Изобретение относится к импульсной технике и может быть использовано в вычислительной технике и системах управления.

Известно счетное устройство, сохраняющее информацию при перерывах питания [1] содержащее линию задержки, элемент памяти в виде основного запоминающего трансформатора, входящего в однотипные счетные ячейки, соединенные последовательно, элемент И-НЕ, а в каждой счетной ячейке сумматор и вспомогательный запоминающий трансформатор. Первый вход сумматора подключен к выходной обмотке основного запоминающего трансформатора, а второй вход к адресному входу устройства. Обмотка записи вспомогательного запоминающего трансформатора подключена к выходу сумматора, а выходная обмотка подключена через диод к обмотке записи основного запоминающего трансформатора. Тактовые обмотки вспомогательных запоминающих трансформаторов включены последовательно между собой и подключены к выходу элемента И-НЕ. Один вход элемента И-НЕ соединен со счетным входом устройства, другой вход с входом установки "0", третий вход с выходом линии задержки, вход которой соединен со счетным входом устройства. Выход переноса сумматора предыдущей ячейки соединен с входом переноса последующей ячейки.

Недостатком данного счетного устройства является низкая достоверность функционирования, что связано с отсутствием контроля функционирования.

Известен счетчик импульсов, сохраняющий информацию при перерывах питания [2] который является прототипом изобретения и содержит блок управления и n счетных ячеек, каждая из которых содержит сердечник с прямоугольной петлей гистерезиса и обмотками выходной, записи и считывания, четыре логических элемента, четыре резистора, конденсатор и диод. Вход блока управления является счетным входом устройства, первый выход соединен с первым входом каждой счетной ячейки, а второй выход с вторым входом первой счетной ячейки. У каждой i-й счетной ячейки, где i=2, 3,n, второй вход соединен с первым выходом (i-1)-й ячейки, а третий вход с вторым выходом (i-1)-й ячейки. Первый и второй выходы последней счетной ячейки являются соответственно основным и дополнительным выходами устройства. Четвертые входы всех счетных ячеек соединены с входом блока управления и третьим входом первой счетной ячейки. В каждой счетной ячейке первый вход первого логического элемента является первым входом ячейки, выход второго логического элемента соединен через первый резистор с началом обмотки записи сердечника, первый вход с выходом четвертого логического элемента, а второй вход с первым выходом ячейки. Первый вход четвертого логического элемента является вторым входом счетной ячейки, третьим входом которой является первый вход третьего логического элемента. При этом конец выходной обмотки сердечника соединен с выводом второго резистора, другой вывод которого соединен с вторым входом первого логического элемента и через третий резистор с катодом диода, анод которого соединен с началом выходной обмотки сердечника, которое является вторым выходом счетной ячейки. При этом конец выходной обмотки сердечника соединен с общей шиной и через конденсатор с вторым входом первого логического элемента, выход которого является первым выходом счетной ячейки, четвертым входом которой является второй вход третьего логического элемента, выход которого через четвертый резистор соединен с концом обмотки считывания сердечника, начало которой соединено с шиной питания и концом обмотки записи сердечника. В каждой счетной ячейке первый, второй и третий логические элементы выполнены в виде элементов И-НЕ, а четвертый логический элемент в виде инвертора.

Блок управления содержит инвертор и элемент задержки, вход которого является входом блока управления, а выход соединен с входом инвертора и является первым выходом блока управления, вторым выходом которого является выход инвертора.

Недостатком данного устройства является низкая достоверность функционирования, что связано с отсутствием контроля функционирования.

Техническим результатом изобретения является повышение достоверности функционирования.

Указанный технический результат достигается тем, что в счетчик импульсов, сохраняющий информацию при перерывах питания, содержащий блок управления и n счетчик ячеек, каждая из которых содержит сердечник с прямоугольной петлей гистерезиса и обмотками выходной и записи, четыре логических элемента и два резистора, при этом первый вход блока управления является счетным входом устройства, первый выход соединен с первым входом каждой счетной ячейки, а второй выход с вторым входом первой счетной ячейки, второй вход каждой i-й счетной ячейки, где i=2, 3,n, соединен с первым выходом (i-1)-й ячейки, а третий вход с вторым выходом (i-1)-й ячейки, первый и второй выходы n-й счетной ячейки являются соответственно основным и дополнительным выходами устройства, четвертые входы всех счетных ячеек объединены, в каждой счетной ячейке первый вход первого логического элемента является первым входом ячейки, выход второго логического элемента соединен через первый резистор с началом обмотки записи сердечники, а первый вход с выходом четвертого логического элемента, вход которого является вторым входом счетной ячейки, третьим входом которой является первый вход третьего логического элемента, конец выходной обмотки сердечника соединен с выводом второго резистора, введены блок анализа четности, контрольный сердечник с прямоугольной петлей гистерезиса и обмоткой, два элемента И-НЕ с открытыми стоками (коллекторами), резистор и блок формирования сигнала ошибки, а в каждую счетную ячейку введены RS-триггер, причем инверсный и прямой выходы блока анализа четности соединены с первыми входами соответственно первого и второго элементов И-НЕ и соответственно с третьим и пятым входами первой счетной ячейки, n входов соединены с вторыми выходами соответствующих счетных ячеек, а (n+1)-й вход соединен с входом управления реверсом, пятый вход каждой (i-й счетной ячейки (где i=2,3,n) соединен с третьим выходом (i-1)-й счетной ячейки, второй вход блока управления соединен с шиной начальной установки, третий выход соединен с четвертыми входами счетных ячеек, четвертый выход с вторыми входами элементов И-НЕ, а пятый выход с выходом второго элемента И-НЕ, с первым входом блока формирования сигнала ошибки и через обмотку контрольного сердечника с выходом первого элемента И-НЕ и вторым входом блока формирования сигнала ошибки, третий вход которого соединен с вторым выходом блока управления, а выход является контрольным выходом устройства, средняя точка обмотки контрольного сердечника через резистор соединена с шиной питания, в каждой счетной ячейке R-вход RS-триггера является четвертым входом ячейки, S-вход соединен с другим выводом второго резистора, прямой выход соединен с вторым входом второго логического элемента и является вторым выходом ячейки, а инверсный выход является третьим выходом ячейки, начало выходной обмотки сердечника соединено с общей шиной, а конец обмотки записи с выходом первого логического элемента, второй вход которого соединен с выходом второго логического элемента, выход третьего логического элемента является первым выходом счетной ячейки, а второй вход соединен с первым входом четвертого логического элемента, второй вход которого является пятым входом счетной ячейки, первый и четвертый логические элементы выполнены в виде элементов ИЛИ-НЕ, второй логический элемент в виде элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а третий логический элемент в виде элемента ИЛИ.

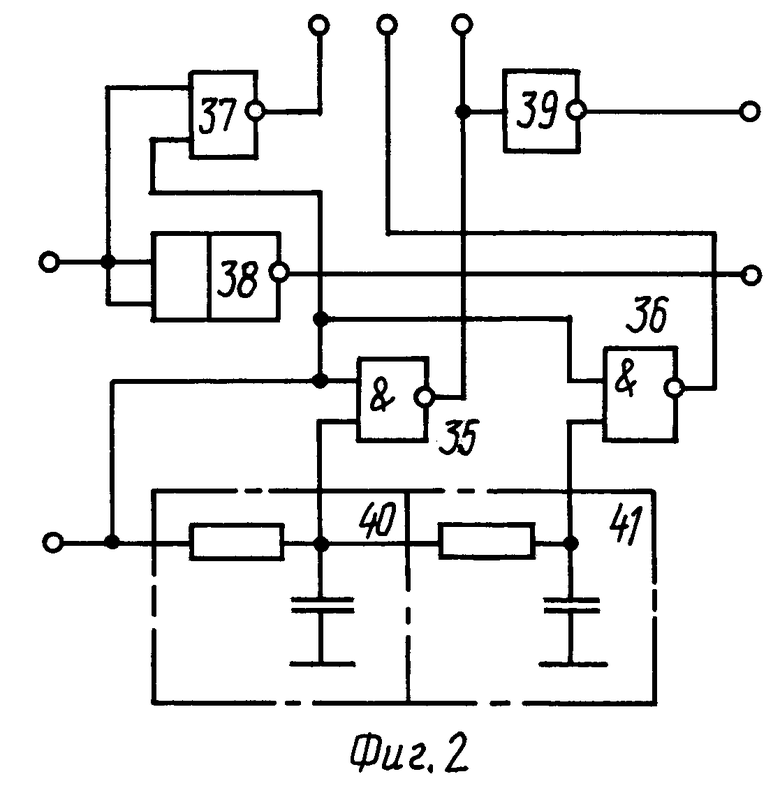

Кроме того, блок управления содержит два элемента И-НЕ, элемент ИЛИ-НЕ, два инвертора и два элемента задержки, вход первого из которых является первым входом блока управления и соединен с первыми входами элементов И-НЕ и элемента ИЛИ-НЕ, второй вход которого является вторым входом блока управления, и соединен с входом первого инвертора, а выход является первым выходом блока управления, выход первого элемента задержки соединен с вторым входом первого элемента И-НЕ и входом второго элемента задержки, выход которого соединен с вторым входом второго элемента И-НЕ, выход которого является вторым выходом блока управления, третьим, четвертым и пятым выходами которого являются выходы соответственно первого элемента И-НЕ, второго и первого инверторов, вход второго инвертора соединен с выходом первого элемента И-НЕ, элементы задержки выполнены в виде интегрирующих RC-цепей, а первый инвертор имеет выход с открытым стоком (коллектором).

Кроме того, блок формирования сигнала ошибки содержит два двунаправленных ключа, два конденсатора, два резистора, элемент ИЛИ-НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с первым информационным входом первого двунаправленного ключа и через последовательно соединенные первые резистор и конденсатор с общей шиной, второй вход с первым информационным входом второго двунаправленного ключа и через последовательно соединенные вторые резистор и конденсатор с общей шиной, а выход соединен с первым входом элемента ИЛИ-НЕ, выход которого является выходом блока формирования сигнала ошибки, первым и вторым входами которого являются управляющие входы соответственно первого и второго двунаправленных ключей, а третьим входом является второй вход элемента ИЛИ-НЕ, соединенный с вторыми информационными входами двунаправленных ключей.

Указанная совокупность признаков позволяет повысить достоверность функционирования счетчика импульсов путем обеспечения контроля функционирования.

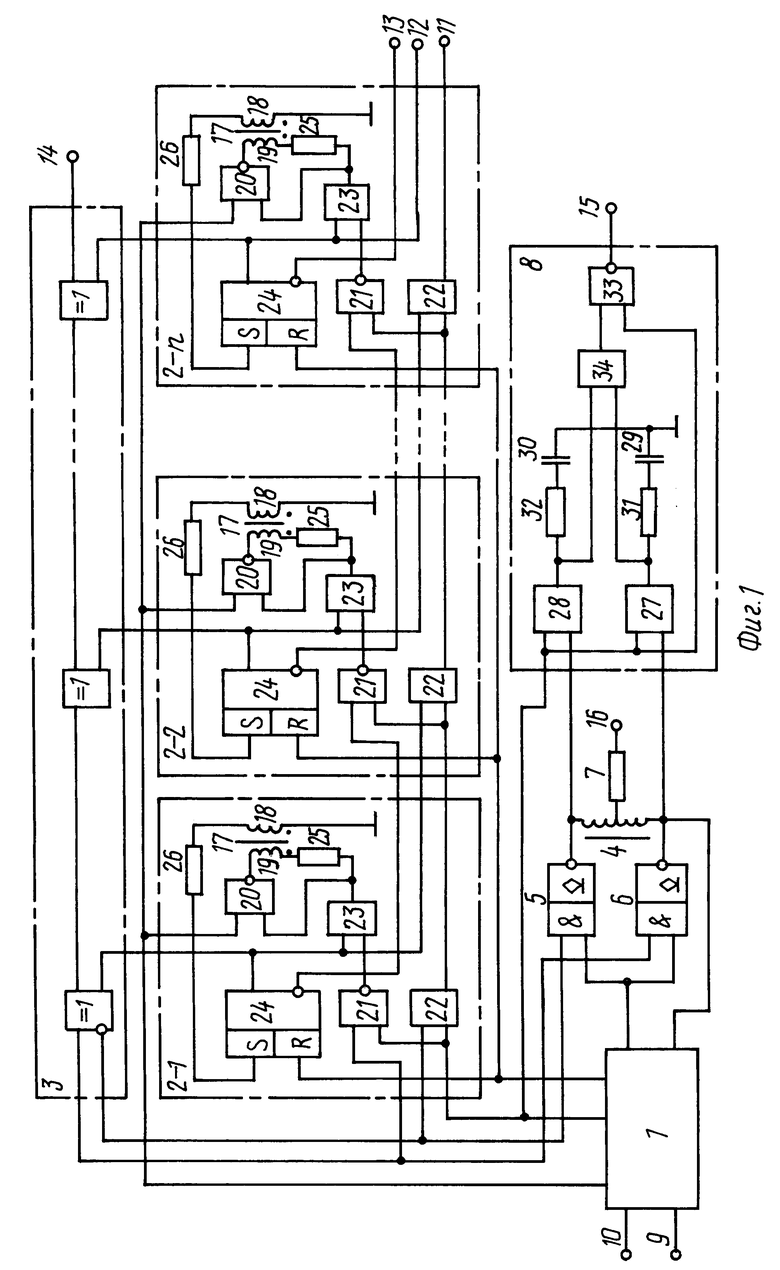

На фиг. 1 приведена схема счетчика импульсов, сохраняющего информацию при перерывах напряжения питания; на фиг. 2 схема блока управления.

Счетчик импульсов, сохраняющий информацию при перерывах питания, содержит блок управления 1, n счетчик ячеек 2-1, 2-2, 2-n, блок 3 анализа четности, контрольный сердечник 4, первый 5 и второй 6 элементы И-НЕ, резистор 7, блок 8 формирования сигнала ошибки, счетный вход 9, шину 10 начальной установки, основной выход 11, первый 12 и второй 13 дополнительные выходы, вход 14 управления реверсом, контрольный выход 15 и шину питания 16. Каждая из ячеек 2-1, 2-2,2-n содержит сердечник 17 с прямоугольной петлей гистерезиза и обмотками выходной 18 и записи 19, первый 20 и второй 21 элементы ИЛИ-НЕ, элемент ИЛИ 22, элемент 23 ИСКЛЮЧАЮЩЕЕ ИЛИ, RS-триггер 24, первый 25 и второй 26 резисторы.

Первый вход блока 1 управления является счетным входом 9 устройства, второй вход соединен с шиной 10 начальной установки, первый выход соединен с первым входом каждой счетной ячейки 2-1, 2-2,2-n, а второй выход с вторым входом первой счетной ячейки 2-1. У каждой счетной ячейки 2-i, где i-2, 3,n, второй и третий входы соединены соответственно с первым и вторым выходами ячейки 2-(i-1), четвертый вход соединен с четвертым входом ячейки 2-1 и третьим выходом блока 1 управления, а пятый вход с третьим выходом ячейки 2-(i-1). Первый, второй и третий выходы ячейки 2-n являются соответственно основным 11, первым дополнительным 12 и вторым дополнительным 13 выходами устройства. Прямой и инверсный выходы блока 3 анализа четности соединены с первыми входами соответственно второго 6 и первого 5 элементов И-НЕ и соответственно с пятым и третьим входами счетной ячейки 2-1, n входов соединены с вторыми выходами соответствующих счетных ячеек 2-1, 2-2, 2-n, а (n+1)-й вход соединен с входом 14 управления реверсом. Четвертый выход блока 1 управления соединен с вторыми входами элементов 5 и 6 И-НЕ, а пятый выход с выходом элемента И-НЕ 6, который соединен с первым входом блока 8 формирования сигнала ошибки и через обмотку контрольного сердечника 4 с выходом элемента И-НЕ 5 и вторым входом блока 8 формирования сигнала ошибки, третий вход которого соединен с вторым выходом блока 1 управления, а выход является контрольным выходом 15 устройства. Средняя точка обмотки контрольного сердечника 4 через резистор 7 соединена с шиной 16 питания.

В каждой счетной ячейке 2-1, 2-2,2-n первый вход элемента ИЛИ-НЕ 20 является первым входом ячейки, второй вход соединен с выходом элемента 23 ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход с концом обмотки 19 записи сердечника 17, начало которой через резистор 25 соединено с выходом элемента 23 ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом элемента ИЛИ-НЕ 21, а второй вход соединен с прямым выходом RS-триггера 24, являющимся вторым выходом счетной ячейки. Первые входы элементов ИЛИ-НЕ 21 и ИЛИ 22 объединены и являются вторым входом счетной ячейки, третьим и пятым входами которой являются вторые входы элементов соответственно ИЛИ 22 и ИЛИ-НЕ 21. Выход элемента ИЛИ 22 является первым выходом счетной ячейки, третьим выходом которой является инверсный выход RS-триггера 24, S-вход которого через резистор 26 соединен с концом выходной обмотки 18 сердечника 17, а R-вход является четвертым входом счетной ячейки. Начало выходной обмотки 18 сердечника 17 каждой ячейки 2-1, 2-2,2n соединено с общей шиной.

Блок 8 формирования сигнала ошибки содержит два двунаправленных ключа 27 и 28, два конденсатора 29 и 30, два резистора 31 и 32, элемент ИЛИ-НЕ 33 и элемент 34 ИСКЛЮЧАЮЩЕЕ ИЛИ. Первый вход элемента 34 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым информационным входом первого двунаправленного ключа 27 и через последовательно соединенные первые резистор 31 и конденсатор 29 с общей шиной, второй вход с первым информационным входом второго двунаправленного ключа 28 и через последовательно соединенные второй резистор 32 и конденсатор 30 с общей шиной. Выход элемента 34 ИСКЛЮЧАЮЩЕЕ-ИЛИ соединен с первым входом элемента ИЛИ-НЕ 33, выход которого является выходом блока 8 формирования сигнала ошибки, первым и вторым входами которого являются управляющие входы соответственно первого 27 и второго 28 двунаправленных ключей, а третьим входом является второй вход элемента ИЛИ-НЕ 33 соединенный с вторыми информационными входами двунаправленных ключей 27 и 28.

Блок 1 управления содержит элементы И-НЕ 35 и 36, элемент ИЛИ-НЕ 37, инверторы 38 и 39 и два элемента 40 и 41 задержки. Вход первого элемента 40 задержки является первым входом блока 1 управления и соединен с первыми входами элементов И-НЕ 35 и 36 и элемента ИЛИ-НЕ 37, второй вход которого является вторым входом блока 1 управления и соединен с входом первого инвертора 38, а выход является первым выходом блока 1 управления. Выход первого элемента 40 задержки соединен с вторым входом второго элемента 41 задержки, выход которого соединен с вторым входом второго элемента И-НЕ 36, выход которого является вторым выходом блока 1 управления, Третьим, четвертым и пятым выходами блока 1 управления являются выходы соответственно первого элемента И-НЕ 35, второго 39 и первого 38 инверторов. Вход второго инвертора 39 соединен с выходом первого элемента И-НЕ 35, второй вход которого соединен с выходом первого элемента 40 задержки. Первый инвертор 38 имеет выход с открытым стоком (коллектором).

Счетчик импульсов, сохраняющий информацию при перерывах питания, работает следующим образом. В исходное состояние счетчик устанавливается импульсом, поступающим по шине 10 начальной установки. При этом триггер 24 в каждой счетной ячейке 2-1, 2-2,2-n принудительно удерживается в нулевом состоянии, и уровень логического "0" с выхода указанного триггера поступает на первый вход элемента 23, на второй вход которого поступает уровень логического "0" с выхода элемента 21. На выходе элемента 23 присутствует уровень логического "0", поступающий на вход элемента 20, на другой вход которого поступает уровень логического "0" с первого выхода блока 1 управления, а на выходе появляется уровень логической "1". Магнитный сердечник 17 перемагничивается в нулевое состояние током, протекающим с выхода элемента 20 через обмотку 19 записи, резистор 25 на выход элемента 23. В это время на пятом выходе блока 1 управления присутствует уровень логического "0", и контрольный сердечник 4 перемегничивается в единичное состояние током, протекающим с шины 16 питания через резистор 7, обмотку контрольного сердечника 4 на пятый выход блока 1 управления.

После окончания импульса на шине 10 начальной установки начинают поступать счетные импульсы по счетному входу 9. В паузе между импульсом начальной установки и первым счетным импульсом (а также между последующими счетными импульсами) на выходах элементов 5 и 6 присутствуют уровни логической "1", удерживающие двунаправленные ключи 27 и 28 в открытом состоянии. Конденсаторы 29 и 30 через резисторы 31 и 32 и двунаправленные ключи 27 и 28 заряжаются до уровня логической "1", присутствующего на втором выходе блока 1 управления. На шине 14 управления реверсом присутствует уровень логического "0", поэтому счетчик импульсов работает в прямом режиме (режиме сложения счетных импульсов) в соответствии с кодом Грея.

По фронту первого счетного импульса на первом выходе блока 1 управления появляется уровень логического "0", и, как было описано выше, сердечник 17 в каждой счетной ячейке начинает перемагничиваться в нулевое состояние. Так как в каждой ячейке указанный сердечник установлен в нулевое состояние импульсом начальной установки, то на конце его обмотки 18 считывания и на S-входе триггера 24 появится лишь короткий (1 мкс) импульс помехи, связанный с непрямоугольностью петли гистерезиса магнитного сердечника. Триггер 24 при этом своего состояния не изменит, так как продолжает принудительно удерживаться в нулевом состоянии по R-входу. С задержкой, определяемой элементом 40 задержки, на R-входах триггеров 24 появится уровень логического "0". Так как время указанной задержки (5 мкс) превышает длительность импульса помехи (1 мкс), связанной с прямоугольностью петли гистерезиса, то к этому времени на S-входах триггеров 24 будут присутствовать уровни логического "0", и триггеры своего нулевого состояния не изменяет. Следовательно, на инверсном выходе блока 3 анализа четности будет присутствовать уровень логической "1", который поступает на первый вход элемента И-НЕ 5, на втором входе которого присутствует уровень логической "1", который поступает с четвертого выхода блока 1 управления одновременно с уровнем логического "0", на втором выходе блока 1 управления. В результате на выходе элемента И-НЕ 5 появится уровень логического "0", и контрольный сердечник 4 начнет перемагничиваться в нулевое состояние током, протекающим с шины 16 питания через резистор 7, обмотку контрольного сердечника 4 на выход элемента И-НЕ 5. Уровень логического "0" на выходе элемента И-НЕ 5 закроет двунаправленный ключ 28. На другом конце обмотки сердечника 4 на время его перемагничивания (около 20 мкс) сохранится уровень логической "1", и двунаправленный ключ 27 останется открытым. С задержкой (5 мкс), определяемой вторым элементом 40 задержки, на втором выходе блока 1 управления появляется уровень логического "0", который проходит через дву- направленный ключ 27 и разряжает конденсатор 29 через резистор 31. При этом на одном из входов элемента 33 ИЛИ-НЕ уровень логической "1" исчезает, а на другом входе появится, и на контрольном выходе 15 сохранится уровень логического "0", что свидетельствует о нормальном функционировании счетчика импульсов.

Одновременно уровень логического "0" с второго выхода блока 1 управления поступает на входы элементов 21 и 22 счетной ячейки 2-1. Элемент 22 в это время закрыт, так как на его другой вход поступает уровень логической "1" с инверсного выхода блока 3 анализа четности, а элемент 21 открыт, так как на его другой вход поступает уровень логического "0" с прямого выхода блока 3 анализа четности. Поэтому, в соответствии с кодом Грея, первым счетным импульсом переключается первая счетная ячейка 2-1, переключение которой заключается в перемагничивании сердечника 17 в единичное состояние. По окончании первого счетного импульса на счетном входе 9 триггера 24 всех счетных ячеек устанавливаются в нулевое состояние, обмотки всех сердечников 17 обесточиваются, конденсаторы 29 и 30 заряжаются до уровня логической "1".

По фронту второго счетного импульса на первом выходе блока 1 управления появляется уровень логического "0", и сердечники 17 всех счетных ячеек 2-1, 2-2,2-n начинают перемагничиваться в нулевое состояние. На конце выходной обмотки 18 сердечника 17 первой счетной ячейки 2-1 появится импульс уровня логической "1" (длительность которого, если не прерывать процесс перемагничивания указанного сердечника, 20 мкс), а на концах выходных обмоток 18 сердечников 17 остальных счетных ячеек 2-2,2-n появятся импульсы помех (длительностью 1 мкс). Через 5 мкс на R-входах триггеров 24 всех счетных ячеек 2-1,2-2,2-n появится уровень логического "0". К этому времени на S-входе триггера 24 первой счетной ячейки 2-1 будет присутствовать уровень логической "1", и он переключится в единичное состояние, а на S-входах триггеров 24 остальных счетных ячеек 2-2,2-n будут присутствовать уровни логического "0", и они сохранят нулевое состояние. Следовательно, на прямом выходе блока 3 анализа четности появится уровень логической "1", который поступает на вход элемента И-НЕ 6, на втором входе которого присутствует уровень логической "1", поступающий с четвертого выхода блока 1 управления одновременно с уровнем логического "0" на третьем выходе блока 1 управления. В результате на выходе элемента И-НЕ 6 появится уровень логического "0", и контрольный сердечник 4 начнет перемагничиваться в единичное состояние током, протекающим с шины 16 питания через резистор 7, обмотку контрольного сердечника 4 на вход элемента И-НЕ 6. Уровень логического "0" на выходе элемента И-НЕ 6 закроет двунаправленный ключ 27. На другом конце обмотки сердечника 4 на время его перемагничивания (около 20 мкс) сохранится уровень логической "1", и двунаправленный ключ 28 останется открытым. С задержкой (5 мкс), определяемой элементом 41 задержки, на втором выходе блока 1 управления появляется уровень логического "0", который проходит через двунаправленный ключ 28 и разряжает конденсатор 30 через резистор 32. При этом на одном из входов элемента ИЛИ-НЕ 33 уровень логической "1" исчезает, а на другом входе появится, и на контрольном выходе 15 сохранится уровень логического "0", что свидетельствует о нормальном функционировании счетчика импульсов.

Одновременно уровень логического "0" с второго выхода блока 1 управления поступает на входы элементов 21 и 22 первой счетной ячейки 2-1. Элемент 21 в это время закрыт, так как на его другой вход поступает уровень логической "1" с прямого выхода блока 3 анализа четности, а элемент 22 открыт, так как на его другой вход поступает уровень логического "0" с инверсного выхода блока 3 анализа четности. Уровень логического "0" через элемент 22 счетной ячейки 2-1 поступает на входы элементов 21 и 22 второй счетной ячейки 2-2, на других входах которых присутствуют соответственно уровень логического "0" и уровень логической "1", поступающие соответственно с инверсного и прямого выходов триггера 24 счетной ячейки 2-1. Поэтому, в соответствии с кодом Грея, вторым счетным импульсом переключается счетная ячейка 2-2, переключение которой заключается в перемагничивании сердечника 17 в единичное состояние. По окончании второго счетного импульса на счетном входе 9 триггеры 24 всех счетных ячеек устанавливаются в нулевое состояние, обмотки всех сердечников 17 обесточиваются, конденсаторы 29 и 30 заряжаются до уровня логической "1".

Последующие счетные импульсы переключают счетчик в соответствии с кодом Грея. При этом работа счетчика во время каждого нечетного счетного импульса аналогична его работе во время первого счетного импульса, а во время каждого нечетного счетного импульса аналогична его работе во время первого счетного импульса, а во время каждого четного счетного импульса аналогична его работе во время второго счетного импульса. Таким образом, во время каждого счетного импульса контрольный сердечник полностью перемагничивается в противоположное состояние, так как при нормальной работе счетчика четность кода его состояния изменяется каждым счетным импульсом. После переполнения счетчика на его основном выходе 11 появляется импульс, свидетельствующий о том, что счетчик переполнен. Если после этого импульса изменить сигнал на входе 14 управления реверсом с логического "0" на логическую "1", счетчик может продолжать работу, но уже в реверсном режиме (режиме вычитания счетных импульсов). Выходы 11, 12 и 13 счетчика импульсов и его вход 14 могут быть использованы для наращивания числа разрядов счетчика путем подключения необходимого количества однотипных счетных ячеек.

Если в результате сбоя или отказа элементов счетчика переключения соответствующей счетной ячейки в течение текущего счетного импульса не произойдет, то во время следующего счетного импульса на выходах блока 3 анализа четности сигналы не изменятся, контрольный сердечник 4 перемагничиваться не будет, к моменту появления уровня логического "0" на втором выходе блока 1 управления двунаправленные ключи 27 и 28 будут закрытыми, конденсаторы 29 и 30 сохранят заряженное состояние, и на контрольном выходе 15 появится импульс, являющийся сигналом ошибки, свидетельствующим о неправильном функционировании счетчика. Длительность этого импульса определяется длительностью счетного импульса.

Если во время счетного импульса после переключения одной из счетных ячеек произойдет ее повторное переключение или переключение других счетных ячеек, то сигналы на выходах блока 3 анализа четности при этом будут изменяться при каждом переключении, что приведет к поочередному появлению уровней логического "0" на выходах элементов И-НЕ 5 и 6 и поочередному открыванию двунаправленных ключей 27 и 28. В результате разрядятся оба конденсатора 29 и 30, и на контрольном выходе 15 появится импульс, являющийся сигналом ошибки, свидетельствующим о неправильном функционировании счетчика.

Таким образом, достоверность функционирования счетчика импульсов, сохраняющего информацию при перерывах питания, обеспечивается путем контроля его функционирования с помощью схемы контроля (элементы 4-7,27-33), также сохраняющей информацию при перерывах питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207718C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207717C2 |

| ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2038692C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 1992 |

|

RU2040113C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2036547C1 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1999 |

|

RU2152685C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2110146C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2042268C1 |

Использование: изобретение относится к импульсной технике и позволяет повысить достоверность функционирования. Устройство содержит блок управления, n счетных ячеек, блок анализа четности, контрольный сердечник, два элемента И НЕ, резистор, блок формирования сигнала ошибки, счетный вход, шину начальной установки, выход, контрольный выход. Каждая из счетных ячеек содержит сердечник с прямоугольной петлей гистерезиса и двумя обмотками выходной и записи, два элемента ИЛИ НЕ, элемент ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, RS-триггер, два резистора. 2 з. п. ф-лы, 2 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Счетчик импульсов, сохраняющий информацию при перерывах питания | 1985 |

|

SU1633490A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-10-27—Публикация

1991-11-18—Подача