Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известно счетное устройство [1] содержащее инвертор, элемент задержки и последовательно соединенные счетные ячейки. Каждая счетная ячейка содержит элемент памяти на ферритовом сердечнике с прямоугольной петлей гистерезиса и обмотками выходной, записи и считывания, четыре логических элемента, четыре резистора, конденсатор и диод. Вход элемента задержки подключен к входу устройства, а выход к третьим входам всех счетных ячеек. У первой счетной ячейки четвертый вход объединен с вторым входом и подключен к входу устройства, а ее первый вход соединен с выходом инвертора. У каждой i-й счетной ячейки, где i 2, 3, n, первый вход соединен с первым выходом (i-1)-й ячейки, второй вход соединен с вторым выходом предыдущей ячейки.

Третьи входы всех счетных ячеек подключены к входу инвертора, а четвертые входы объединены и подключены к входу устройства. Первый выход n-й счетной ячейки подключен к основному, а второй к дополнительному выходам устройства. В каждой счетной ячейке анод диода соединен с началом выходной обмотки и вторым выходом этой счетной ячейки, а катод через последовательно соединенные первый резистор и конденсатор соединен с концом выходной обмотки, соединенным также с общей шиной питания.

Второй резистор подключен параллельно конденсатору. Точка соединения первого и второго резисторов и конденсатора подсоединена к второму входу первого логического элемента, выход которого, являясь одновременно и первым выходом счетной ячейки, соединен с первым входом второго логического элемента. Первый вход первого логического элемента соединен с третьим входом счетной ячейки. Выход второго логического элемента через третий резистор соединен с началом обмотки записи, конец которой соединен с началом обмотки считывания и с шиной питания. Второй вход второго логического элемента соединен с выходом четвертого логического элемента, вход которого соединен с первым входом счетной ячейки. Второй вход счетной ячейки соединен с первым входом третьего логического элемента, выход которого через четвертый резистор соединен с концом обмотки считывания, а второй вход с четвертым входом счетной ячейки. Первый, второй и третий логические элементы выполнены в виде элементов И-НЕ, а четвертый в виде инвертора.

Наличие в данном счетном устройстве только одного канала не позволяет производить независимый счет импульсов, поступающих от двух разных источников.

Известно счетное устройство [2] содержащее формирователь импульсов (линию задержки), элемент И-НЕ, N разрядов (счетных ячеек), счетный вход, вход начальной установки и N адресных входов. Каждый разряд содержит две ячейки памяти в виде запоминающих трансформаторов с тактовым входом (тактовой обмоткой), информационным входом (обмоткой записи) и выходом (выходной обмоткой), логический элемент, выполненный в виде одноразрядного сумматора, и диод. Первый вход элемента И-НЕ является входом начальной установки устройства, второй вход счетным входом устройства, а третий вход соединен с выходом формирователя импульсов, вход которого подключен к счетному входу устройства. Тактовые входы первых ячеек памяти всех разрядов объединены и подключены к выходу элемента И-НЕ, а тактовые входы вторых ячеек памяти объединены и подключены к счетному входу устройства. В каждом разряде первый вход логического элемента соединен с соответствующим адресным входом устройства, второй вход с выходом второй ячейки памяти, а выход с информационным входом первой ячейки памяти, выход которой через диод подключен к информационному входу второй ячейки памяти.

Наличие в данном счетном устройстве только одного канала не позволяет производить независимый счет импульсов, поступающих от двух разных источников.

Целью изобретения является расширение функциональных возможностей путем обеспечения счета импульсов по двум независимым каналам.

Цель достигается тем, что в счетное устройство, содержащее первый счетный вход, вход начальной установки, первый элемент И-НЕ, первый формирователь и N разрядов, каждый из которых содержит две ячейки памяти и логический элемент, первый и второй входы элемента И-НЕ являются соответственно первым счетным входом и входом начальной установки устройства, тактовые входы первых ячеек памяти всех разрядов объединены и подключены к выходу элемента И-НЕ, тактовые входы вторых ячеек памяти всех разрядов объединены, в каждом разряде выход второй ячейки памяти соединен с одним входом логического элемента, введены второй счетный вход устройства, второй формирователь импульсов, второй и третий элементы И-НЕ, N-разрядный счетчик импульсов, два дешифратора и два выхода устройства, первый вход второго элемента И-НЕ соединен с входом начальной установки, второй вход с вторым счетным входом устройства, а выход с тактовыми входами вторых ячеек памяти разрядов, счетные входы устройства соединены с соответствующими входами третьего элемента И-НЕ, выход которого подключен к входу первого формирователя импульсов, выход которого соединен с входом обнуления счетчика и входом второго формирователя импульсов, выход которого соединен со счетным входом счетчика, тактовые входы первого и второго дешифраторов соединены с выходами соответствующих элементов И-НЕ, информационные входы с соответствующими выходами разрядов счетчика импульсов, а выходы являются соответствующими выходами счетного устройства, прямой выход каждого разряда счетчика импульсов соединен с информационными входами первой и второй ячеек памяти соответствующего разряда устройства, в каждом разряде которого второй вход логического элемента соединен с выходом первой ячейки памяти, а выход с входом установки соответствующего разряда счетчика импульсов, при этом логические элементы разрядов устройства выполнены в виде элементов И-НЕ. Кроме того, каждая ячейка памяти содержит первый и второй элементы И-НЕ с открытым стоком (коллектором), инвертор, магнитный сердечник с прямоугольной петлей гистерезиса и обмоткой и два резистора, причем тактовый вход ячейки памяти соединен с первыми входами элементов И-НЕ, информационный вход с вторым входом первого элемента И-НЕ и через инвертор с вторым входом второго элемента И-НЕ, выход которого через обмотку сердечника соединен с выходом первого элемента И-НЕ, который через первый резистор соединен с выходом ячейки памяти, средняя точка обмотки сердечника через второй резистор соединена с шиной питания. Кроме того, счетчик импульсов в каждом разряде содержит триггер и элемент ИЛИ-НЕ, первый вход которого является входом установки данного разряда, а выход соединен с S-входом триггера данного разряда, R-входы триггеров всех разрядов объединены между собой и с вторыми входами элементов ИЛИ-НЕ и соединены с входом обнуления счетчика импульсов, счетный вход которого соединен со счетным входом триггера первого разряда и с третьим входом элемента ИЛИ-НЕ каждого разряда, счетный вход триггера каждого разряда, кроме первого, соединен с инверсным выходом триггера предыдущего разряда, прямой выход триггера каждого разряда является выходом данного разряда.

Указанная совокупность признаков позволяет обеспечить работу по двум независимым каналам путем их временного разделения за счет разнесенного во времени опроса первых и вторых ячеек памяти с соответствующим изменением записанной в них информации с помощью общего счетчика импульсов.

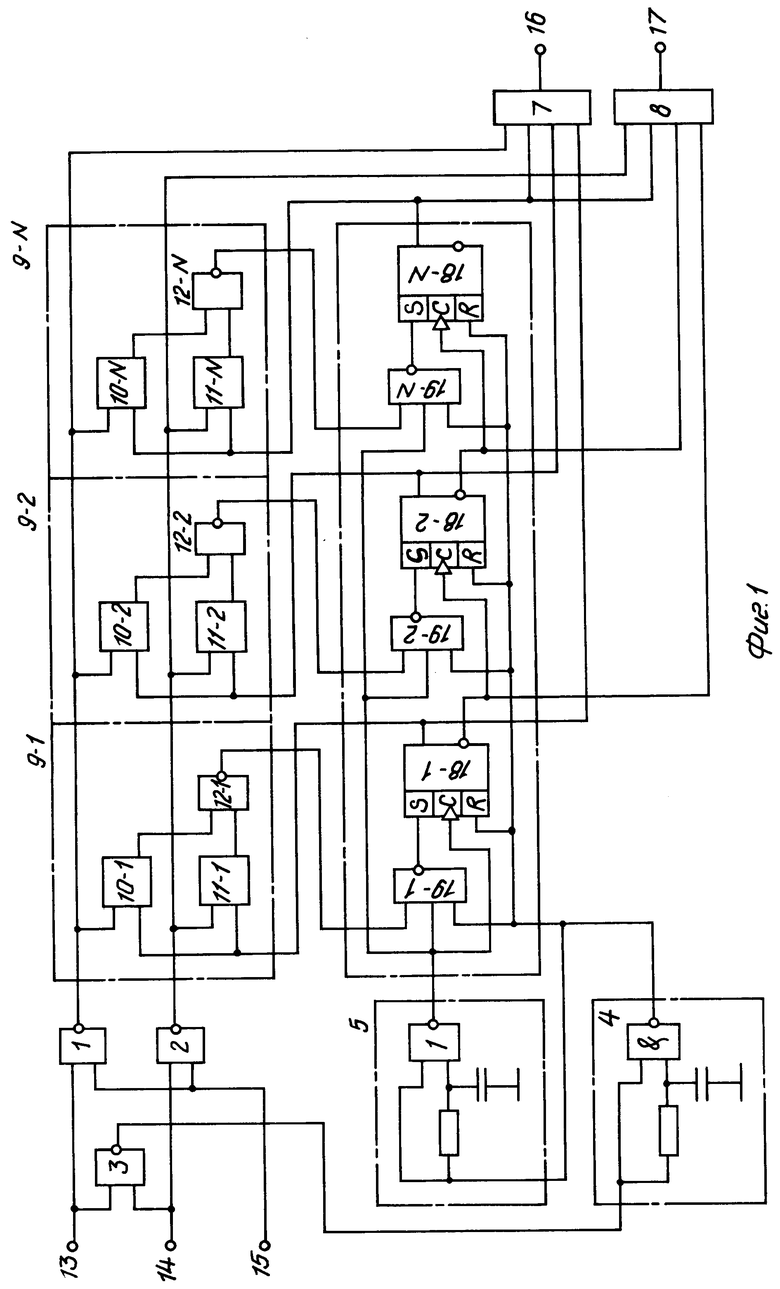

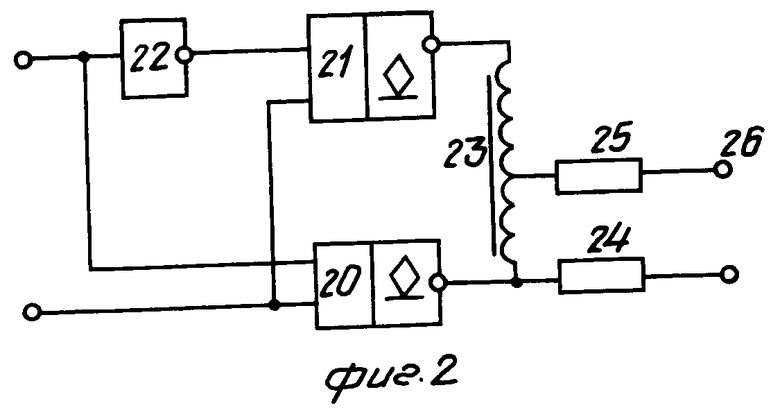

На фиг.1 приведена схема счетного устройства; на фиг.2 схема ячейки памяти.

Счетное устройство (см. фиг.1) содержит три элемента И-НЕ 1-3, два формирователя 4, 5 импульсов, счетчик 6 импульсов, два дешифратора 7, 8 и N разрядов 9-1, 9-2, 9-N, каждый из которых содержит две ячейки 10-i, 11-i памяти и элемент И-НЕ 12-i (где i 1, 2, N). Счетное устройство имеет два счетных входа 13, 14, вход 15 начальной установки и два выхода 16, 17.

Первый и второй входы элемента И-НЕ 1 являются соответственно первым счетным входом 13 и входом 15 начальной установки устройства, первый вход элемента И-НЕ 2 является вторым счетным входом 14 устройства, а второй вход соединен с вторым входом элемента И-НЕ 1. Первые входы элементов И-НЕ 1 и 2 соединены с соответствующими входами элемента И-НЕ 3, выход которого соединен через первый формирователь 4 импульсов с входом обнуления счетчика 6, который через второй формирователь 5 импульсов соединен со счетным входом счетчика 6. В каждом разряде 9-1, 9-2, 9-N входы элемента И-НЕ 12-i соединены с выходами соответствующих ячеек 10-i, 11-i памяти, информационные входы которых объединены и подключены к выходу соответствующего разряда счетчика 6 импульсов, а тактовые входы подключены к выходам соответственно первого 1 и второго 2 элементов И-НЕ и к тактовым входам соответственно первого 7 и второго 8 дешифраторов. Информационные входы дешифраторов 7 и 8 соединены с соответствующими выходами разрядов счетчика 6, а выходы являются соответственно первым 16 и вторым 17 выходами устройства.

Счетчик 6 импульсов в каждом разряде содержит триггер 18-i и элемент ИЛИ-НЕ 19-i (где i 1, 2, N). Первый вход элемента ИЛИ-НЕ 19-i каждого разряда счетчика 6 является входом установки данного разряда, а выход соединен с S-входом триггера 18-i данного разряда. R-входы триггеров 18-1, 18-2, 18-N всех разрядов объединены между собой и с вторыми входами элементов ИЛИ-НЕ 19-1, 19-2, 19-N всех разрядов и соединены с входом обнуления счетчика 6 импульсов. Счетный вход счетчика 6 импульсов соединен со счетным входом триггера 18-1 первого разряда и с третьим входом каждого элемента ИЛИ-НЕ 19-1, 19-2, 19-N. Счетный вход триггера 18-j каждого разряда, кроме первого (j 2, N), соединен с инверсным выходом триггера 18-(j-1) предыдущего разряда. Прямой выход триггера 18-i каждого разряда является выходом данного разряда.

Каждая ячейка 10-1, 10-2, 10-N, 11-1, 11-2, 11-N памяти (см. фиг.2) содержит первый 20 и второй 21 элементы И-НЕ с открытым стоком (коллектором), инвертор 22, магнитный сердечник 23 с прямоугольной петлей гистерезиса и обмоткой и два резистора 24, 25. Тактовый вход ячейки памяти соединен с первыми входами элементов И-НЕ 20 и 21, информационный вход с вторым входом первого элемента И-НЕ 20 и через инвертор 22 с вторым входом второго элемента И-НЕ 21, выход которого через обмотку сердечника 23 соединен с выходом первого элемента И-НЕ 20, который через первый резистор 24 соединен с выходом ячейки памяти. Средняя точка обмотки сердечника 23 через второй резистор 25 соединена с шиной 26 питания.

К первому счетному каналу относятся первые ячейки памяти 10-1, 10-2, 10-N, первый элемент И-НЕ 1, первый счетный вход 13, первый дешифратор 7 и первый выход 16. К второму счетному каналу относятся вторые ячейки памяти 11-1, 11-2, 11-N, второй элемент И-НЕ 2, второй счетный вход 14, второй дешифратор 8 и второй выход 17. Остальные элементы устройства являются общими для обоих счетных каналов.

Счетное устройство работает следующим образом.

На вход 15 начальной установки поступает импульс логического "0", который инвертируется элементами И-НЕ 1-2 и поступает на тактовые входы всех ячеек 10-1, 10-N, 11-1, 11-N памяти. На счетных входах 13, 14 в это время присутствуют уровни логической "1", на выходе элемента И-НЕ 3 уровень логического "0", а на выходе формирователя 4 импульсов уровень логической "1", который удерживает счетчик 6 импульсов в нулевом состоянии. При этом на информационные входы всех ячеек 10-1, 10-N, 11-1, 11-N памяти поступают уровни логического "0" и сердечники 23 указанных ячеек памяти перемагничиваются в нулевое состояние. По окончании импульса начальной установки на счетные входы 13 и 14 начинают поступать счетные импульсы, которые могут иметь различную частоту следования, но должны быть разнесены во времени (так как разделение между счетными каналами устройства временное).

Так как счетные каналы устройства работают одинаково, рассмотрим его работу на примере первого счетного канала.

Первый счетный импульс поступает на счетный вход 13 в виде логического "0" и вызывает появление уровней логической "1" на выходах элементов И-НЕ 1 и 3. Уровень логической "1" с выхода элемента И-НЕ 1 поступает на тактовые входы ячеек 10-1, 10-N памяти первого счетного канала, на информационные входы которых поступают уровни логического "0" с соответствующих разрядов счетчика 6 импульсов, удерживаемого в исходном состоянии уровнем логической "1", поступающим с выхода формирователя 4 импульсов. Магнитные сердечники 23 указанных ячеек памяти перемагничиваются в нулевое состояние. Но, так как они были перемагничены в нулевое состояние во время импульса начальной установки, то на выходах данных ячеек памяти формируются лишь короткие импульсы помех, связанные с непрямоугольностью петли гистерезиса магнитных сердечников 23. Эти импульсы не приводят к переключению разрядов счетчика 6 в единичное состояние, так как они принудительно удерживаются в нулевом состоянии. Через время задержки, которое определяется постоянной времени RC-цепи формирователя 4 и превышает длительность импульса помехи от непрямоугольности петли гистерезиса, на выходе формирователя 4 появляется уровень логического "0" и сигнал установки с входа обнуления счетчика 6 снимается. К этому моменту времени на выходах элементов И-НЕ 12-1, 12-N всех разрядов 9-1, 9-N счетного устройства установлены уровни логической "1" и счетчик 6 импульсов остается в нулевом состоянии. Через время задержки, определяемое постоянной времени RC-цепи формирователя 5, на выходе указанного формирователя появляется импульс логической "1", поступающий на счетный вход счетчика 6 и переключающий его в первое состояние, в котором на выходе его первого разряда появляется уровень логической "1". Это вызывает перемагничивание сердечника 23 ячейки 10-1 памяти в единичное состояние. По окончании первого счетного импульса сигнал с тактовых входов ячеек 10-1, 10-N памяти снимается, обмотки сердечников 23 указанных ячеек памяти обесточиваются, а счетчик 6 импульсов принудительно удерживается в нулевом состоянии.

Второй счетный импульс поступает на счетный вход 13 и вызывает появление уровней логической "1" на выходах элементов И-НЕ 1 и 3. Уровень логической "1" с выхода элемента И-НЕ 1 поступает на тактовые входы ячеек 10-1, 10-N памяти первого счетного канала, на информационные входы которых поступают уровни логического "0" с соответствующих разрядов счетчика 6 импульсов, удерживаемого в исходном состоянии уровнем логической "1", поступающим с выхода формирователя 4 импульсов. Магнитные сердечники 23 указанных ячеек памяти перемагничиваются в нулевое состояние. Так как сердечники 23 ячеек 10-2, 10-N памяти уже намагничены в нулевое состояние, то на выходах указанных ячеек памяти формируются короткие импульсы помех от непрямоугольности петли гистерезиса. Так как сердечник 23 ячейки 10-1 памяти был намагничен в единичное состояние во время предыдущего счетного импульса, то на выходе ячейки 10-1 памяти начнет формироваться импульс, длительность которого, если не прерывать процесс перемагничивания, равнялась бы времени перемагничивания сердечника 23. Через время задержки, определяемое формирователем 4, которое превышает длительность импульса помехи от непрямоугольности петли гистерезиса, но меньше времени перемагничивания сердечника 23, на выходе формирователя 4 появляется уровень логического "0" и сигнал установки с входа обнуления счетчика 6 снимается. К этому моменту времени на выходах элементов И-НЕ 12-2, 12-N разрядов 9-2, 9-N установлены уровни логической "1", а на выходе элемента И-НЕ 12-1 первого разряда 9-1 уровень логического "0". Соответственно первый разряд счетчика 6 установится в единичное состояние, а остальные разряды останутся в нулевом состоянии. Через время задержки, определяемое формирователем 5, на выходе указанного формирователя появляется импульс логической "1", поступающий на счетный вход счетчика 6 и переключающий его во второе состояние в соответствии с прямым двоичным кодом (работа счетчика 6 может быть организована в любом двоичном коде, например в коде Грея, однако в рассматриваемом примере (см. фиг.1) приведена схема счетчика 6, работающего в прямом двоичном коде). Соответствующим образом перемагничиваются сердечники 23 ячеек 10-1 и 10-2 памяти. По окончании второго счетного импульса обмотки всех сердечников 23 устройства обесточиваются, а счетчик 6 импульсов принудительно удерживается в нулевом состоянии.

Далее устройство работает аналогично. Когда счетчик 6 примет состояние, на которое настроен дешифратор 7, на выходе этого дешифратора сформируется выходной импульс первого счетного канала.

Из описания работы видно, что счетное устройство позволяет обеспечить работу по двум независимым каналам путем их временного разделения за счет разнесенного во времени опроса ячеек памяти первого и второго счетных каналов с соответствующим изменением записанной в них информации с помощью общего счетчика импульсов.

В институте изготовлен лабораторный макет помехоустойчивого счетчика импульсов, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта. Макет был выполнен на микросхемах серии 564. Элементы памяти выполнены на базе сердечников из сплава АМАГ183. Время перемагничивания сердечников 20 мкс, время задержки сигналов в формирователях 5 мкс.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207717C2 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207718C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| СЧЕТЧИК ИМПУЛЬСОВ, СОХРАНЯЮЩИЙ ИНФОРМАЦИЮ ПРИ ПЕРЕРЫВАХ ПИТАНИЯ | 1991 |

|

RU2047271C1 |

| ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2038692C1 |

| ШИФРАТОР | 1989 |

|

RU2033691C1 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 2002 |

|

RU2213191C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1993 |

|

RU2065250C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036555C1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1993 |

|

RU2111609C1 |

Использование: в импульсной технике, в частности в счетном устройстве по двум независимым каналам. Сущность изобретения: счетное устройство содержит три элемента И-НЕ, два формирователя импульсов, счетчик импульсов, два дешифратора и N разрядов, каждый из которых содержит две ячейки памяти, и элемент И-НЕ. Счетное устройство имеет два счетных входа, вход начальной установки и два выхода. 2 ил.

СЧЕТНОЕ УСТРОЙСТВО, содержащее первый счетный вход, вход начальной установки, первый элемент И НЕ, первый формирователь и N разрядов, каждый из которых содержит две ячейки памяти и логический элемент, первый и второй входы элемента являются соответственно первым счетным входом и входом начальной установки устройства, тактовые входы первых ячеек памяти всех разрядов объединены и подключены к выходу элемента И НЕ, тактовые входы вторых ячеек памяти всех разрядов объединены, в каждом разряде выход второй ячейки памяти соединен с одним входом логического элемента, отличающееся тем, что введены счетный вход устройства, второй формирователь импульсов, второй и третий элементы И НЕ, N-разрядный счетчик импульсов, два дешифратора и два выхода устройства, первый вход второго элемента И НЕ соединен с входом начальной установки, второй вход с вторым счетным входом устройства, а выход с тактовыми входами вторых ячеек памяти разрядов, счетные входы устройства соединены с соответствующими входами третьего элемента И НЕ, выход которого подключен к входу первого формирователя импульсов, выход которого соединен с входом обнуления счетчика и входом второго формирователя импульсов, выход которого соединен с счетным входом счетчика, тактовые входы первого и второго дешифраторов соединены с выходами соответствующих элементов И НЕ, информационные входы с соответствующими выходами разрядов счетчика импульсов, а выходы являются соответствующими выходами счетного устройства, прямой выход каждого разряда счетчика импульсов соединен с информационными входами первой и второй ячеек памяти соответствующего разряда устройства, в каждом разряде которого второй вход логического элемента соединен с выходом первой ячейки памяти, а выход с входом установки соответствующего разряда счетчика импульсов, при этом логические элементы разрядов устройства выполнены в виде элементов И НЕ.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Счетное устройство сохраняющее информацию при перерывах питания | 1981 |

|

SU1051734A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-07-20—Публикация

1992-10-08—Подача