Изобретение относится к импульсной и вычислительной технике и может быть использовано для получения сетки стабильных частот в приеме- передающей и измерительной аппаратуре .

Целью изобретения является расширение функциональных возможностей путем придания ему свойств частотного детектора.

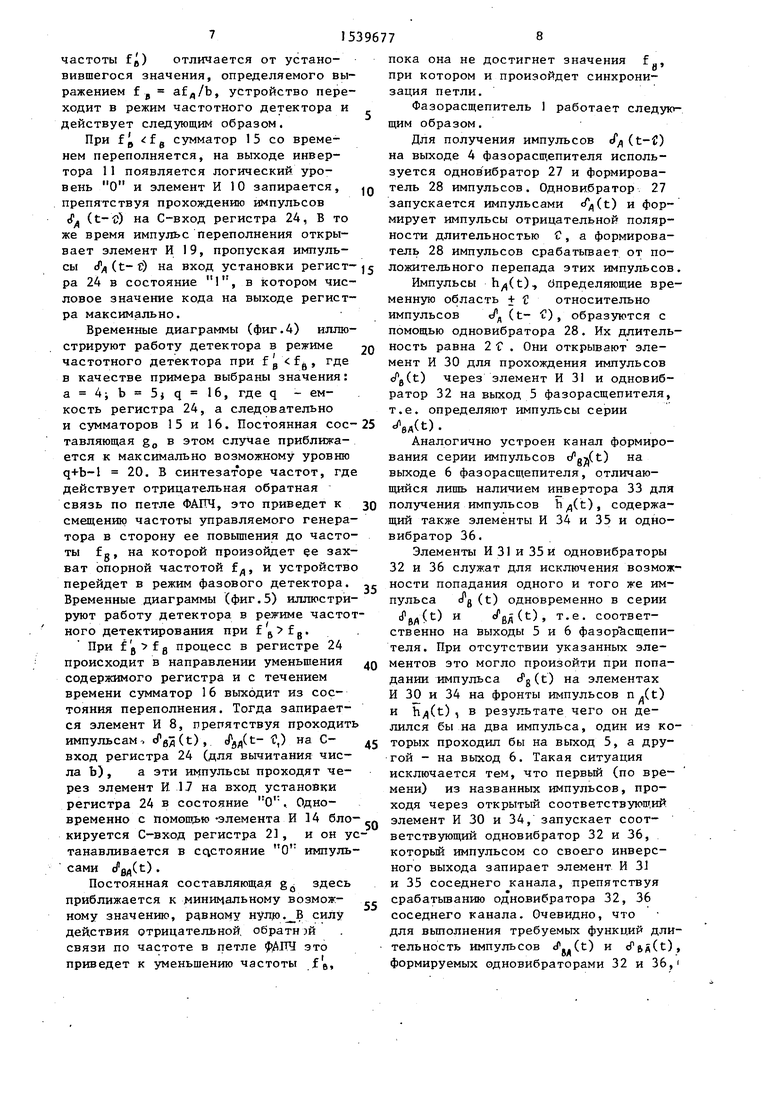

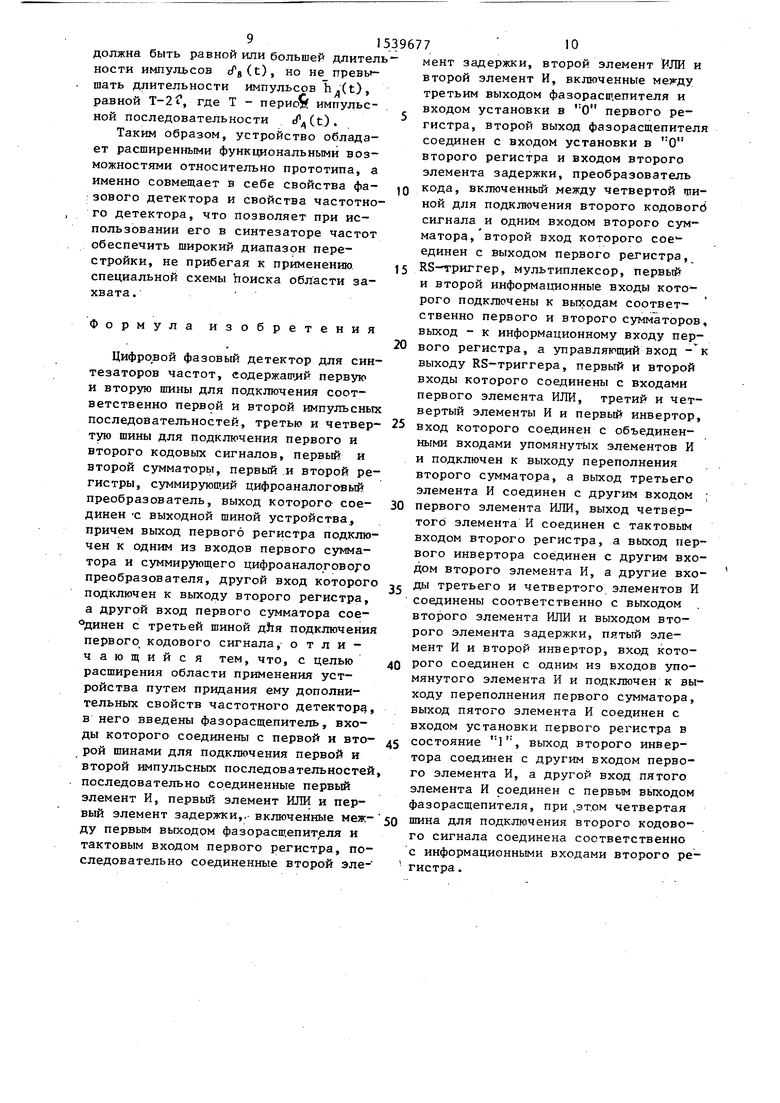

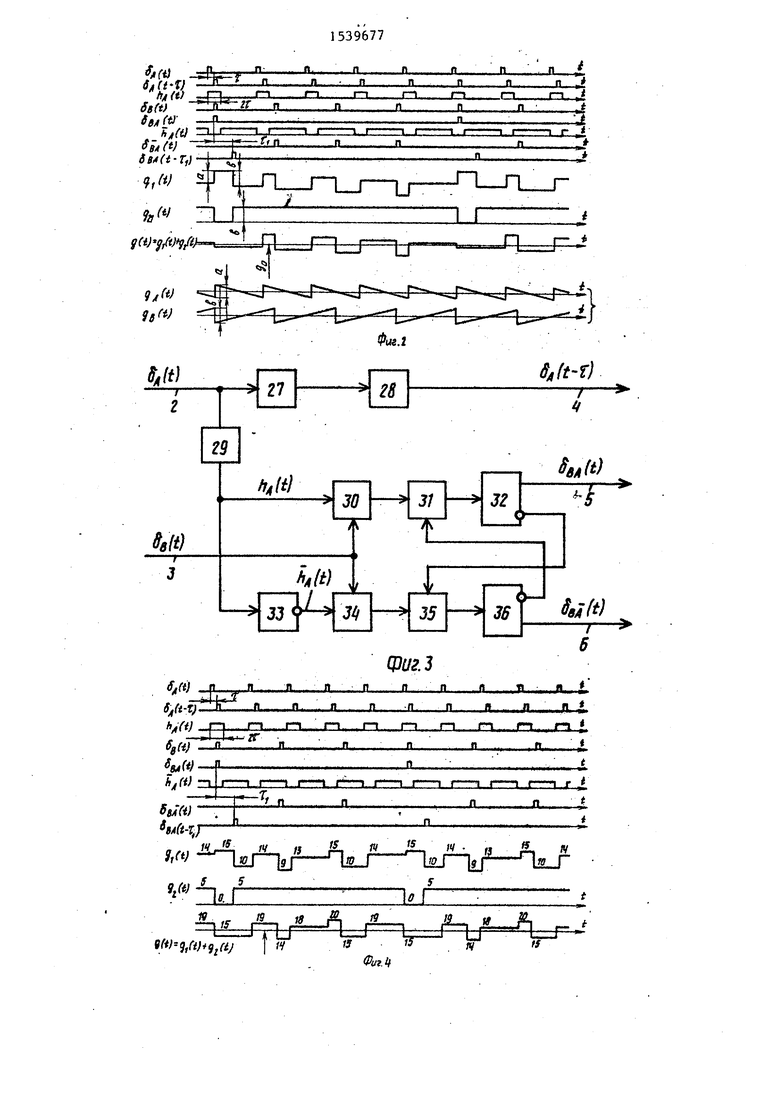

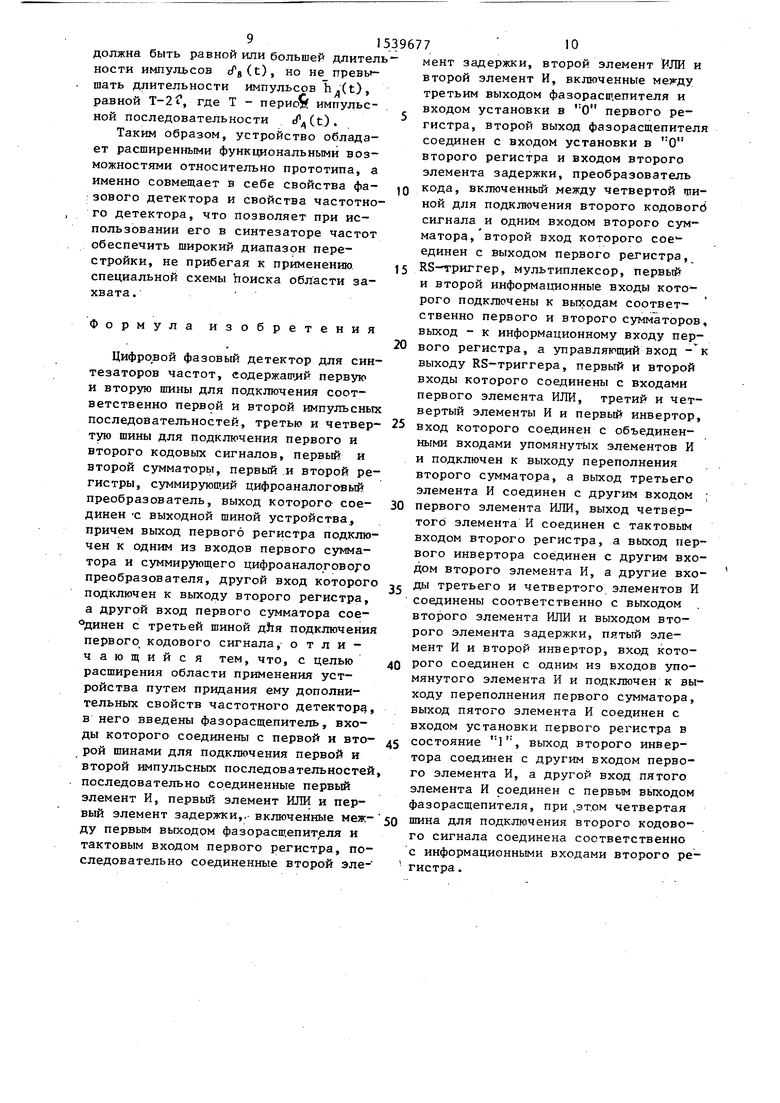

На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие работу уст- ройства на фиг. 3 - один из вариантов структурной электрической схемы фазорасщепителя со схемами совпадения; на фиг. 4,5 - временные диаграммы работы в режиме час- тотного детектирования.

Цифровой фазовый детектор содержит фазорасщепитель J со схемами совпадения, имеющий импульсные входы (шины) 2 и 3 соответственно для первой и второй импульсных последовательностей и выходы 4,5 и 6, элемент ИЛИ 7, элемент И 8, элемент 9 задержки, элемент И 10, инве тор 11, преобразователь 12 кода, ин вертор J3, элемент И 14, сумматоры 15 и 16, элемент И 17, RS-триггер 1 элемент И 19, мультиплексор 20,, регистр 21 , элемент ИЛИ. 22, элемент 23 задержки, регистр 24, суммирую- щий цифроаналоговый преобразователь (ЦАП) 25 и выход 26.

Первый выход 4 фазорасщепителя 1 через элемент И 19 соединен с входо установки 1 регистра 24, а через последовательно соединенные элементы И 10, элемент ИЛИ 22 и элемент 2 задержки с тактовым входом регистра 24. Второй выход 5 фазорасщепителя 1 соединен с входом установки О1 р гистра 21, а через последовательно соединенные элементы 9 задержки и элемент И 14 соединен с тактовым входом регистра 21.

Третий выход 6 фазорасщепителя 1 соединен с входом элемента ИЛИ 7, выход которого через элемент И 17 сединен с входом установки О 1 регисра 21 и через элемент И 8 с вторым входом элемента ИЛИ 22. Входы RS- триггера 18 соединены с входами элемента ИЛИ 22, а выход - с управляющим входом мультиплексора 20,

информационные входы которого соединены с выходами сумматоров 15 и 16. Выход мультиплексора 20 соединен с информационным входом регистра 24, выходч которого соединен с входами сумматоров 15 и 16 и ЦАП 25. Второй вход сумматора 15 соединен с одной шиной кодового сигнала, другая шина которого соединена с входами преобразователя 12 кода и информационным входом регистра 21, выход которого соединен с вторым входом ЦАП 25. Выход преобразователя 12 кода соединен с вторым входом сумматора 16, выход переполнения которого соединен с вторым входом элемента И 8 и через инвертор 13 с вторым входом элемента И 17. Выход переполнения сумматора 15 соединен с вторым входом элемента И 19 и через инвертор 11 с вторым входом элемента И 10.

Фазорасщепитель 1 содержит ждущий мультивибратор (одновибратор) 27, формирователь 28 импульсов, одно- вибратор 29, элементы И 30, 31, одновибратор 32, инвертор 33, элементы 34 и 35, и одновибратор 36.

Объединенные входы одновибратора 27 и 29 соединены с входом 2 фазорасщепителя 1. Выход одновибратора 27 через формирователь 28 импульсов соединен с выходом 4 фазорасщепителя 1. Выход одновибратора 29 через последовательно соединенные элементы

И 30 и 31 и одновибратор 32 соединен с выходом 5 фазорасщепителя 1, а

через последовательно соединенные инвертор 33, элементы И 34 и 35 и одновибратор 36 - с выходом 6 фазорасщепителя J . Второй выход одно- вибратора 32 соединен с вторым входом элемента И 35, а второй выход одновибратора 36 соединен с вторым входом элемента И 31. Вторые входы элементов И 30 и 34 соединены с входом 3 фазорасщепителя 1 .

Устройство работает следующим образом.

С помощью сумматоров 15 и 16 и регистра 24, подключаемого к сумматорам через мультиплексор 20, происходит добавление числа а к содержимому регистра 24 на каждом такте первой из сравниваемых импульсных последовательностей и вычитание числа Ъ на каждом такте второй последовательности импульсов. Названные элементы схемы образуют накапливающий сумматор (НС), в структуре которого поочередно используется один из сумматоров 15 или 16 в зависимости от логического уровня на управляющем входе мультиплексора 20.

Вычитание числа Ъ происходит путем подачи его на вход сумматора 16 через преобразователь 12 кода, который преобразует его в дополнительный код.

В режиме фазового детектирования (фиг.2) числа а и b связаны с частотами ЈА и f fl первой (РА (t) и второй cPB(t) импульсных последовательностей на входах 2 и 3 устройства соотношением аЈЛ -bfB, благодаря чему возрастание числа g 4(t) в регистре 24 под действием импульсов первой последовательности в среднем по времени компенсируется его убыванием под действием импульсов второй последовательности. При этом переполнение сумматора 15 отсутствует, а сумматор 16 постоянно переполнен .

Выход переполнения сумматора 15 через инвертор 11 подключен к одному из входов элемента И 10, что позволяет импульсам ) с первого выхода 4 фазорасщепителя проходить через последовательно включенные элемент И J 0, элемент ИЛИ 22 и эле-, мент 23 задержки на С-вход регистра 24. Эти же импульсы, поступая на второй вход RS-триггера J8, устанавливают последний в состояние, при котором к D-входу регистра 24 через мультиплексор 20 подключается выход сумматора J5, т,е. происходит прибавление числа а. .Время задержки С в эл менте 23 равно .или несколько превышает суммарное время переключений RS-триггера J8 и мультиплексора 20.

Для вычитания числа b используются две серии импульсов второй последовательности, получаемые в фазо- расщепителе 1 . На выходе 5 сформиг- рованы импульсы T6/,(t), находящиеся во временной области ± относительно положения импульсов «Pfl( - Ј ) на выходе 4. На выходе 6 - импульсы cCflA (t) , не входящие в названную область, Время Ј с некоторым запасом равно разрешающей способности регистра 24 по С-входу.

Если импульс rfg (t) появляется в области fj , т.е. действует практически одновременно с импульсом

PA(t- f), он попадает в серию импульсов Л)Д(Ј) и с выхода 5 фазорасщепителя 1 поступает на второй регистр 21 для установки его в состояние О. Этот же импульс спустя время Ј., , определяемое элементом 9 задержки, приходит через элемент И 14 на С-вход регистра 21 и устанавлиQ вает его в исходное состояние - хранение числа b (D-вход регистра подключен к второй кодовой шине устройства) . Одновременно задержанный импульс через элемент . ИЛИ 7 и элемент

5 И 8., поступает на первый вход RS-триггера 18, который переводит мультиплексор 20 на замыкание цепи выход сумматора 16 - D-вход регистра 24, а далее импульс через элемент ИЛИ 22 и

0 элемент 23 задержки воздействует на С-вход регистра 24, т.е. происходит вычитание числа b из содержимого регистра. Величина задержки €, в элементе 9 должна несколько превышать

5 величину 2С, чтобы импульсы JJ,(t-c) и вд (t- Ј,) , производящие соответственно прибавление и вычитание чисел а и Ь в регистре 24, были разнесены по времени на величину боль0 шую, чем разрешающая способность регистра 24 по С-входу.

В случае, когда импульсы Pe(t) попадают в серию cf(t) , они не поступают на регистр 21, а производят

,. вычитание числа b в регистре 24 аналогично импульсам fg(t- и), с которыми они суммируются на элементе ИЛИ 7.

Цифровые процессы g ,(t) и ga(t)

Q с выходов соответственно регистров 24 и 21 поступают на входы суммирующего ЦАП 25, преобразующего сумму g(t) процессов аналоговый эквивалент G(tJ, передаваемый на выход 26

5 устройства.

Как видно из фиг.2. результирующий процесс g(t) содержит постоянную составляющую g0 и пилообразные составляющие с- частотами f л и f6. Ана0 логовые эквиваленты последних двух составляющих устраняются петлевым фильтром, а постоянная составляющая - аналог gc, пропорциональная эквивалентной разности фаз импульсных последовательностей $ (t), Jj(t) проходит с выхода детектора в цепь

с

управления частотой генератора.

Если фактическое значение частоты управляемого генератора (например,

частоты fi) отличается от установившегося значения, определяемого выражением f B аЈд/Ь, устройство переходит в режим частотного детектора и действует следующим образом.

При fЈ fe сумматор 15 со временем переполняется, на выходе инвертора 11 появляется логический уровень О и элемент И 10 запирается, препятствуя прохождению импульсов fA (t-fl) на С-вход регистра 24, В то же время импульс переполнения открывает элемент И 19, пропуская импуль«fy(t-f) на вход установки регист-j ложительного перепада этих импульсов,

сы

ра 24 в состояние 1, в котором числовое значение кода на выходе регистра максимально.

Временные диаграммы (фиг.4) иллюстрируют работу детектора в режиме 20 частотного детектора при f g f B , где в качестве примера выбраны значения: , где q - емкость регистра 24, а следовательно и сумматоров 15 и 16. Постоянная сое- 25 тавляющая g0 в этом случае приближается к максимально возможному уровню q+b-1 20. В синтезаторе частот, где действует отрицательная обратная связь по петле ФАПЧ, это приведет к 30 смещению частоты управляемого генератора в сторону ее повышения до частоИмпульсы ), бпределяющие временную область + Ј относительно импульсов (t- -t) , образуются с помощью одновибратора 28. Их длительность равна 2 f . Они открывают элемент И 30 для прохождения импульсов c/g(t) через элемент И 31 и одновибратор 32 на выход 5 фазорасщепителя, т.е. определяют импульсы серии Лд(ь) .

Аналогично устроен канал формирования серии импульсов дъ(О на выходе 6 фазорасщепителя, отличающийся лишь наличием инвертора 33 для получения импульсов h/4(t), содержащий также элементы И 34 и 35 и одно- вибратор 36.

ты

-8

на которой произойдет ее захват опорной частотой Јл, и устройство перейдет в режим фазового детектора. Временные диаграммы (фиг.5) иллюстрируют работу детектора в режиме частот3

ного детектирования при

При процесс в регистре 24 происходит в направлении уменьшения содержимого регистра и с течением времени сумматор 16 выходит из состояния переполнения. Тогда запирается элемент И 8, препятствуя проходить импульсам-, сГбд(О, Лдд(ь- ,) на С- вход регистра 24 (для вычитания числа Ь) , а эти импульсы проходят через элемент И 17 на вход установки регистра 24 в состояние 0 :. Одновременно с помощью -элемента И 14 блокируется С-вход регистра 2, и он устанавливается в состояние О т импульсами cCflA(t) .

Постоянная составляющая gQ здесь приближается к минимальному возможному значению, равному нулю.В силу действия отрицательной обрати эй связи по частоте в петле ФАПЧ это приведет к уменьшению частоты f в,

пока она не достигнет значения

fl

при котором и произойдет синхронизация петли.

Фазорасщепитель 1 работает следующим образом.

Для получения импульсов fA (t-U) на выходе 4 фазорасщепителя используется одновибратор 27 и формирователь 28 импульсов. Одновибратор 27 запускается импульсами (t) и формирует импульсы отрицательной полярности длительностью С, а формирователь 28 импульсов срабатывает от по-

0 5 0

5

0

5

0

5

Импульсы ), бпределяющие временную область + Ј относительно импульсов (t- -t) , образуются с помощью одновибратора 28. Их длительность равна 2 f . Они открывают элемент И 30 для прохождения импульсов c/g(t) через элемент И 31 и одновибратор 32 на выход 5 фазорасщепителя, т.е. определяют импульсы серии Лд(ь) .

Аналогично устроен канал формирования серии импульсов дъ(О на выходе 6 фазорасщепителя, отличающийся лишь наличием инвертора 33 для получения импульсов h/4(t), содержащий также элементы И 34 и 35 и одно- вибратор 36.

Элементы И 31 и 35 и одновибраторы 32 и 36 служат для исключения возможности попадания одного и того же импульса cfe (t) одновременно в серии

(PB/,(t) и вл) соответственно на выходы 5 и 6 фазор асщепи- теля. При отсутствии указанных элементов это могло произойти при попадании импульса g(t) на элементах И 30 и 34 на фронты импульсов n.(t) и h(t), в результате чего он делился бы на два импульса, один из которых проходил бы на выход 5, а другой - на выход 6. Такая ситуация исключается тем, что первый (по времени) из названных импульсов, проходя через открытый соответствующий элемент И 30 и 34, запускает соответствующий одновибратор 32 и 36, который импульсом со своего инверсного выхода запирает элемент И 3J и 35 соседнего канала, препятствуя срабатыванию одновибратора 32, 36 соседнего канала. Очевидно, что для выполнения требуемых функций длительность импульсов М(О и tTftsd:), формируемых одновибраторами 32 и 36,

должна быть равной или большей длителности импульсов tfgCt), но не превышать длительности импульсов Ъ.(О, равной 1-2, где Т - период импульсной последовательности t(t).

Таким образом, устройство обладает расширенными функциональными возможностями относительно прототипа, а именно совмещает в себе свойства фа- зового детектора и свойства частотного детектора, что позволяет при использовании его в синтезаторе частот обеспечить широкий диапазон перестройки, не прибегая к применению специальной схемы поиска области захвата.

Формула изобретения

Цифровой фазовый детектор для синтезаторов частот, содержащий первую и вторую шины для подключения соответственно первой и второй импульсных последовательностей, третью и четвер- тую шины для подключения первого и второго кодовых сигналов, первый и второй сумматоры, первый и второй регистры, суммирующий цифроаналоговый преобразователь, выход которого сое- динен -с выходной шиной устройства, причем выход первого регистра подключен к одним из входов первого сумматора и суммирующего цифроаналогового

преобразователя, другой вход которого

подключен к выходу второго регистра, а другой вход первого сумматора соединен с третьей шиной для подключения первого, кодового сигнала, отличающийся тем, что, с целью расширения области применения устройства путем придания ему дополнительных свойств частотного детектора, в него введены фазорасщепитель, входы которого соединены с первой и вто- рой шинами для подключения первой и второй импульсных последовательностей последовательно соединенные первый элемент И, первый элемент ИЛИ и первый элемент задержки,, включенные между первым выходом фазорасщепителя и тактовым входом первого регистра, последовательно соединенные второй эле-

Q

0

5 0

5

Q 0

мент задержки, второй элемент ИЛИ и второй элемент И, включенные между третьим выходом фазорасщепителя и входом установки в О первого регистра, второй выход фазорасщепителя соединен с входом установки в К0 второго регистра и входом второго элемента задержки, преобразователь кода, включенный между четвертой шиной для подключения второго кодового сигнала и одним входом второго сумматора, второй вход которого сое1- единен с выходом первого регистра, RS-триггер, мультиплексор, первый и второй информационные входы которого подключены к выходам соответственно первого и второго сумматоров, выход - к информационному входу первого регистра, а управляющий вход - к выходу RS-триггера, первый и второй входы которого соединены с входами первого элемента ИЛИ, третий и четвертый элементы И и первый инвертор, вход которого соединен с объединенными входами упомянутых элементов И и подключен к выходу переполнения второго сумматора, а выход третьего элемента И соединен с другим входом первого элемента ИЛИ, выход четвертого элемента И соединен с тактовым входом второго регистра, а выход первого инвертора соединен с другим входом второго элемента И, а другие вхо- ды третьего и четвертого элементов И соединены соответственно с выходом второго элемента ИЛИ и выходом второго элемента задержки, пятый элемент И и второй инвертор, вход которого соединен с одним из входов упомянутого элемента И и подключен к выходу переполнения первого сумматора, выход пятого элемента И соединен с входом установки первого регистра в состояние , выход второго инвертора соединен с другим входом первого элемента И, а другой вход пятого элемента И соединен с первым выходом фазорасщепителя, при ,этом четвертая шина для подключения второго кодового сигнала соединена соответственно с информационными входами второго регистра .

hi .Ы6

&

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1987 |

|

SU1610599A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1988 |

|

SU1757080A1 |

| Синтезатор частот | 1986 |

|

SU1337990A1 |

| Синтезатор частот | 1987 |

|

SU1478327A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

| МНОГОЧАСТОТНЫЙ ФАЗОЦИФРОВОЙ ДЕТЕКТОР | 1988 |

|

RU2040851C1 |

| Синтезатор частот | 1988 |

|

SU1566455A1 |

| Квазисинхронный детектор | 1985 |

|

SU1352637A1 |

| Накапливающий сумматор | 1986 |

|

SU1374215A1 |

| Синтезатор частот | 1988 |

|

SU1656680A1 |

Изобретение относится к импульсной и вычислительной технике и может быть использовано для получения сетки стабильных частот в приемопередающей и измерительной аппаратуре. Цель изобретения - расширение функциональных возможностей устройства путем придания ему свойств частотного детектора. Цель достигается тем, что в цифровой фазовый детектор для синтезаторов частот, содержащий сумматоры 15 и 16, регистры 21 и 24 и суммирующий ЦАП 25 введены фазорасщепитель 1, инверторы 11 и 13, элементы И 8,10,14,17 и 19, элементы ИЛИ 7,22, элементы 9 и 23 задержки, преобразователь 12 кодов, RS - триггер 18 и мультиплексор 20. Введение новых элементов позволяет обеспечить дополнительно работу в режиме частотного детектирования. 5 ил.

ы

а

ТГUUТГU .«

ц

-цQ|fц-ицц- Т|Ц

Иtt UUUUUUК

ЈWO}

r

Г.

t- u

1

U

S S

и/т

J l-tJHf

J-

.«

ГТ

р- (М Ч

jjy j

jh-t/S

tfbtfbMt

С w«

ft/

r j

Ml 9

fv

ttj ff

f w «

,

;

iЈ96«t

i с

ч/ ч

-с:

V 5 53

I - «О «ч

. 5 C3N

t§ 4s - СзЧ

Редактор М. Циткина

Составитель М. Катанова

Техред М.Ходанич КорректорМ.Шароши

Заказ 215

Тираж 534

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Авторы

Даты

1990-01-30—Публикация

1988-04-26—Подача