Изобретение относится к вычислительной технике и может быть использовано для построения устройств сопряжения ЭВМ с периферийными устройствами (ПУ).

Для реализации более чем одного протокола обмена информацией между ЭВМ и ПУ различного типа с помощью одного устройства сопряжения используют программируемые интерфейсы, т. е. интерфейсы, способные менять свою конфигурацию под управлением программы. Большие возможности для построения такого рода устройств сопряжения дает применение БИС программируемого параллельного интерфейса (ППИ) КР580ВВ55А, предназначенной для организации ввода/вывода параллельной информации различного формата и позволяющей реализовывать большинство известных протоколов обмена по параллельным каналам [1, 2, 3, 4] В состав БИС для обмена информацией с внешними устройствами входят три 8-разрядных канала ввода/вывода (РОRТ А, В и С). Режим работы каждого из каналов ППИ программируется с помощью управляющего слова. Управляющее слово может задать один из трех режимов: основной режим ввода/вывода (режим 0), стробируемый ввод/вывод (режим 1), режим двунаправленной передачи информации (режим 2) [1]

Однако возможности построения устройств сопряжения для связи ЭВМ с ПУ на основе БИС ППИ ограничиваются малой нагрузочной способностью микросхемы (выходной ток низкого уровня 1, 7 мА [5]). Повышенная нагрузочная способность портов интерфейсных устройств требуется, например, в случае удаленного ПУ и, следовательно, возникает необходимость работы на коаксиальный кабель или витую пару большой длины. Установка буферных каскадов со стороны портов микросхемы осложняется тем, что необходимо переключать направление передачи информации по ним, не ограничивая при этом возможности микросхемы по режимам работы и направлениям передачи, а также не снижая скорости обмена информацией. Авторам известен случай применения шинных формирователей, в том числе и для умощнения портов ППИ в универсальном интерфейсе [8] Однако указанный вариант сужает потенциальные возможности ППИ, т. к. для управления формирователями, установленными по портам А и В, используются сигналы портов С и, следовательно, они не могут быть использованы самостоятельно в качестве сигналов, участвующих в обмене информацией с ПУ.

Предлагаемое изобретение решает задачу повышения нагрузочной способности устройства сопряжения, построенных на основе ППИ, не ограничивая при этом его возможностей по реализации всего многообразия протоколов обмена информацией между ЭВМ и конкретным ПУ.

Наиболее близким к предлагаемому изобретению и может быть рассмотрено устройство для связи персонального компьютера типа IВМ РС с накопителем на магнитной ленте НМЛ СМ5309 [6]

Поставленная цель достигается тем, что в устройство, содержащее буфер данных, селектор адреса и два программируемых параллельных интерфейса, введены буферные каскады четыре блока шинных формирователей и два блока буферных элементов, два регистра, два дешифратора управляющего слова, два элемента НЕ, формирователь сигналов записи, два формирователя сигналов управления.

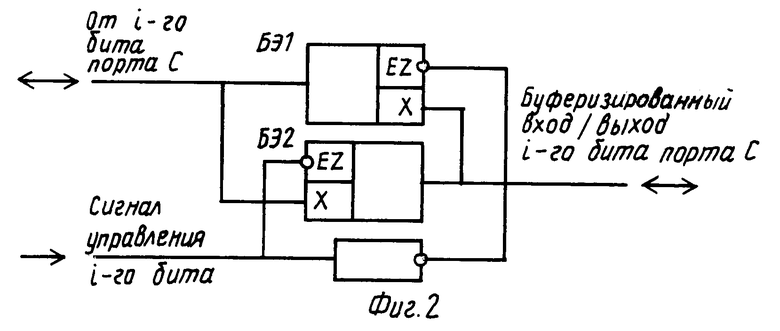

На фиг. 1 представлена структурная схема прогpаммируемого устройства сопряжения с повышенной нагрузочной способностью.

Устройство содержит буфер данных 1, селектор адреса 5, два программируемых интерфейса 2.1 и 2.2, четыре блока шинных формирователей 3.1, 3.2, 3.3, 3.4, два блока буферных элементов 4.1 и 4.2, два регистра 8.1 и 8.2, два дешифратора управляющего слова 10.1 и 10.2, два элемента НЕ 7.1 и 7.2, формирователь сигналов записи 9, два формирователя сигналов управления 6.1 и 6.2.

Первая группа входов-выходов буфера данных является группой входов-выходов данных устройства, первая группа входов селектора адреса является группой адресных входов устройства, вторая группа входов селектора адреса является группой входов сигналов управления устройства, вторая группа входов-выходов буфера данных соединена с группой входов-выходов данных первого и второго программируемых параллельных интерфейсов, выход чтения группы выходов селектора адреса соединен с входами чтения первого и второго программируемых параллельных интерфейсов и соединен с входом чтения буфера данных, выход выбора устройства группы выходов селектора адреса соединен с входом выбора буфера данных, выходы записи и сброса группы выходов селектора адреса соединены соответственно с входами записи и сброса первого и второго программируемых параллельных интерфейсов, нулевой и первый разряды выхода выбора интерфейса группы выходов селектора адреса соединены с входами выбора соответственно первого и второго программируемых параллельных интерфейсов, нулевой и первый разряды адресного выхода группы выходов селектора адреса соединены соответственно с нулевым и первым разрядами адресного входа группы входов первого и второго программируемых параллельных интерфейсов, первые группы входов-выходов каждого блока шинных формирователей и блока буферных элементов являются соответствующими группами входов-выходов устройства, нулевой, второй, третий, пятый, шестой, седьмой разряды второй группы входов-выходов буфера данных соединены с соответствующими информационными входами первого и второго регистров, первый разряд второй группы входов-выходов буфера данных подключен через первый элемент НЕ к первым разрядам информационных входов, первого и второго регистров, четвертый разряд второй группы входов-выходов буфера данных подключен через второй элемент НЕ к четвертым разрядам информационных входов первого и второго регистров, седьмой разряд второй группы входов-выходов буфера данных подключен к первому входу формирователя сигналов записи, второй и третий входы, которого соединены соответственно с нулевым и первым разрядами адресного выхода группы выходов селектора адреса, четвертый, пятый и шестой входы формирователя сигналов записи соединены соответственно с выходом записи, с нулевым и первым разрядами выбора селектора адреса, первый и второй выходы формирователя сигналов записи соединены соответственно с входами записи первого и второго регистров, выход сброса группы выходов селектора адреса соединен с входами сброса первого и второго регистров, группа выходов первого порта первого программируемого параллельного интерфейса соединена с группой информационных входов первого блока шинных формирователей, группа выходов второго порта первого программируемого параллельного интерфейса соединена с группой информационных входов первого блока буферных элементов, группа выходов третьего порта первого программируемого параллельного интерфейса соединена с группой информационных входов второго блока шинных формирователей, группа выходов первого порта второго программируемого параллельного интерфейса соединена с группой информационных входов третьего блока шинных формирователей, группа выходов второго порта второго программируемого параллельного интерфейса соединена с группой информационных входов второго блока буферных элементов, группа выходов третьего порта второго программируемого параллельного интерфейса соединена с группой информационных входов четвертого блока шинных формирователей, группа выходов первого регистра соединена с группой адресных входов первого дешифратора управляющего слова, первый разрядный выход группы выходов первого регистра соединен с управляющим входом второго блока шинных формирователей, четвертый и шестой разрядные выходы группы выходов первого регистра соединены соответственно с первым и вторым входами первого формирователя сигналов управления, третий вход первого формирователя сигналов управления соединен с шестым выходом группы выходов первого блока буферных элементов, выход первого формирователя сигналов управления соединен с входом управления первого блока шинных формирователей, группа выходов второго регистра соединена с группой адресных входов второго дешифратора управляющего слова, первый разрядный выход группы выходов второго регистра соединен с управляющим входом четвертого блока шинных формирователей, четвертый и шестой разрядные выходы группы выходов второго регистра соединены с первым и вторым входами второго формирователя сигналов управления, третий вход второго формирователя сигналов управления соединен с шестым выходом группы выходов второго блока буферных элементов, выход второго формирователя сигналов управления соединен с входом управления третьего блока шинных формирователей, группа выходов первого дешифратора управляющего слова соединена с группой управляющих входов первого блока буферных элементов, группа выходов второго дешифратора управляющего слова соединена с группой управляющих входов второго блока буферных элементов.

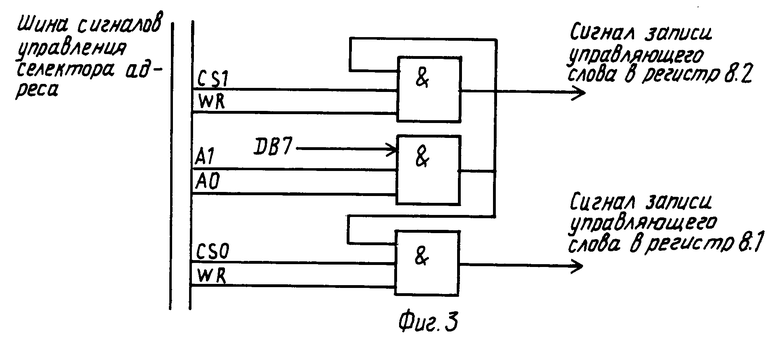

Особенностью построения буферных каскадов устройства является то, что шинные формирователи первых и третьих портов (портов А и В) могут быть выполнены группой по восемь, по числу линий портов, например, на ИМС К555АП6, с единым управляющим входом, а блоки вторых портов (портов С) должны иметь буферные элементы с возможностью управления на ввод или вывод по каждому биту порта в отдельности.

На фиг. 2 представлена схема соединения буферных элементов БЭ1 и БЭ2 в блоках 4.1 и 4.2 для одного бита портов С интерфейсов. Элементы имеют третье состояние, поэтому в случае, если сигнал управления принимает значение лог. "1", то элемент БЭ2 выключается и вся схема работает на ввод.

Устройство сопряжения работает следующим образом.

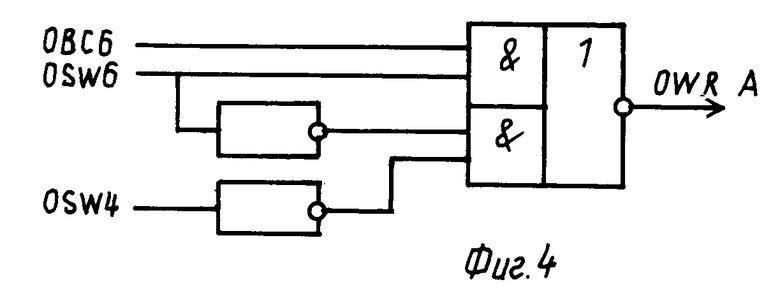

Перед началом работы ЭВМ с конкретным ПУ необходимо запрограммировать (сконфигурировать) интерфейсы 2 устройства сопряжения под назначенный протокол обмена информацией (применение двух ППИ позволяет вести обмен информацией с ПУ 16-разрядными словами). Для этого по шине ЭВМ (для примера, как и в прототипе, рассмотрена шина ЭВМ типа IВМ РС) в каждый интерфейс поочередно пересылается свое управляющее слово. Для формирования сигналов управления буферными каскадами 3, 4 нельзя непосредственно воспользоваться информацией этих слов, так как они аппаратно недоступны. Для дополнительной фиксации управляющих слов введены два регистра 8.1 и 8.2. Формирование сигналов записи в эти регистры происходит с помощью формирователя 9, построенного, например, как показано на фиг. 3, на трех схемах совпадения. Формирование сигналов записи происходит при наличии следующих сигналов:

сигнал на запись WR, сформированный селектором адреса из сигнала вывода IOW шины ЭВМ;

сигнал выбора интерфейсов СSO или CSI, сформированных селектором адреса по сигналам линий адреса шины ЭВМ;

сигналов А0 и А1, являющихся признаками обращения по адресам управляющих слов и cформированных селектором адреса из одноименных сигналов линий адреса шины ЭВМ;

сигнала DВ7 (D7 1 в управляющем слове), представляющего собой буферизированный сигнал по линии данных D7 шины ЭВМ и свидетельствующий, при наличии всех вышеперечисленных сигналов, о смене конфигурации в одном из интерфейсов (при D7 0 в управляющем слове, интерфейс работает в дополнительном режиме программно независимой установки в 1 и сброса в 0 любого из разрядов регистра порта С, не меняющем конфигурации портов). Наличие именно этих сигналов, всегда сопровождающих смену или начальную установку конфигурации интерфейсов, приводит к автоматической фиксации управляющих слов в регистрах. Так, если происходит установка конфигурации интерфейса 2.1, то это будет сопровождаться в том числе сигналом выбора СSO и появится сигнал записи в регистр 8.1.

Для управления шинными формирователями блоков 3.2, 3.4 по портам В интерфейсов может быть использован 1-й бит 0SWI, 1SWI соответствующего управляющего слова регистров 8, т. к. именно этот бит управляющего слова интерфейса определяет режим на ввод или вывод по этому порту [7]

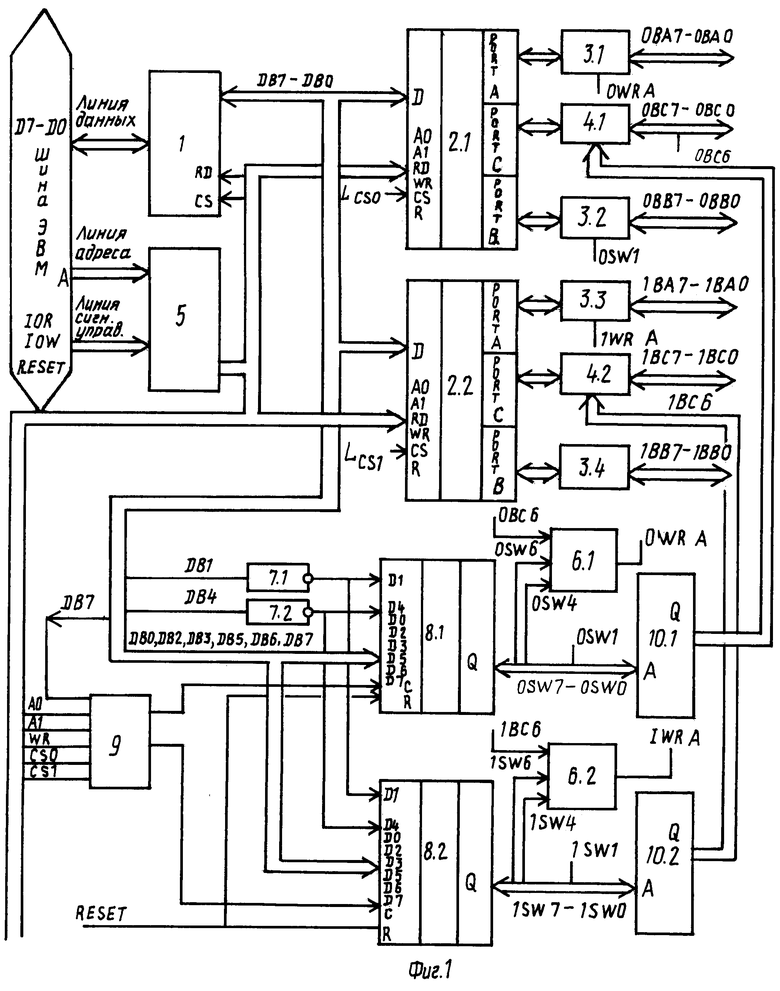

Шинные формирователи блоков 3.1, 3.3 портов А не должны препятствовать выполнению протокола режима 2 интерфейсов, при котором запись информации в ПУ сопровождается сигналом ПУ "Подтверждение записи", поступающим в устройство сопряжения по шестому биту канала С 0ВС6 (1ВС6) [7] Поэтому для формирования управляющих сигналов 0WR А или 1WR А, определяющих направление передачи блоков 3.1 или 3.3, служат два формирователя 6 построенных, например, с помощью логической схемы И-ИЛИ-НЕ, показанной на фиг. 4.

Схема формирует сигнал 0WR А в зависимости от выбранного режима по порту А. В случае работы порта А интерфейса 2.1 в режимах 0 или 1, о чем будет свидетельствовать наличие логического 0 в шестом бите управляющего слова интерфейса и слова зафиксированного в регистре 8.1, сигнал 0WR А будет определяться четвертым битом 0SW4 слова регистра, поскольку именно он в управляющем слове интерфейса определяет режим на ввод или вывод.

В случае работы в режиме 2 (логическая 1 в шестом бите управляющего слова) режим на ввод или вывод формирователей будет определяться внешним для устройства сопряжения сигналом периферийного устройства 0ВС6.

Для преодоления конфликтных ситуаций по линиям связи устройства сопряжения с ПУ до того момента, как интерфейсы и буферные каскады запрограммированы под выбранный протокол, необходимо предусмотреть, чтобы все каскады были включены на ввод. Для этого можно использовать сигнал шины ЭВМ по линии RESEТ, буферизованный селектором адреса, который формируется после включения питания ЭВМ. Этот сигнал будет сбрасывать все биты регистров 8. Учитывая, что при программировании интерфейсов по портам А и В на ввод в первом и четвертом блоках управляющего слова требуется логическая 1, сигналы по цепям этих битов на входе регистров 8 инвертируются. Теперь в случае программирования портов А и В на ввод, в также после прохождения сигнала RESEТ в первом и четвеpтом разрядах будет зафиксирован 0, определяя работу формирователей портов на ввод.

Так как четвертый бит формирует сигнал управления 0WR А (1WR А), то в схему формирователя 6 могут быть введены инверторы четвертого 0SW4 (1SW4) и шестого 0SW6 (1SW6) битов регистров 8, а соблюдение полярности сигнала управления 0WR А (1WR А) будет обеспечиваться наличием инверсии в схеме И-ИЛИ-НЕ.

Для переключения буферных элементов портов С интерфейсов в устройство сопряжения введены дешифраторы 10, формирующие по восемь управляющих сигналов в зависимости от управляющего слова регистра 8. Дешифратор управляющего слова может быть выполнен с помощью программируемого постоянного запоминающего устройства ППЗУ, к адресным входам которого подводится управляющее слово 0SW (1SW) регистров 8. ППЗУ программируются таким образом, чтобы вырабатываемые ими сигналы управления обеспечивали переключение направления передачи информации по каждой линии блоков 4 в точном соответcтвии с направлениями, установленными по интерфейсах по портам С.

Например, если по протоколу обмена с ПУ интерфейс 2.1 будет запрограммирован на режим 0 по всем портам А, В и С, то ППЗУ дешифратора 10.1 должно формировать сигналы, управляющие буферными элементами в соответствии с табл. 1.

Из данных табл. 1 видно, что значение управляющих сигналов, переключающих буферные элементы блоков 4.1 на ввод или вывод, определяется значениями бита D0 для элементов битов С3-С0 и битом D3 для элементов битов С7-С4. Значения битов D4 и D1 в таблице не определены, т. к. они не влияют на конфигурацию портов С ППИ.

В табл. 2 показано программирование ППЗУ дешифратора для случая использования ППИ в режиме 1, когда порты А и В используются для обмена данными, а линии порта С для приема и выдачи сигналов управления (сигналов квитирования).

В табл. 3 показано программирование ППЗУ дешифратора для случая использования режима 2 ППИ, когда буферные элементы блока 4.1 должны обеспечивать протокол обмена информацией с ПУ по двунаправленному порту А. При этом также должна обеспечиваться возможность обмена информацией по порту В в режимах 0 и 1.

В табл. 3 первые две строки обеспечивают возможность работы в режиме 2 по порту А, а три младших бита порта С могут быть использованы как дополнительные для ввода или вывода. Последней строкой, кроме режима 2 по порту А, обеспечивается возможность обмена по порту 8 в режиме 1, при котором три младших бита порта С используются в качестве сигналов управления.

Таким образом, введение буферных каскадов и других дополнительных блоков в программируемое устройство сопряжения позволило расширить область применения устройства за счет повышения его нагрузочной способности. Так нагрузочная способность по портам А и В (в случае применения в качестве формирователей, например, ИМС К555АП6) увеличивается до 24 мА, а по портам С (в случае применения ИМС К555ЛП8) до 12 мА. При этом сохраняются все потенциальные возможности интерфейсов на ИМС KР80ВВ55А по обеспечению многообразия протоколов обмена информацией с различными периферийными устройствами.

Предлагаемое устройство может рассматриваться как универсальное устройство сопряжения с программно-изменяемой конфигурацией буферизированных портов на ввод или вывод. Применение двух ППИ в устройстве позволяет вести обмен с ПУ как байтами, так и 16-разрядными словами, обеспечивая различные варианты протоколов обмена. Кроме того, устройство предоставляет возможность обмена по 48-ми буферизированным линиям. Повышенная нагрузочная способность устройства позволяет использовать его также в случаях, когда ПУ удалено и возникает необходимость передачи информации по линиям, имеющим повышенную емкостную нагрузку. Введение буферных каскадов позволяет в этом случае сохранить скорость обмена и обеспечить достоверность передаваемой информации. Наличие буферных каскадов также защищает достаточно сложные и дорогостоящие схемы интерфейсов от возможных повреждений в случае нарушений в работе ПУ.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ МАГИСТРАЛЕЙ | 1990 |

|

RU2017210C1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 1991 |

|

RU2074514C1 |

| ЦИФРОВАЯ СИСТЕМА СТАБИЛИЗАЦИИ СКОРОСТИ | 1990 |

|

RU2047890C1 |

| КОММУТАТОР LINK-ПОРТОВ | 2009 |

|

RU2405196C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Устройство адресации к памяти | 1987 |

|

SU1561834A3 |

Изобретение относится к вычислительной технике и может быть использовано для построения устройств сопряжения ЭВМ с периферийными устройствами. Изобретение решает задачу повышения нагрузочной способности устройств сопряжения, построенных на основе применения программируемых параллельных интерфейсов (ППИ), не ограничивая при этом его возможностей по реализации всего многообразия протоколов обмена информацией между ЭВМ и конкретным ПУ. Устройство содержит буфер данных 1, селектор адреса 5, два программируемых параллельных интерфейса 2.1 и 2.2, четыре блока шинных формирователей 3.1, 3.2, 3.3, 3.4, два блока буферных элементов 4.1 и 4.2, два регистра 8.1 и 8.2, два дешифратора управляющих слов 10.1 и 10.2, два элемента НЕ 7.1 и 7.2, формирователь сигналов записи 9, два формирователя сигналов управления 6.1 и 6.2. 4 ил. 3 табл.

ПРОГРАММИРУЕМОЕ УСТРОЙСТВО СОПРЯЖЕНИЯ С ПОВЫШЕННОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ, содержащее буфер данных, селектор адреса и два программируемых параллельных интерфейса, причем первая группа входов-выходов буфера данных является группой входов-выходов данных устройства, первая группа входов селектора адреса является группой адресных входов устройства, вторая группа входов селектора адреса является группой входов сигналов управления устройства, вторая группа входов-выходов буфера данных соединена с группой входов-выходов данных первого и второго программируемых параллельных интерфейсов, выход чтения группы выходов селектора адреса соединен с входами чтения первого и второго программируемых параллельных интерфейсов и соединен с входом чтения буфера данных, выход выбора устройства группы выходов селектора адреса соединен с входом выбора буфера данных, выходы записи и сброса группы выходов селектора адреса соединены соответственно с входами записи и сброса первого и второго программируемых параллельных интерфейсов, нулевой и первый разрядные выходы выбора интерфейса группы выходов селектора адреса соединены с входами выбора соответственно первого и второго программируемых параллельных интерфейсов, нулевой и первый разряды адресного выхода группы выходов селектора адреса соединены соответственно с нулевым и первым разрядами адресного входа группы входов первого и второго программируемых параллельных интерфейсов, отличающееся тем, что в него введены четыре блока шинных формирователей, два блока буферных элементов, два регистра, два дешифратора управляющего слова, два элемента НЕ, формирователь сигналов записи и два формирователя сигналов управления, причем первые группы входов-выходов каждого блока шинных формирователей и блока буферных элементов являются соответствующими группами входов-выходов устройства, нулевой, второй, третий, пятый, шестой и седьмой разряды второй группы входов-выходов буфера данных соединены с соответствующими информационными входами первого и второго регистров, первый разряд второй группы входов-выходов буфера данных подключен через первый элемент НЕ к первым информационным входам первого и второго регистров, четвертый разряд второй группы входов-выходов буфера данных подключен через второй элемент НЕ к четвертому разряду информационных входов первого и второго регистров, седьмой разряд второй группы входов-выходов буфера данных подключен к первому входу формирователя сигналов записи, второй и третий входы которого соединены соответственно с нулевым и первым разрядами адресного выхода группы выходов селектора адреса, четвертый, пятый и шестой входы формирователя сигналов записи соединены соответственно с выходом записи, с нулевым и первым разрядами выхода выбора селектора адреса, первый и второй выходы формирователя сигналов записи соединены соответственно с входами записи первого и второго регистров, выход сброса группы выходов селектора адреса соединен с входами сброса первого и второго регистров, группа выходов первого порта первого программируемого параллельного интерфейса соединен с группой информационных входов первого блока шинных формирователей, группа выходов второго порта первого программируемого параллельного интерфейса соединена с группой первого блока буферных элементов, группа выходов третьего порта первого программируемого параллельного интерфейса соединена с группой информационных входов второго блока шинных формирователей, группа выходов первого порта второго программируемого параллельного интерфейса соединена с группой информационных входов третьего блока шинных формирователей, группа выходов второго порта второго программируемого параллельного интерфейса соединена с группой информационных входов второго блока буферных элементов, группа выходов третьего порта второго программируемого параллельного интерфейса соединена с группой информационных входов четвертого блока шинных формирователей, группа выходов первого регистра соединена с группой адресных входов первого дешифратора управляющего слова, первый разрядный выход группы выходов первого регистра соединен с управляющим входом второго блока шинных формирователей, четвертый и шестой разрядные выходы группы выходов первого регистра соединены соответственно с первым и вторым входами первого формирователя сигналов управления, третий вход первого формирователя сигналов управления соединен с шестым выходом группы выходов первого блока буферных элементов, выход первого формирователя сигналов управления соединен с входом управления первого блока шинных формирователей, группа выходов второго регистра соединена с группой адресных входов второго дешифратора управляющего слова, первый разрядный выход группы выходов второго регистра соединен с управляющим входом четвертого блока шинных формирователей, четвертый и шестой разрядные выходы групппы выходов второго регистра соединены соответственно с первым и вторым входами второго формирователя сигналов управления, третий вход второго формирователя сигналов управления соединен с шестым выходом группы выходов второго блока буферных элементов, выход второго формирователя сигналов управления соединен с входом управления третьего блока шинных формирователей, группа выходов первого дешифратора управляющего слова соединена с группой управляющих входов первого блока буферных элементов, группа выходов второго дешифратора управляющего слова соединена с группой управляющих входов второго блока буферных элементов.

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Накалов Е.Ф., Тюлькин С.П | |||

| Способ приготовления консистентных мазей | 1919 |

|

SU1990A1 |

Авторы

Даты

1995-07-09—Публикация

1992-07-03—Подача