Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известно счетное устройство (см. патент РФ 2047271 от 18.11.91, МКИ: Н 03 К 21/40. "Счетчик импульсов, сохраняющий информацию при перерывах питания" /И.И. Дикарев, Л.Б. Егоров, Г.И. Шишкин//Опубл. 27.10.95, Бюл. 30), содержащее блок управления и n счетных ячеек, каждая из которых содержит сердечник с прямоугольной петлей гистерезиса и обмотками - выходной и записи, четыре логических элемента и два резистора, при этом первый вход блока управления является счетным входом устройства, первый вход соединен с первым входом каждой счетной ячейки, а второй выход - со вторым входом первой счетной ячейки, второй вход каждой i-ой счетной ячейки, где i - 2, 3..., n, соединен с первым выходом (i-1)-ой ячейки, а третий вход - со вторым выходом (i-1)-ой ячейки, второй выход n-ой счетной ячейки является выходом устройства, четвертые входы всех счетных ячеек объединены, в каждой счетной ячейке первый вход первого логического элемента является первым входом ячейки, выход второго логического элемента соединен через первый резистор с началом обмотки записи сердечника, а первый вход - с выходом четвертого логического элемента, вход которого является вторым входом счетной ячейки, третьим входом которой является первый вход третьего логического элемента, конец выходной обмотки сердечника соединен с выводом второго резистора, блока анализа четности, контрольного сердечника с прямоугольной петлей гистерезиса и обмоткой, двух элементов И-НЕ с открытыми стоками (коллекторами), резистора и блока формирования сигнала ошибки, а в каждую счетную ячейку введен RS-триггер, причем интенсивный и прямой выходы блока анализа четности соединены с первыми входами, соответственно, первого и второго элементов И-НЕ и, соответственно, с третьим и пятым входами первой счетной ячейки, n входов соединены со вторыми входами соответствующих счетных ячеек, пятый вход каждой i-ой счетной ячейки (где i - 2,3,... n) соединен с третьим выходом (i-1)-ой счетной ячейки, второй вход блока управления соединен с шиной начальной установки, третий выход соединен с четвертыми входами счетных ячеек, четвертый выход - со вторым входом элементов И-НЕ, а пятый выход - с выходом второго элемента И-НЕ, с первым входом блока формирования сигнала ошибки и через обмотку контрольного сердечника с выходом первого элемента И-НЕ и вторым входом блока формирования сигнала ошибки, третий вход которого соединен со вторым входом блока управления, а выход является контрольным выходом устройства, средняя точка обмотки контрольного сердечника через резистор соединена с шиной питания, в каждой счетной ячейке R-вход RS-триггера является четвертым входом ячейки, S-вход соединен с другим выводом второго резистора, прямой выход соединен со вторым входом второго логического элемента и является вторым выходом ячейки, а инверсный выход является третьим выходом счетной ячейки, начало выходной обмотки сердечника соединено с общей шиной, а конец обмотки записи - с выходом первого логического элемента, второй вход которого соединен с выходом второго логического элемента, выход третьего логического элемента является первым выходом счетной ячейки, а второй вход соединен с первым входом четвертого логического элемента, второй вход которого является пятым входом счетной ячейки, первый и четвертый логические элементы выполнены в виде элементов ИЛИ-НЕ, второй логический элемент - в виде элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а третий логический элемент - в виде элемента ИЛИ.

Недостатками данного счетного устройства является сложность схемной реализации в связи с большим количеством элементов в каждом разряде, и большой ток перемагничивания сердечников в связи с ограничением числа витков обмотки записи за счет наличия выходной обмотки.

Известно счетное устройство (см. патент РФ 2040113 от 08.10.92, МКИ: Н 03 К 23/76. "Счетное устройство". /И. И. Дикарев, Л.Б. Егоров, Г.И. Шишкин//Опубл. 27.07.95, Бюл. N 20), которое является наиболее близким по технической сущности и взято в качестве прототипа. Устройство содержит первый счетный вход, вход начальной установки, первый элемент И-НЕ, первый формирователь и N разрядов, каждый из которых содержит две ячейки памяти и логический элемент, первый и второй входы элемента являются, соответственно, первым счетным входом и входом начальной установки устройства, тактовые входы первых ячеек памяти всех разрядов объединены и подключены к выходу элемента И-НЕ, тактовые входы вторых ячеек памяти всех разрядов объединены, в каждом разряде выход второй ячейки памяти соединен с одним входом логического элемента. Второй счетный вход устройства, второй формирователь импульсов, второй и третий элементы И-НЕ, N-разрядный счетчик импульсов, два дешифратора и два выхода устройства, первый вход второго элемента И-НЕ соединен с входом начальной установки, второй вход - со вторым счетным входом устройства, а выход - с тактовыми входами вторых ячеек памяти разрядов, счетные входы устройства соединены с соответствующими входами третьего элемента И-НЕ, выход которого подключен к входу первого формирователя импульсов, выход которого соединен с входом обнуления счетчика и входом второго формирователя импульсов, выход которого соединен со счетным входом счетчика, тактовые входы первого и второго дешифратора соединены с выходами соответствующих элементов И-НЕ, информационные входы - с соответствующими выходами разрядов счетчика импульсов, а выходы являются соответствующими выходами счетного устройства, прямой выход каждого разряда счетчика импульсов соединен с информационными входами первой и второй ячеек памяти соответствующего разряда устройства, в каждом разряде которого второй вход логического элемента соединен с выходом первой ячейки памяти, а выход - с входом установки соответствующего разряда счетчика импульсов, при этом логические элементы разрядов устройства выполнены в виде элементов И-НЕ.

Недостатком прототипа является сложность схемной реализации даже для одноканального устройства, связанная в первую очередь с необходимостью использования логических элементов И-НЕ с открытым стоком и счетного триггера.

Задачей, решаемой предлагаемым изобретением, является упрощение счетного устройства.

Технический результат, достигается тем, что счетное устройство содержит счетный вход и вход начальной установки, два формирователя импульсов и N-разрядов, каждый из которых содержит ячейку памяти на магнитном сердечнике с прямоугольной петлей гистерезиса и обмоткой, средняя точка которой соединена с первым выводом резистора. Новым является то, что дополнительно введены логический элемент ИЛИ-НЕ счетного устройства, первый вход которого соединен со счетным входом счетного устройства, а второй вход - со входом начальной установки счетного устройства, в каждый разряд счетного устройства введены первый и второй логические элементы ИЛИ-НЕ, RS-триггер и полусумматор, первый вход которого соединен с прямым выходом RS-триггера, являющимся выходом счетного устройства, вход установки RS-триггера соединен с выходом второго логического элемента ИЛИ-НЕ, первый вход которого соединен с началом обмотки сердечника, конец которой соединен с выходом первого логического элемента ИЛИ-НЕ, первый вход которого соединен с выходом полусумматора, вторым выводом резистора и вторым входом второго логического элемента ИЛИ-НЕ, входы сброса RS-триггеров всех разрядов объединены и соединены с выходом первого формирователя импульсов и с входом второго формирователя импульсов, выход которого соединен со вторым входом полусумматора первого разряда, выход переноса которого соединен со вторым входом полусумматора последующего разряда, при этом вход первого формирователя импульсов соединен с первым входом логического элемента ИЛИ-НЕ счетного устройства, выход которого соединен с объединенными вторыми входами логических первых элементов ИЛИ-НЕ каждого разряда.

Указанная совокупность признаков позволяет упростить счетное устройство путем замены счетных триггеров RS-триггерами и отказа от использования логических элементов И-НЕ с открытым стоком.

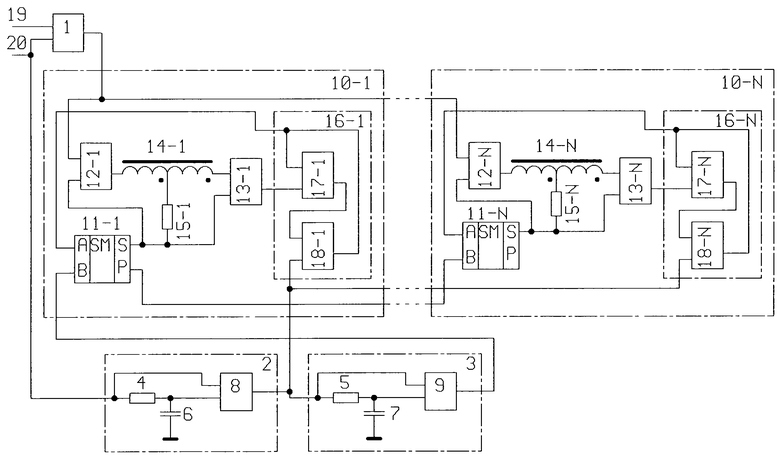

На чертеже приведена принципиальная схема счетного устройства.

Счетное устройство содержит элемент ИЛИ-НЕ 1 счетного устройства, первый и второй формирователи импульсов 2, 3, содержащие резисторы 4, 5, конденсаторы 6, 7 и элементы И-НЕ, ИЛИ-НЕ 8, 9 соответственно, и N разрядов 10-1,. . . 10-N, каждый из которых содержит полусумматор 11-i, первый и второй элементы ИЛИ-НЕ 12-i, 13-i, магнитный сердечник 14-i с прямоугольной петлей гистерезиса и обмоткой, резистор 15-i и RS-триггер 16-i, выполненный на первом и втором элементах ИЛИ-НЕ 17-i, 18-i RS-триггера (где i=l, ... N). Счетное устройство имеет, вход начальной установки 19 и счетный вход 20.

Первый и второй входы элемента ИЛИ-НЕ 1 являются, соответственно, счетным входом 20 и входом начальной установки 19 устройства. В формирователе импульсов 2 первый вход элемента И-НЕ 8 соединен с первым выводом конденсатора 6 и вторым выводом резистора 4. Вторые выводы конденсаторов 6, 7 подключены к шине питания, первый вывод резистора 4, подключенный ко второму входу элемента И-НЕ 8 и к счетному входу устройства, является входом формирователя импульсов 2, а выходом его является выход элемента И-НЕ 8. В формирователе импульсов 3 первый вход элемента ИЛИ-НЕ 9 подключен к первому выводу конденсатора 7 и ко второму выводу резистора 5. Входом формирователя импульсов 3 является первый вывод резистора 5, соединенный с выходом элемента И-НЕ 8 и со вторым входом элемента ИЛИ-НЕ 9. Выход элемента ИЛИ-НЕ 9 соединен со вторым входом полусумматора 11-1 первого разряда 10-1 устройства и является выходом формирователя импульсов 3. Первый вход полусумматора 11-i каждого разряда i (где i=1, ... N) соединен с первым входом элемента ИЛИ-НЕ 17-i и с выходом элемента ИЛИ-НЕ 18-i, первый вход которого соединен с выходом элемента ИЛИ-НЕ 17-i, второй вход которого соединен с выходом элемента ИЛИ-НЕ 13-i. Элементы ИЛИ-НЕ 17-i, 18-i образуют RS-триггер 16-i, входами сброса и установки которого являются вторые входы элементов 18-i, 17-i, соответственно, а прямым выходом является выход элемента ИЛИ-НЕ 18-i. Первый вход элемента ИЛИ-НЕ 13-i каждого разряда подключен к началу обмотки магнитного сердечника 14-i с прямоугольной петлей гистерезиса, конец которой соединен с выходом элемента ИЛИ-НЕ 12-i, первый вход которого соединен с выходом полусумматора 11-i, со вторым входом элемента ИЛИ-НЕ 13-i и вторым выводом резистора 15-i, первый вывод которого подключен к средней точке обмотки магнитного сердечника 14-i. Вторые входы элементов ИЛИ-НЕ 12-i всех разрядов устройства объединены и подключены к выходу элемента ИЛИ-НЕ 1, вторые входы элементов 18-i всех разрядов устройства объединены и подключены к выходу элемента И-НЕ 8 формирователя импульсов 2. Выход переноса полусумматора 11-(j-1) каждого предыдущего разряда (где j=2, ... N) соединен со вторым входом полусумматора 11-j последующего разряда. Выходы элементов ИЛИ-НЕ 18-i каждого разряда являются выходами счетного устройства.

Счетное устройство работает следующим образом.

На вход 19 начальной установки устройства поступает импульс логической "1", который инвертируется элементом ИЛИ-НЕ 1 и поступает на входы элементов ИЛИ-НЕ 12-i каждого разряда 10-i (где i=l, ... N). На счетном входе 20 в это время присутствует уровень логического "0", который поступает на вход формирователя импульсов 2. Уровень логической "1" с его выхода поступает на входы сброса RS-триггеров 16-1, ..., 16-N, устанавливая на их выходе уровни логического "0", и на вход формирователя импульсов 3, который выдает на выходе уровень логического "0". При этом на выходе полусумматоров 11-1, ..., 11-N устанавливаются уровни логического "0", а на выходах элементов 12-1,..., 12-N - уровни логической "1". Магнитные сердечники с прямоугольной петлей гистерезиса и обмоткой 14-1, ..., 14-N перемагничиваются в начальное нулевое состояние. По окончании импульса начальной установки на выходах элементов 12-1, . . ., 12-N и полусумматоров 11-1, ..., 11-N формируются уровни логического "0", обмотки магнитных сердечников 14-1, .... 14-N обесточиваются и устройство переходит в режим хранения информации.

Первый счетный импульс поступает на счетный вход 20 в виде уровня логической "1" и вызывает появление на выходе элемента ИЛИ-НЕ 1 уровня логического "0", который поступает вторые входы элементов ИЛИ-НЕ 12-1,..., 12-N. При этом на выходе формирователей импульсов 2, 3 присутствуют уровни логической "1" и логического "0" соответственно. На выходах элементов ИЛИ-НЕ 18-1, ..., 18-N, на вторых входах и на выходах полусумматоров 11-1,..., 11-N устанавливаются уровни логического "0", что приводит к появлению уровня логической "1" на выходах элементов ИЛИ-НЕ 12-1,..., 12-N. При этом начинается процесс перемагничивания магнитных сердечников с прямоугольной петлей гистерезиса и обмоткой 14-1,..., 14-N в нулевое состояние. Но, так как они были перемагничены в нулевое состояние во время поступления импульса начальной установки, то на их выходах формируются лишь короткие импульсы помех, связанные с непрямоугольностью петли гистерезиса данных магнитных сердечников с обмоткой 14-1,..., 14-N. Данные импульсы, инвертированные элементами ИЛИ-НЕ 13-1, ..., 13-N, не приводят к переключению RS-триггеров 16-1,..., 16-N, так как на их входах сброса удерживается уровень логической "1" с выхода формирователя импульсов 2. Через время задержки, определяемое постоянной времени интегрирующей RC-цепи, состоящей из резистора 4 и конденсатора 6, которая превышает длительность импульса помехи от непрямоугольности петли гистерезиса, но меньше времени перемагничивания сердечников 14-1,..., 14-N, на выходе формирователя импульсов 2 происходит появление уровня логического "0", снимаются сигналы обнуления с входов сброса RS-триггеров 16-1,..., 16-N. На первых входах элементов ИЛИ-НЕ 13-1,..., 13-N присутствуют уровни логической "1", а на их выходах - уровни логического "0". Происходит запись информации из магнитных сердечников с обмоткой 14-1,..., 14-N в RS-триггеры 16-1, . . ., 16-N. Через время задержки, определяемое постоянной времени интегрирующей RC-цепи, состоящей из резистора 5 и конденсатора 7, и превышающей длительность времени переключения элементов 13-i, 17-i, 18-i (где i=1,. . . N), но меньше времени перемагничивания сердечников 14-1,..., 14-N, на выходе формирователя импульсов 3 появляется уровень логической "1", вызывающий появление уровня логической "1" на выходе полусумматора 11-1. На выходе элемента ИЛИ-НЕ 12-1 образуется уровень логического "0", что приводит к перемагничиванию сердечника с обмоткой 14-1 первого разряда устройства в состояние логической "1". По окончании первого счетного импульса на выходе формирователя 2 формируется уровень логической "1", а на выходе формирователя 3 - уровень логического "0", обмотки магнитных сердечников 14-1,..., 14-N обесточиваются и устройство переходит в режим хранения информации.

Второй счетный импульс поступает на счетный вход 20 в виде уровня логической "1" и вызывает появление на выходе элемента ИЛИ-НЕ 1 уровня логического "0", который поступает вторые входы элементов ИЛИ-НЕ 12-1,..., 12-N. На выходах элементов ИЛИ-НЕ 18-1,..., 18-N и на выходах полусумматоров 11-1, . . ., 11-N устанавливаются уровни логического "0", что приводит к появлению уровня логической "1" на выходах элементов ИЛИ-НЕ 12-1,..., 12-N. Начинается процесс перемагничивания магнитных сердечников с прямоугольной петлей гистерезиса и обмоткой 14-1, ..., 14-N в нулевое состояние. Так как сердечники 14-2,..., 14-N были перемагничены в нулевое состояние, то на их выходах формируются лишь короткие импульсы помех, связанные с непрямоугольностью петли гистерезиса. Через время задержки, определяемое формирователем импульсов 2, на его выходе появляется уровень логического "0", снимаются сигналы обнуления с входов сброса RS-триггеров 16-1,..., 16-N. На первом входе элемента ИЛИ-НЕ 13-1 присутствует уровни логического "0", а на его выходе - уровень логической "1". Происходит запись логической "1" из магнитного сердечника с обмоткой 14-1 в RS-триггер 16-1 через элемент ИЛИ-НЕ 13-1. Через время задержки, определяемое формирователем импульсов 3, на его выходе появляется уровень логической "1", вызывающий появление уровня логического "0" на выходе полусумматора 11-1, а на его выходе переноса - логической "1", который поступает на второй вход полусумматора 11-2 второго разряда. Это вызывает перемагничивание сердечника с обмоткой 14-2 в состояние логической "1", а сердечника 14-1 - в состояние логического "0". Сердечники 14-3,..., 14-N остаются в исходном нулевом состоянии. По окончании второго счетного импульса на выходе формирователя 2 формируется уровень логической "1", а на выходе формирователя 3 - уровень логического "0", обмотки магнитных сердечников 14-1, ..., 14-N обесточиваются и устройство переходит в режим хранения информации.

Далее устройство работает аналогично.

При реализации одного разряда счетного устройства на элементах серии 564, в прототипе используются два элемента 564ЛН2, по одному элементу 564ЛА9 и 564ЛЕ10, два элемента 564ЛА10, один триггер 564ТМ2. Для построения данных элементов требуется 70 транзисторов (Цифровые интегральные микросхемы: Справочник /П.П. Мальцев, Н.С. Долидзе, М.И. Критенко и др. - М.: Радио и связь, 1994. - 240 с., ил.). В предлагаемом устройстве один разряд может быть построен на четырех элементах 564ЛЕ5 (6 транзисторов в каждом) и полусумматоре, который может быть реализован (Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. - М.: Радио и связь, 1990. - 304 с.: ил.) на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 564ЛП2 и элементе совпадения И (реализуется на микросхеме 564ЛА7 и инверторе 564ЛН2). Данное построение предлагаемого счетного устройства требует 38 транзисторов для одного его разряда. Таким образом, достигнуто упрощение счетного устройства.

Изготовлен лабораторный макет счетного устройства, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта. Макет был выполнен на микросхемах серии 564 и на сердечниках из сплава АМАГ183. Время перемагничивания использованных сердечников - 20 мкс, время задержки, определяемое формирователем импульсов 2-5 мкс, а время задержки, определяемое формирователем импульсов 3-1 мкс.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207717C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 2002 |

|

RU2230427C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

| ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2038692C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 2001 |

|

RU2212096C2 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 2002 |

|

RU2208902C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 2003 |

|

RU2237355C1 |

| ЯЧЕЙКА ПАМЯТИ | 2001 |

|

RU2214037C2 |

| СЧЕТНОЕ УСТРОЙСТВО | 1992 |

|

RU2040113C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1995 |

|

RU2106742C1 |

Использование: в устройствах вычислительной техники и систем управления. Технический результат заключается в упрощении счетного устройства. Счетное устройство содержит элемент ИЛИ-НЕ счетного устройства, первый и второй формирователи импульсов, содержащие резисторы, конденсаторы и элементы И-НЕ, ИЛИ-НЕ соответственно, и N разрядов, каждый из которых содержит полусумматор, первый и второй элементы ИЛИ-НЕ, магнитный сердечник с прямоугольной петлей гистерезиса и обмоткой, резистор и RS-триггер. Счетное устройство имеет вход начальной установки и счетный вход. 1 ил.

Счетное устройство, содержащее счетный вход и вход начальной установки, два формирователя импульсов и N-разрядов, каждый из которых содержит ячейку памяти на магнитном сердечнике с прямоугольной петлей гистерезиса и обмоткой, средняя точка которой соединена с первым выводом резистора, отличающееся тем, что дополнительно введены логический элемент ИЛИ-НЕ счетного устройства, первый вход которого соединен со счетным входом счетного устройства, а второй вход - со входом начальной установки счетного устройства, в каждый разряд счетного устройства введены первый и второй логические элементы ИЛИ-НЕ, RS-триггер и полусумматор, первый вход которого соединен с прямым выходом RS-триггера, являющимся выходом счетного устройства, вход установки RS-триггера соединен с выходом второго логического элемента ИЛИ-НЕ, первый вход которого соединен с началом обмотки сердечника, конец которой соединен с выходом первого логического элемента ИЛИ-НЕ, первый вход которого соединен с выходом полусумматора, вторым выводом резистора и вторым входом второго логического элемента ИЛИ-НЕ, входы сброса RS-триггеров всех разрядов объединены и соединены с выходом первого формирователя импульсов и с входом второго формирователя импульсов, выход которого соединен со вторым входом полусумматора первого разряда, выход переноса которого соединен со вторым входом полусумматора последующего разряда, при этом вход первого формирователя импульсов соединен с первым входом логического элемента ИЛИ-НЕ счетного устройства, выход которого соединен с объединенными вторыми входами логических первых элементов ИЛИ-НЕ каждого разряда.

| СЧЕТНОЕ УСТРОЙСТВО | 1992 |

|

RU2040113C1 |

| ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2038692C1 |

| Счетчик импульсов, сохраняющий информацию при перерывах питания | 1985 |

|

SU1633490A1 |

| Счетное устройство сохраняющее информацию при перерывах питания | 1981 |

|

SU1051734A1 |

| Ограждение | 1987 |

|

SU1479596A1 |

Авторы

Даты

2003-06-27—Публикация

2001-11-01—Подача