Изобретение относится к вычислительной технике и может быть использовано для выполнения функциональных преобразований в различных цифровых системах обработки информации, например в бортовых системах летательных аппаратов.

Известные устройства [1,2] для кусочно-линейной интерполяции используют алгоритм вычисления функции по добавлению приращения ординаты на последующем отрезке относительно найденного аргумента узла к значению функции, соответствующему данному аргументу. При этом предварительно определяется порядок текущего значения аргумента функции интерполирования путем выделения целой части результата от деления разности текущего аргумента на соседних шагах интерполирования. Затем при собственно вычислении значения искомой функции коэффициент наклона на данном отрезке определяется путем деления разности ординат соседних шагов интерполирования на величину шага.

Из известных устройств за прототип выбрано устройство для кусочно-линейной интерполяции функций [2] содержащее регистр аргумента, регистр числа, сумматор, три регистра промежуточных значений, четыре коммутатора, блок памяти, блок микропрограммного управления, три элемента И и регистр признаков.

Недостатками данного устройства являются, во-первых, необходимость иметь постоянный шаг изменения аргумента (что не обязательно при малом изменении коэффициента наклона функции); во-вторых, вычисление коэффициента наклона при каждом интерполировании с применением длительной операции деления, что значительно увеличивает процесс интерполирования.

Целью изобретения является повышение быстродействия (за счет интерполирования с произвольной точки и исключения длительности операций выделения целой части и деления).

Значение функции Y устройство формирует в соответствии с выражением:

Y (X Xm) ˙Km + Ym, (1) где Х текущее значение аргумента;

Хm, Km, Ym соответственно аргумент, коэффициент наклона и ордината узла интерполяции;

m номер узла интерполяции, относительно которого осуществляется вычисление функции.

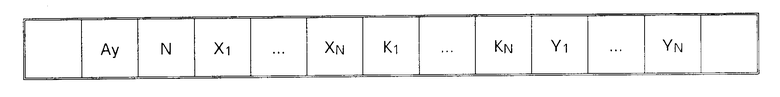

Параметры узлов интерполяции записываются в постоянном запоминающем устройстве в соответствии с таблицей

В таблице обозначено:

Ay адрес размещения в оперативном запоминающем устройстве (ОЗУ) вычисленного значения функции y;

N количество узлов интерполяции; Х1 Хn аргументы узлов интерполяции, причем

Х1 > Х2 >.> Хn;

К1 КN коэффициенты наклона, соответствующие узлу интерполяции;

Y1 Yn ординаты узлов интерполяции.

Адрес ячейки Aи ПЗУ, в которой размещается Ay, является начальной точкой таблицы интерполяции, относительно которого осуществляются все вычисления для определения параметров выражения (1).

Номер искомого узла m размещается в ОЗУ по адресу Aи + 1 (в соседней с Y ячейке).

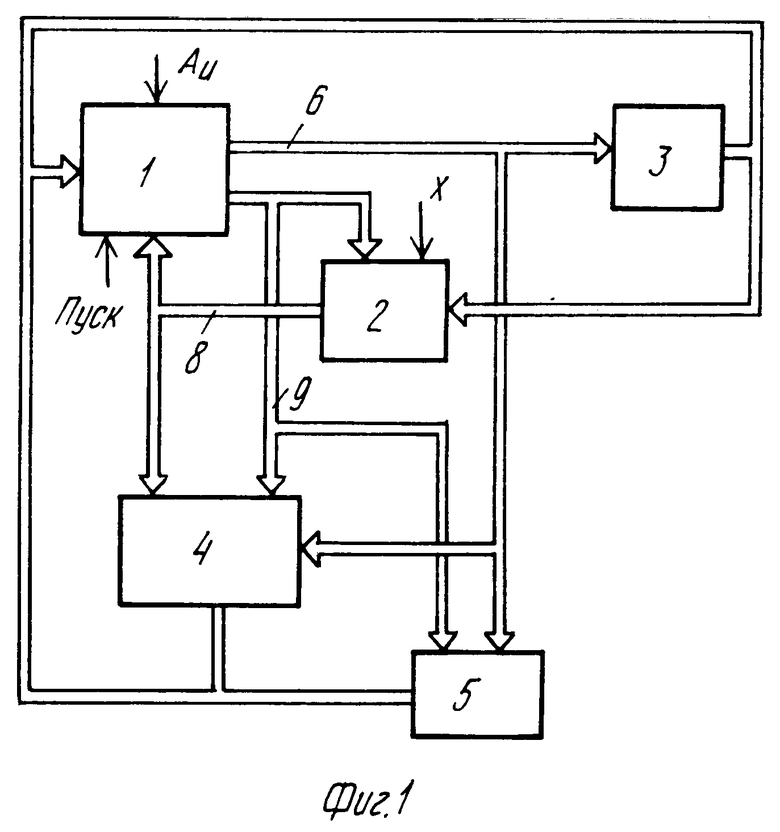

Устройство для интерполяции содержит блок 1 управления, вычислительный блок 2, постоянное запоминающее устройство 3, блок 4 счетчиков, блок 5 оперативной памяти.

Блок управления (фиг. 2) содержит регистр 7, формирователь 8 синхроимпульсов, восемь элементов ИЛИ 9-16, узлы 17, 18 элементов ИЛИ, узел 19 задания констант, коммутатор 20, узлы 21-28 элементов И и сумматор 29.

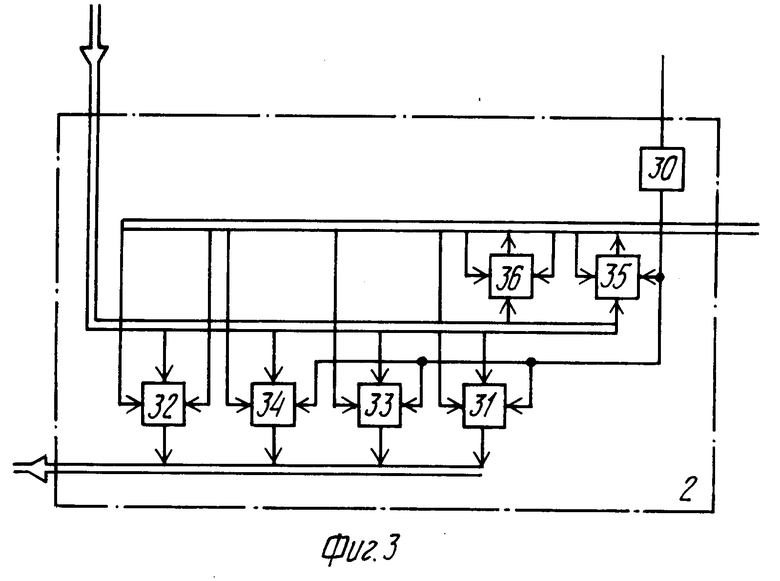

Вычислительный блок 2 (фиг. 3) содержит регистр 30, схемы сравнения 31-34, вычитатель 35 и умножитель 36.

Блок 4 счетчиков (фиг. 4) содержит регистры 37, 38 и узлы 39, 40 элементов ИЛИ.

Устройство работает следующим образом.

Предварительно в регистры блоков 1 и 2 записываются через первые входы соответственно начальный адрес таблицы Aи интерполяции и значение аргумента Х. По сигналу "Пуск" включается формирователь 8 синхроимпульсов (СИ).

По первому СИ, поступающему через элемент ИЛИ 9 на первый узла 21, содержимое регистра 7 через второй вход узла 21, первый вход узла элементов ИЛИ 18 поступает на первый вход сумматора 29. Одновременно с первого выхода узла 19 задания констант передается величина, равная двум единицам младшего разряда, через второй вход узла 22 и первый вход узла 17 элементов ИЛИ на второй вход сумматора 29. Выходной сигнал сумматора 29, равный смещенному (увеличенному) на 2 адресу Aи (начальный адрес таблицы интерполяции), через первый вход коммутатора 20, на второй вход которого поступает 1-й СИ, передается по магистрали на регистр адреса ПЗУ 3.

Выходной сигнал ПЗУ 3, соответствующий наибольшему значению аргумента Х1 таблицы интерполяции, по второй информационной магистрали поступает в блок 2 на первый вход первой схемы 31 сравнения, на втором входе которой присутствует содержимое регистра 30, равное значению входного аргумента.

По 2-му СИ, поступающему по синхромагистрали с выхода формирователя 8 синхроимпульсов на управляющий вход первой схемы 31 сравнения, формируется сигнал на выходе в зависимости от соотношения поступивших сигналов.

Если содержимое регистра 30 равно или больше сигнала, поступившего с выхода ПЗУ 3, т.е. Х ≥ Х1, то выходной сигнал схемы 31 сравнения будет равен нулю, и последовательность формирования синхроимпульсов в формирователе 8 не изменится.

При этом по 3-му СИ 3, поступающему на элемент ИЛИ 9, содержимое регистра 7 через узел 21 и узел 18 подается на первый вход сумматора 29. Одновременно с второго выхода узла 19 задания констант сигнал, равный одной единице младшего разряда, через второй вход узла 23, второй вход второго узла 17 элементов ИЛИ поступит на второй вход сумматора 29.

Выходной сигнал сумматора 29 через коммутатор 20 поступает в регистр адреса ПЗУ 3, с выхода которого величина, равная количеству узлов интерполяции (записанная по адресу AN Aи + 1), по 4-му СИ, поступающему по синхромагистрали на управляющий вход регистра 37, передается через первый вход первого узла 39 и записывается в регистр 37 блока 4 счетчиков.

По 5-му СИ, поступающему на первые входы узлов 21 и 22 через элементы ИЛИ 9 и 10 соответственно, на первый и второй входы сумматора 29 поступает через узел 21 и 18 содержимое регистра 7, а через узел 22 и узел 17 содержимое узла 19 задания констант, равное двум единицам младшего разряда. Таким образом, на выходе сумматора получается адрес Х1(Aи + 2), который через коммутатор 20 по информационной магистрали через второй узел 40 в присутствии 5-го СИ на управляющем входе 38 с выхода блока 1 по синхромагистрали заносится в регистр 38.

Шестой синхроимпульс через элементы ИЛИ 12 и 13 поступает на первые входы соответственно узлов 24 и 25.

При этом содержимое регистров 38 и 37 через второй вход узла 18 и третий вход узла 17 элементов ИЛИ поступает соответственно на первый и второй входы сумматора 29, выходной сигнал которого через коммутатор 20 по магистрали через второй вход узла 40 по заднему фронту 6-го СИ, поступающего по магистрали на управляющий вход, записывается в регистр 38.

По 7-му СИ аналогичным образом содержимое регистров 38 и 37 поступает на первый и второй входы сумматора 29, выходной сигнал которого передается по магистрали через коммутатор 20 на регистр адреса ПЗУ 3.

Этот сигнал равен адресу ординаты Y1, соответствующей аргументу Х1(Ay1 Aи + 2 + N + N).

Выходной сигнал ПЗУ 3, равный ординате Y1, по магистрали через первый вход узла 39 заносится в регистр 37.

По 8-му СИ, поступающему через элемент ИЛИ 9 на первый вход узла 21, содержимое регистра 7 через узел 21, узел 18 передается на первый вход сумматора 29.

При этом на второй вход сумматора 29 поступает нулевой сигнал с выхода узла 17 элементов ИЛИ. Поэтому выходной сигнал сумматора 29 равен величине Aи адрес таблицы интерполяции.

Этот сигнал через коммутатор 20 поступает на регистр адреса ПЗУЗ, на выходе которого выбирается содержимое ячейки с адресом Aи, т.е. адрес ячейки ОЗУ 5 для занесения значения ординаты.

По 9-му СИ адрес Aи с выхода ПЗУ 3 передается по магистрали через первый вход узла 40 на регистр 38 и одновременно на регистр адреса ОЗУ 5. В ячейку по выбранному адресу ОЗУ 5 заносится по магистрали содержимое регистра 37. Таким образом, в ОЗУ 5 оказывается занесена величина ординаты Y1.

По 10-му СИ аналогично описанному выше через элемент ИЛИ 12, узел 24, узел 18 содержимое регистра 38 поступает на первый вход сумматора 29. На второй вход при этом передается содержимое с второго выхода узла 19 (равное 1 ЕМР).

Таким образом, на выходе сумматора получится адрес ячейки ОЗУ для хранения текущего номера узла интерполяции. Выходной сигнал сумматора 29 через коммутатор 20 по магистрали поступает на регистр адреса ОЗУ 5, и по этому адресу через входную шину по 11-му СИ перепишется содержимое второго выхода узла 19 (т. е. 1 ЕМР), переданное в магистраль через схему И 23, узел 17, сумматор 29 и коммутатор 20.

После этого процесс интерполяции завершается, т.е. при значениях аргумента Х ≥ Х1 в ячейку ОЗУ 5 будет записано значение ординаты, равное Y1, а в следующую ячейку ОЗУ 5 номер узла, равный 1.

Если во время СИ 2 содержимое регистра 3, будет меньше выходного сигнала ПЗУ 3, т.е. Х < Х1, то выходной сигнал схемы 31 сравнения будет равен единице и, переданный по логической магистрали через второй вход формирователя синхроимпульсов, изменит последовательность формирования синхроимпульсов.

При этом после СИ 2 будет сфоpмирован 12-й СИ, подаваемый на элемент ИЛИ 9, по которому содержимое регистра 7 через узел 21, узел 18, сумматор 29, коммутатор 20 и магистраль поступит на регистр адреса ПЗУ 3. С выхода ПЗУ 3 адрес ячейки для записи ординаты Ay по магистрали через первый вход узла 39 по 13-му СИ, поданному по синхромагистрали на управляющий вход, запишется в регистр 37.

По 14-му СИ, переданному на первый вход узла 26, сигнал со второго выхода (1 ЕМР) узла 19 поступит на первый вход сумматор 29. Одновременно с выхода элемента ИЛИ 13 на второй вход сумматора поступит на регистр адреса ОЗУ 5.

Содержимое выходной шины ОЗУ 5 (номер узла m интерполяции, записанный в прошлом сеансе интерполяции) по магистрали через третий вход узла 40 по 15-му СИ запишется в регистр 38.

По 16-му СИ, поданному на элементы ИЛИ 9 и 11 в сумматоре 29 осуществится сложение содержимого регистра 7 (Aи) и сигнала с второго выхода узла 19 (1 ЕМР), поступивших на первый и второй входы сумматора 29 описанным способом, и выходной сигнал сумматора 29 (AN) через коммутатор 20 по магистрали будет передан в регистр адреса ПЗУ 3 и через второй вход узла 29 в регистр 37.

По 17-му СИ, поданному на входы сумматора 29, поступит содержимое регистров 38 и 37.

Выходной сигнал сумматора, равный адресу аргументов таблицы интерполяции для узла m (Axm m + AN), через коммутатор 20 по магистрали будет записан в регистр 37.

По 18-му СИ в регистр адреса ПЗУ 3 передается по первой магистрали 6 выходной сигнал коммутатора 20, равный сумме содержимого регистра 7 и сигнала со второго выхода узла 19. Этот сигнал определяет адрес ячейки количества узлов интерполяции.

По 19-му СИ осуществляется сравнение выходного сигнала ПЗУ 3 и содержимого регистра 38 во второй схеме 32 сравнения. Если выходной сигнал схемы 32 сравнения равен нулю, то по 20-му СИ на регистр адреса ПЗУ 3 по магистрали через коммутатор 20 будет передан адрес аргумента следующего узла (Axm + 1) с выхода сумматора 29.

По 21-му СИ, переданному на управляющий вход третьей схемы 33 сравнения, осуществляется сравнение содержимого регистра 30, подаваемого на первый ее вход, и поступающего на второй вход по логической магистрали выходного сигнала ПЗУ 3.

При этом, если выходной сигнал ПЗУ 3 больше содержимого регистра 30, то единичный сигнал на выходе схемы 33 сравнения поступает по логической магистрали на инкрементные (+) входы регистров 37 и 38, увеличивая их содержимое на единицу. Одновременно сигнал с выхода схемы 33 сравнения по магистрали поступает на третий вход формирователя 8 синхроимпульсов и после окончания СИ снова начинает формировать 18-й СИ.

Если содержимое pегистра 30 больше или равно выходному сигналу ПЗУ 3 (Х ≥ Хm+1) во время действия 21-го СИ, то выходной сигнал схемы 33 сравнения равен нулю и ход следования синхроимпульсов не нарушается.

По 22-му СИ, подаваемому на элемент ИЛИ 13, содержимое регистра 37 по магистрали поступает на регистр адреса ПЗУ 3 и по 23-му СИ выходной сигнал ПЗУ 3 в четвертой схеме 34 сравнения сравнивается с содержимым регистра 30.

Если содержимое регистра 30 больше выходного сигнала ПЗУ 3, то вырабатывается единичный сигнал на выходе схемы 34 сравнения и поступает по логической магистрали на декрементные (-) входы регистров 37 и 38, уменьшая их содержимое на единицу. Одновременно сигнал с выхода схемы 34 сравнения поступит на четвертый вход формирователя 8 синхроимпульсов. При этом после окончания 23-го СИ снова будет формироваться 22-й СИ.

Если во время действия 23-го СИ содержимое регистра 30 окажется меньше выходного сигнала ПЗУ 3 (Х < Хm), то ход следования синхроимпульсов не нарушается.

По СИ 24 содержимое регистра 7 через схему И 21, узел 18 элементов ИЛИ, коммутатор 20 по магистрали передается в регистр адресу ПЗУ 3.

По СИ к выходному сигналу ПЗУ 3 (адрес хранения выходной ординаты Ay, подаваемому через схему И 27 и четвертый вход элемента ИЛИ 18 на первый вход сумматора 29, добавляется единица со второго выхода блока 19 задания констант, подаваемая через схему И 23, элемент ИЛИ 17 на второй вход сумматора 29, выходной сигнал которого через коммутатор 20 по магистрали поступает на регистр адреса ОЗУ 5 (адрес хранения номер m узла интерполяции).

По СИ 26 в эту ячейку ОЗУ 5 заносится через входную шину содержимое регистра 38.

По СИ 27 содержимое регистра 37 (адрес Axm) записывается в регистр адреса ПЗУ 3.

По СИ 28 на управляющем входе блока 35 вычитания из содержимого регистра 30 вычитается выходной сигнал ПЗУ 3, поступающий на втоpой вход блока 35 вычитания по магистрали, и результат записывается в регистp 38.

По СИ 29 содержимое регистра 7 и сигнал второго выхода узла 19 задания констант поступают на входы сумматора 29. Результат сложения (адрес AN) через коммутатор 20 по магистрали 6 передается на регистр адреса ПЗУ 3.

По СИ 30 выходной сигнал ПЗУ 3 (количество узлов N интерполяции) через узел И 27, ИЛИ 18 и содержимое регистра 37 (адрес Axm) поступают соответственно на первый и второй входы сумматора 29, выходной сигнал которого (адрес коэффициента наклона Axm) через коммутатор 20 по магистрали 6 передается в регистр адреса ПЗУ 3 и одновременно записывается в регистр 37.

По СИ 31, подаваемому на управляющий вход блока 36 умножения, перемножаются выходной сигнал ПЗУ 3 (коэффициент наклона Xm) и содержимое регистра 38 (разность Х -Хm), поступающие по магистрали. После завершения операции результат умножения записывается в регистр 38.

По СИ 32 на регистре адреса ПЗУ 32 на регистре адреса ПЗУ 3 записывается адрес AN (аналогично ситуации действия СИ 29).

По СИ 33, поступающему на элементы ИЛИ 16 и 13, на регистре адреса ПЗУ 3 записывается адрес ординаты узла AYm (аналогично действию СИ 30).

По СИ 34 выходной сигнал Ym ПЗУ 3 и содержимое регистра 38 поступают соответственно первый и второй входы сумматора 29. Выходной сигнал сумматора 29 записывается в регистр 38.

По СИ 35, поступающему на схему ИЛИ 9, аналогично СИ24, содержимое регистра 7 записывается в регистр адреса ПЗУ 3.

По СИ 36 выходной сигнал ПЗУ 3 поступает по магистрали на регистр адреса ОЗУ 5 и содержимое регистра 38 записывается через входную шину ОЗУ 5 по этому адресу. На этом заканчивается полный цикл интерполяции.

Таким образом, как видно из описания алгоритма, а основном вычисления сводятся к работе по определению адресов параметров интерполяции в таблице ПЗУ путем сравнения текущего аргумента со значениями аргументов, расположенных справа и слева от угла на предыдущем сеансе интерполяции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2233552C2 |

| Устройство для вычисления коэффициентов интерполирующего полинома | 1990 |

|

SU1748158A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА | 1991 |

|

RU2006917C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| СПОСОБ КОНТРОЛЯ И ОТЛАДКИ ПРОГРАММ РЕАЛЬНОГО ВРЕМЕНИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2050588C1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

Устройство для интерполяции относится к вычислительной технике и предназначено для выполнения функциональных преобразований в различных цифровых системах обработки информации, например в бортовых системах ЛА. Цель изобретения повышение быстродействия. Устройство для интерполяции содержит блок 1 управления, вычислительный блок 2, постоянное запоминающее устройство 3, блок 4 счетчиков, блок 5 оперативной памяти. Повышение быстродействия достигается за счет интерполирования с произвольной точки и исключения длительных операций выделения целой части и деления. 1 з.п. ф-лы, 4 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для кусочно-линейной интерполяции функций | 1983 |

|

SU1215117A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-08-27—Публикация

1990-07-04—Подача