Изобретение относится к вычислительной технике и может быть использовано для выполнения функциональных преобразований в различных цифровых системах обработки информации

Целью изобретения является повышение быстродействия за счет интерполирования с произвольной точки.

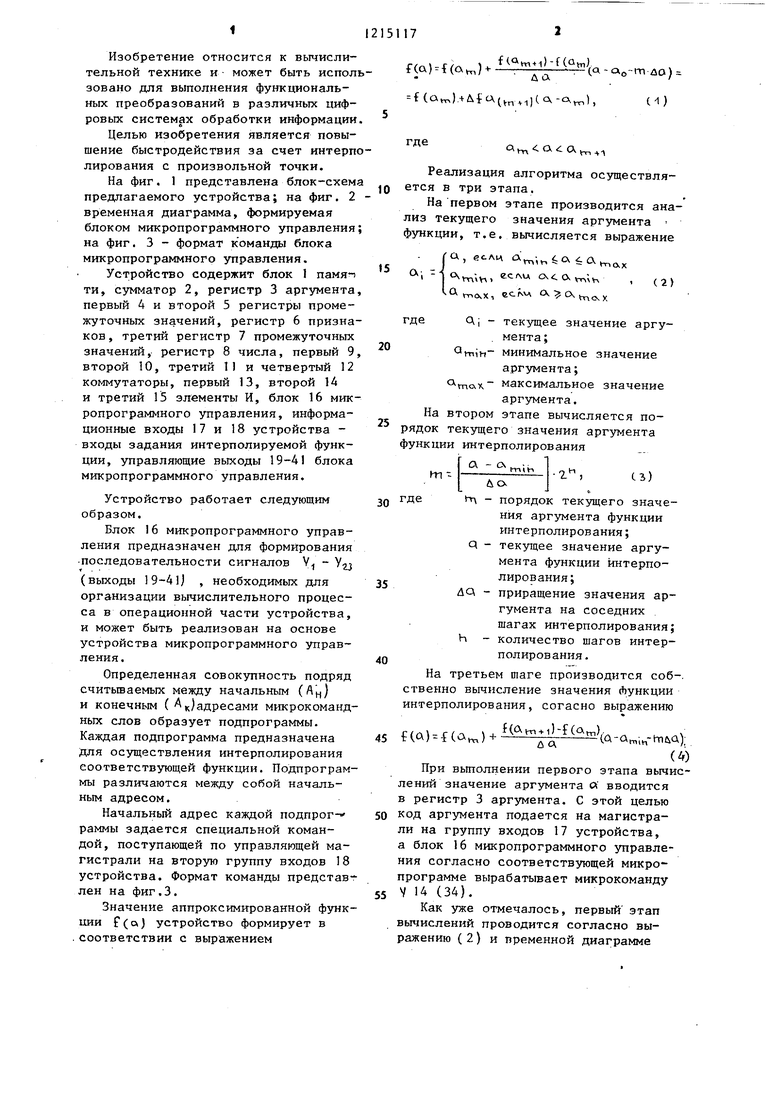

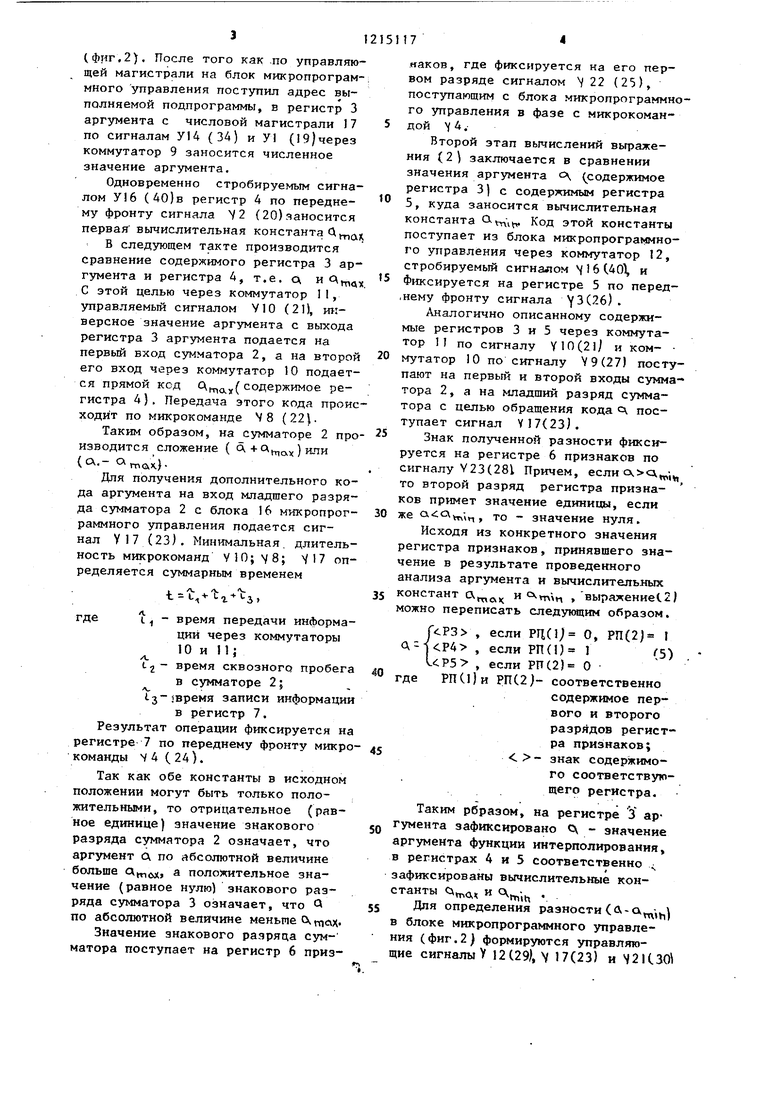

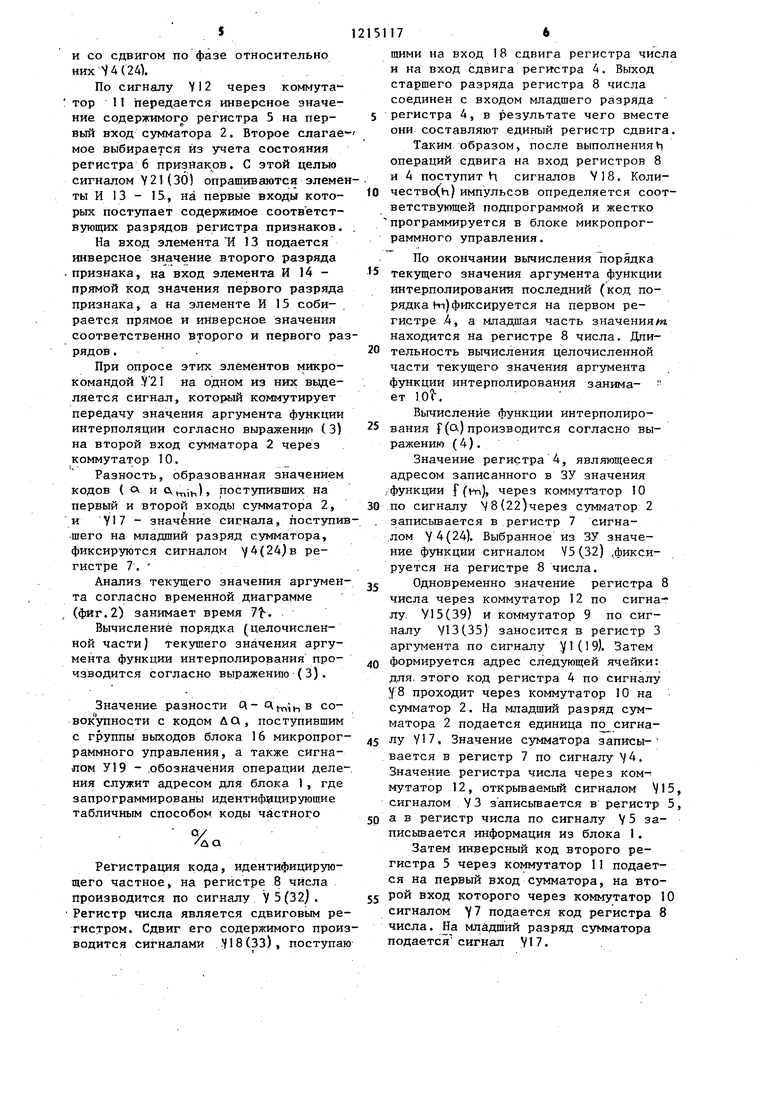

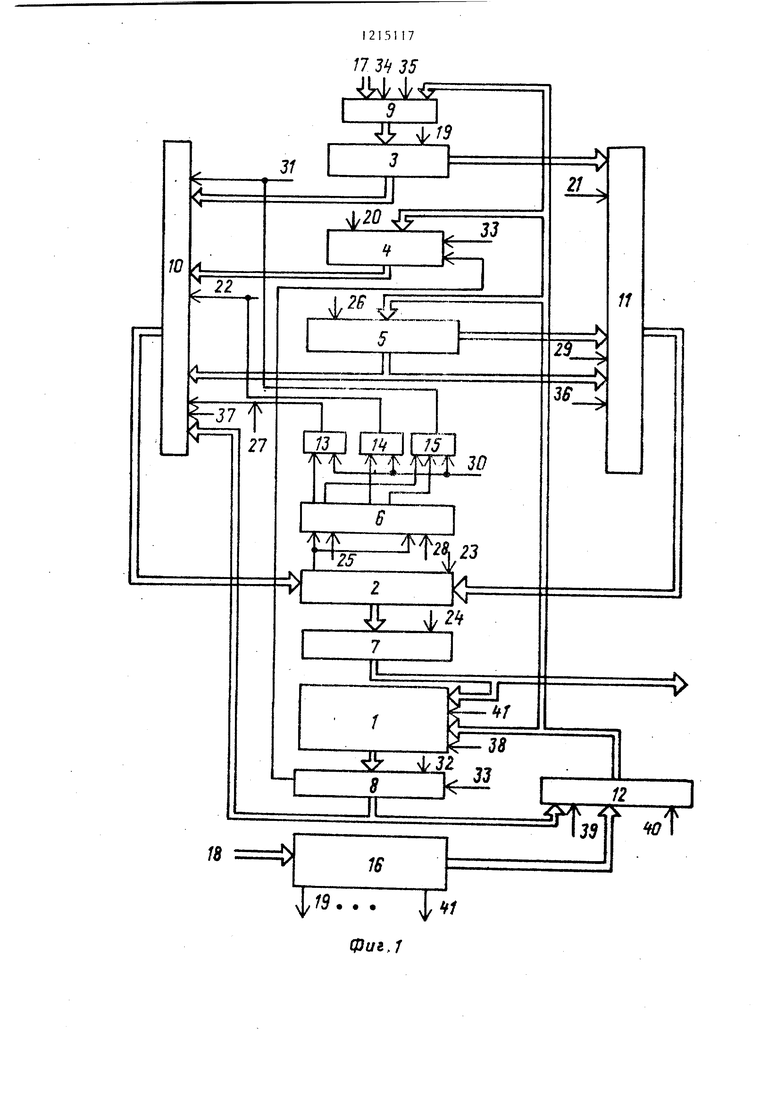

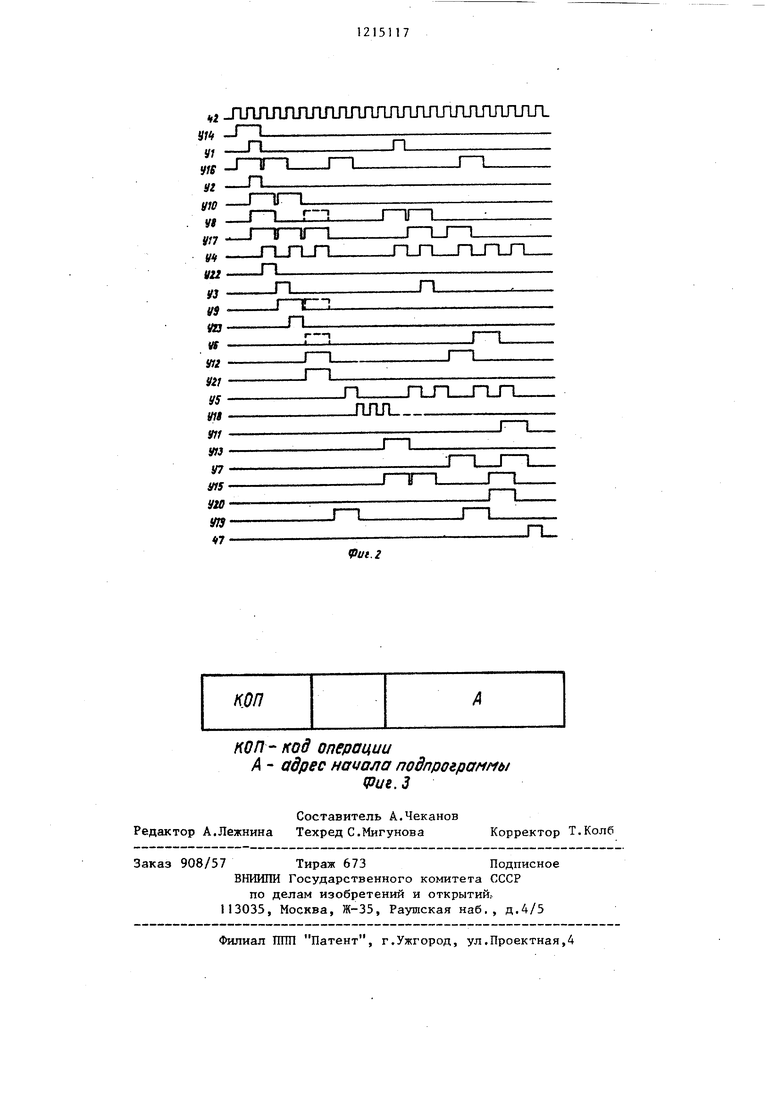

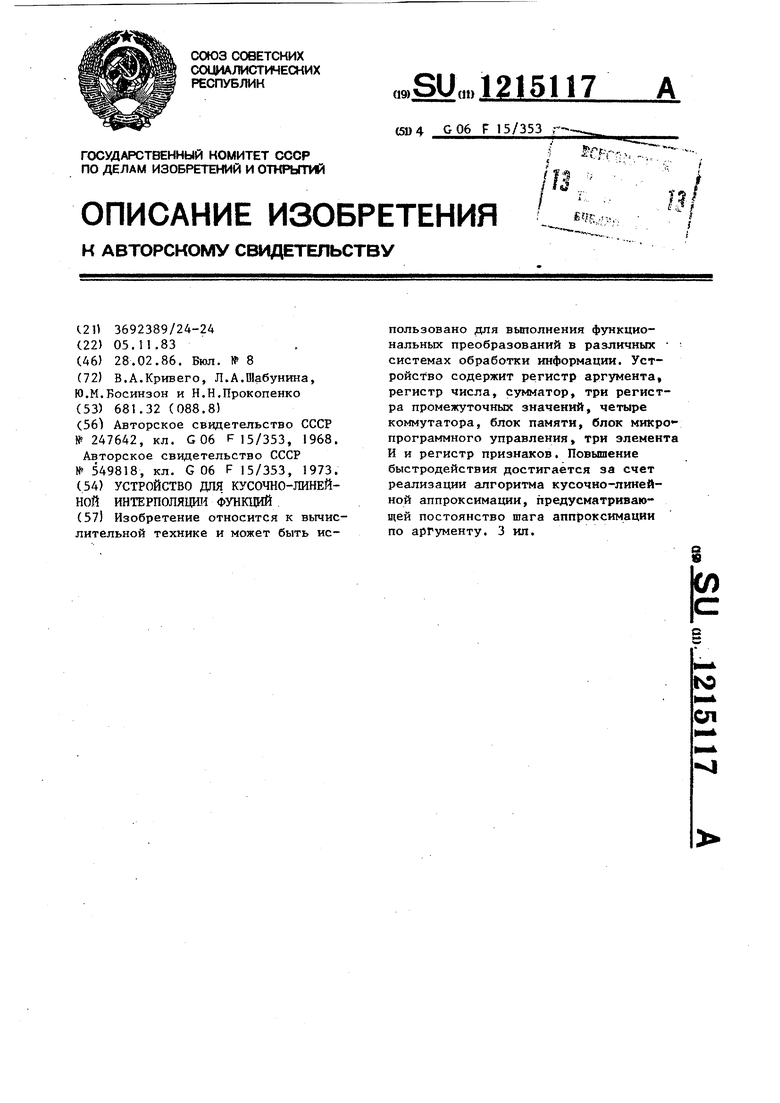

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 временная диаграмма, формируемая блоком микропрограммного управления на фиг. 3 - формат к оманды блока микропрограммного управления.

Устройство содержит блок 1 памя-5 ти, сумматор 2, регистр 3 аргумента первый 4 и второй 5 регистры промежуточных значений, регистр 6 признаков , третий регистр 7 промежуточных значений, регистр 8 числа, первый 9 второй 10, третий 11 и четвертый 12 коммутаторы, первый 13, второй 14 и третий 15 элементы И, блок 16 микропрограммного управления, информационные входы 17 и 18 устройства - входы задания интерполируемой функции, управляющие выходы 19-41 блока микропрограммного управления.

Устройство работает следующим образом.

Блок 16 микропрограммного управления предназначен для формирования последовательности сигналов V - У

(выходы 19-4) , необходимых для организации вычислительного процесса в операционной части устройства, и может быть реализован на основе устройства микропрограммного управления .

Определенная совокупность подряд считьшаемых между начальным (А ) и конечным (А)адресами микрокоманд- ньпс слов образует подпрограммы. Каждая подпрограмма предназначена Для осуществления интерполирования соответствующей функции. Подпрограммы различаются между собой начальным адресом.

Начальный адрес каждой подпрог-- раммы задается специальной командой, поступающей по управляющей магистрали на вторую группу входов 18 устройства. Формат команды представ- лен на фиг.З.

Значение аппроксимированной функции f(а) устройство формирует в . соответствии с выражением

ГСгл С/ f )-f(Qtn)

f(a)-f (,,; (a-ao-m ло):

да

f (а).+ Д{ сл(„,)(сх-а),

(Я

где

.,

Реализация алгоритма осуществля- ется в три этапа.

На первом этапе производится анализ текущего значения аргумента функции, т.е. вычисляется выражение

ja, если , . счса,; ,x, c CXtncsx

(2)

где

Qj - текущее значение аргумента ; min- минимальное значение

аргумента; mckX максимальное значение

аргумента.

На втором этапе вычисляется порядок текущего значения аргумента функции интерполирования

Ж г,

-h

UCX

Ci)

где

т - порядок текущего значения аргумента функции интерполирования; о. - текущее значение аргумента функции интерполирования;

дс - приращение значения аргумента на соседних щагах интерполирования;

h - количество щагов интерполирования.

На третьем шаге производится соб-. ственно вычисление значения Аункции интерполирования, согасно выражению

f(a)-f(a),):

(4)

При выполнении первого этапа вычислений значение аргумента « вводится в регистр 3 аргумента. С этой целью код аргумента подается на магистрали на группу входов 17 устройства, а блок 16 микропрограммного управления согласно соответствующей микропрограмме вырабатывает микрокоманду V 14 (34).

Как уже отмечалось, первый этап вычислений проводится согласно выражению ( 2) и временной диаграмме

(фиг.2). После того как .по управляющей магистрали на блок микропрограммного управления поступил адрес выполняемой подпрограммы, в регистр 3 аргумента с числовой магистрали 17 по сигналам (ЗА) и У1 (19)через коммутатор 9 заносится численное значение аргумента.

Одновременно стробируемым сигналом У16 (40)в регистр 4 по передне- му фронту сигнала V2 (20)заносится первая вычислительная константа о

В следующем такте производится сравнение содержимого регистра 3 аргумента и регистра 4, т.е. а и С этой целью через коммутатор I1, управляемый сигналом V10 (21), ик- версное значение аргумента с выхода регистра 3 аргумента подается на первый вход сумматора 2, а на второй его вход через коммутатор 10 подается прямой код та( содержимое регистра 4). Передача этого кода происходит по микрокоманде V8 (22|.

Таким образом, на сумматоре 2 про изводится сложение ( + с ) или (а,- ,.

Для получения дополнительного кода аргумента на вход младшего разряда сумматора 2 с блока 16 микропрог- раммного управления подается сигнал Y17 (23). Минимальная, длительность микрокоманд V10; V8; V17 определяется суммарным временем

,гг.гз,

где

1 - время передачи информации через коммутаторы 10 и llj Lj время сквозного пробега

в сумматоре 2 ; , 1з время записи информации

в регистр 7.

Результат операции фиксируется на регистре 7 по переднему фронту микро команды V 4 (24).

Так как обе константы в исходном положении могут быть только положительными, то отрицательное (равное единице) значение знакового разряда сумматора 2 означает, что аргумент сх по абсолютной величине больше (, а положительное значение (равное нулю) знакового разряда сумматора 3 означает, что Q по абсолютной величине меньше сх, . Значение знакового разряца сумматора поступает на регистр 6 приз5

5 20 25

30

35

40

45

50 55

,

.наков, где фгжсируется на его первом разряде сигналом V 22 (25), поступающим с блока микропрограммного управления в фазе с микрокомандой V4.Второй этап вычислений выражения (2) заключается в сравнении значения аргумента с (содержимое регистра 3) с содерткимым регистра 5, куда заносится вычислительная константа О Код этой константы поступает из блока микропрограммного управления через коммутатор 12, стробируемый сигналом V16 С40 и Фиксируется на регистре 5 по перед- .нему фронту сигнала (26).

Аналогично описанному содержимые регистров 3 и 5 через коммутатор П по сигналу Y10(2U и ком- мутатор 10 по сигналу V9(27) поступают на nepBbrii и второй входы сумматора 2, а на младший разряд сумматора с целью обращения кода с поступает сигнал V17(23).

Знак полученной разности фиксируется на регистре 6 признаков по сигналу V23(28l Причем, если ,, то второй разряд регистра признаков примет значение единицы, если же o.cVvTv n то - значение нуля.

Исходя из конкретного значения регистра признаков, принявшего значение в результате проведенного анализа аргумента и вычислительных констант и л. , выражение(.2) можно переписать следующим образом.

ГсРЗ , если Pri(i; О, Pn(2j I , если РП()« 1 (5)

UP5 , если РП(2) О где РПС1)и РПС2)- соответственно

содержимое первого и второго разрядов регистра признаков; - знак содержимого cooTBeTCTBjTo- щего регистра.

Таким рбразом, на регистре З аргумента зафиксировано с - значение аргумента функции интерполирования, в регистрах 4 и 5 соответственно зафиксированы вычислительные константы и cv. ,

Для определения разности (Л-а,-,) в блоке микропрограммного управления (фиг.2) формируются управляющие сигналыУ 12(29), V 17(23) и V2K30

S

и со сдвигом по фазе относительно них 4 (24).

По сигналу V12 через KOMNtyTa - тор 11 передается инверсное значение содержимого регистра 5 на первый вход сумматора 2. Второе слагаемое выбирается из учета состояния регистра 6 признаков. С этой целью сигналом Y 21(30) опрашиваются элементы И 13 - 15, на первые входы которых поступает содержимое соответствующих разрядов регистра признаков.

На вход элемента И 13 подается инверсное значение второго разряда признака, на вход элемента И 14 - прямой код значения первого разряда признака, а на элементе И 15 собирается прямое и инверсное значения соответственно второго и первого разрядов , .

При опросе этих элементов микрокомандой -V 21 на одном из них вьще- ляется сигнал, кото1м 1й коммутирует передачу значения аргумента функции интерполяции согласно выражению (3) на второй вход сумматора 2 через коммутатор 10.

Разность, образованная значением кодов ( л и Ck,i), поступивших на первый и второй входы сумматора 2, и Y17 - значение сигнала, поступив шего на младший разряд сумматора, фиксируются сигналом у4(24)в регистре 7.

Анализ текущего значения аргумента согласно временной диаграмме (фиг.2) занимает время 7.

Вычисление порядка (целочисленной части) текущего значения аргумента функции интерполирования производится согласно выражению (3).

Значение разности й- ° вокупности с кодом да, поступившим с группы выходов блока 16 микропрограммного управления, а также сигналом У19 - .обозначения операции деления служит адресом для блока 1, где запрограммированы идентифицирующие табличным способом коды частного

Q/ /л

да

Регистрация кода, идентифицирующего частное, на регистре 8 числа производится по сигналу У 5 (32,). Регистр числа является сдвиговым регистром. Сдвиг его содержимого производится сигналами ,V18(33), поступаю

15117

щими на вход 18 сдвига регистра числа и на вход сдвига регистра 4. Выход старшего разряда регистра 8 числа соединен с входом младшего разряда 5 регистра 4, в результате чего вместе они составляют единый регистр сдвига.

Таким образом, после выполненияh операций сдвига на вход регистров 8 и 4 поступит И сигналов V18. Коли- iO чество(и) импульсов определяется соответствующей подпрограммой и жестко программируется в блоке микропрограммного управления.

По окончании вычисления порядка

15 текущего значения аргз мента функции интерполирования последний (код порядка Hi) фиксируется на первом регистре .4, а младшая часть значения/л находится на регистре 8 числа. Дли20 тельноеть вычисления целочисленной части текущего значения аргумента функции интерполирования занима- ет 10.

Вычисление функции интерполиро25 вания f(cx) производится согласно выражению (4).

Значение регистра 4, являющееся адресом записанного в ЗУ значения /функции f (VYI), через коммутатор 10

30 по сигналу V8(22)4epe3 сумматор 2 . записывается в регистр 7 сигна- .лом У4(24). Выбранное из ЗУ значение функции сигналом V5 (32) .фиксируется на регистре 8 числа.

35 Одновременно значение регистра 8 числа через коммутатор 12 по сигналу. VI5(39) и коммутатор 9 по сигналу VI3(35) заносится в регистр 3 аргумента по сигналу У1 (19). Затем

40 формируется адрес следующей ячейки: для. этого код регистра 4 по сигналу У 8 проходит через коммутатор 10 на сумматор 2. На младший разряд сумматора 2 подается единица по сигна45 лу У17, Значение сумматора записы- вается в регистр 7 по сигналу У4. Значение регистра числа через ком- мутатор 12, открываемый сигналом V13, сигналом V 3 записьшается в регистр 5,

50 а в регистр числа по сигналу У 5 записывается информация из блока 1.

Затем инверсный код второго регистра 5 через коммутатор 11 подается на первый вход сумматора, на вто55 рой вход которого через коммутатор 10 сигналом у 7 подается код регистра 8 числа. На младший разряд сумматора подается сигнал У17.

Результат вычитания записывается в регистр 7 сигналом У4. Значение это й разности в совокупности с ко- дом Да, поступившим из накопите- ля блока микропрограммного управления по сигналу V16, слз жит адресом для блока 1. На выходе блока 1 получаем частное от деления разности на Д СХ , частное записывается в ре- гистр 8 числа по сигналу У.5.

Значение регистра 3 аргумента через коммутатор 10 по сиг напу У15 через сз мматор 2- записьгоается в регистр 7 сигналом Y 4.

Таким образом, на адресный вход блока 1 поступает код регистра 7, код регистра числа через ком -гутатор 12 и признак операции умножения - сигнал V2p. Результат записьюается в регистр 8 -числа.

Проводится последний этап - суммирование содержимого регистра 5, которое через коммутатор 11 по сиг- .налу V11 подается на первый вход сумматора 2, и содержимого регистра числа, которое через коммутатор 10 по сигналу Y7 подается на второй вход сумматора. Результат фиксируется в регистре 7. Этот результат представляет собой функцию f(а).

Форм ула изобретени

Устройство для кусочно-линейной интерполяции функций, содержащее рег.истр аргумента, регистр числа и сумматор, отличающееся тем, что, с цeлькf повышения быстродействия за счет интерполирования с произвольной точки, оно содержит тр регистра промежуточных значений, че тыре коммутатора, блок памяти, блок микропрограммного управления, три элемента И и регистр признаков, причем информационные входы устройс ва соединены с первой группой информационных входов первого коммутатора, выходы которого соединены с. информационными входами регистра аргумента, прямые выходы которого соединены с первой группой информационных- входов второго коммутатора, а инверсные - с первой группой информационных входов третьего коммутатора, вторая группа информацион ных входов коммутатора соединена с выходами первого регистра промежу точного результата, прямьте выходы

второго регистра промежуточного результата подключены к третьей группе информационных входов второго коммутатора и второй группе информационных входов третьего коммутатора, третья группа информационных входов которо го подключена к инверсным выходам второго регистра промежуточного результата, выходы второго и третьего коммутаторов соединены соответственно с входами первого и второго слагаемьп сумматоров, выходы которых соединены с информационными входами третьего-регистра про- межуточного результата, выходы которого соединены с выходами устройства и с входами младших разрядов адреса блока памяти, выходы которого соединены с информационными входами регистра числа, выходы которого соединены с четвертой группой информационных: входов второго коммутатора и первой группы информационных входов четвертого коммутатора, выходы которого соединены с второй группой информационных входов первого коммутатора, информационными входами первого и второго регистров троме- жуточных результатов и входами старших разрядов адреса блока памяти, входы задания интерполируемой функции устройства соединены с входами начального адреса блока микропрограммного управления, выходы шага аргумента которого соединены с второй группой информационных входов четвертого коммутатора, выход переноса с 11матора соединен с информационными входами регистра признаков выходы первого, второго и третьего элементов И соединены соответственно с первым, вторым и третьим управ ляющим1т входами второго коммутатора прямой выход первого разряда регистра признаков соединен с первым входом второ го элемента И, инверсный выход второго разряда регистра признаков соединен с первым входом первого элемента И, прямой выход второго разряда и инверсный выход первого разряда регистра признаков соединены соответственно с первым и вторым входами третьего элемента И, первый и второй управляющие выходы блока микропрограммного управления соединены с входами управления параллельной записью регистра аргумента и первого регистра промежуточных значений соответственно, третий и четвертьй управляющие выходы блока микропрограммного управления соединены с первым управляющим входом третьего коммутатора и четвертым управляющим входом второго коммутатора соответственно, с пятого по восьмой управляющие выходы блока микропрограммного управления соединены соответственно с входом переноса сумматора-,и выходами синхронизации третьего регистра промежуточных результатов, первого разряда регистра признаков и второго регистра промежуточных результатов соответственно, девятый управляющий выход блока микропрограммного управления соединен с пятым управляющим входом второго коммутатора, десятый управляющий выход блока микропрограммного управления соединен с входом синхронизации второго разряда регистра признаков, одиннадцатый управляющий выход блока микропрограммного управления соединен с вторым управляющим входом третьего коммутатора, двенадцатый управляющий выход блока микропрограммного управления соединен с вторыми входами первого и второго элементов И и третьим входом третьего элемента И, тринадцатый управляющий выход блока микропрограммного управления соединен с шестым управляющим входом второго коммутатора, четьфнадцатый управляющий выход блока микропрограммного управления соединен с. входом управления параллельной за- писью регистра числа, а пятнадцатый - с входом управления сдвигом регистра числа и первого регистра промежуточных результатов, шестнадцатый и семнадцатый управляющие

выходы блока микропрограммного управления соединены с первым и вторым соответственно управляющими входами первого коммутатора, восем- - надцатый управляющий выход блока

микропрограммного управления соединен с третьим управляющим входом третьего коммутатора, девятнадцатый управляющий выход блока микропрограммного управления соединен с седьмь1м управляющим входом второго коммутатора, двадцатый управляющий выход блока микропрограммного управления соединен с первь1м входом базового адреса блока памяти, двадцать

первый и двадцать второй управляющие выходы блока микропрограммного управления соединены с первым и вторым соответственно управлякяцими входами четвертого коммутатора,

двадцать третий управляюпшй выход блока микропрограммного управления соединен с вторым входом базового адреса блока памяти, выход переноса регистра числа соединен с входом переноса первого регистра промежуточных результатов .

... Фиг.Г

Л J 35

lnJmrumгLЛЯJшnJUlnягlллJlГLл

TL

п

Tl

.

f-L.

п

.

f-L.

| название | год | авторы | номер документа |

|---|---|---|---|

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Микропроцессор | 1981 |

|

SU1012266A1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| УСТРОЙСТВО ДЛЯ ИНТЕРПОЛЯЦИИ | 1990 |

|

RU2042979C1 |

| Система для выполнения команд десятичной арифметики табличным способом | 1981 |

|

SU1027731A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Устройство для извлечения корня @ -й степени | 1984 |

|

SU1223225A2 |

Изобретение относится к вычислительной технике и может быть использовано для вьтолнения функциональных преобразований в различных - системах обработки информации. Устройство содержит регистр аргумента, регистр числа, сумматор, три регистра промежуточных значений, четыре коммутатора, блок памяти, блок микропрограммного управления, три элемента И и регистр признаков. Повышение быстродействия достигается за счет реализации алгоритма кусочно-лиией- ной аппроксимации, предусматривающей постоянство шага аппроксимации по аргументу. 3 ил. 5 В

KOn- код операции A - адрес начала подпрограммы (Риг. 3

Составитель А.Чеканов Редактор А.Лежнина Техред С.Мигунова

Заказ 908/57 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий. 113035, Москва, Ж-35, Раушская наб,, д.4/5

Филиал ППП Патент, г.Ужгород, ул.Проектная,4

Корректор Т.Колб

| ЦИФРОВОЙ КУСОЧНО-ЛИНЕЙНЫЙ АППРОКСИМАТОР | 0 |

|

SU247642A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой кусочно-линейный аппроксиматор | 1973 |

|

SU549818A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-28—Публикация

1983-11-05—Подача