Изобретение относится к компьютерной технике и может быть использовано в качестве сопроцессора для персональных компьютеров с целью повышения их производительности при выполнении векторных операций.

Известно арифметическое устройство [1] для выполнения параллельных вычислений векторных величин, содержащее три блока векторных регистров, соединенных с тремя блоками формирования адресов, причем блоки векторных регистров соединены с двумя арифметическими блоками, каждый из которых содержит умножитель, АЛУ и регистр.

Недостатком данного устройства являются больше потери времени на перезагрузку векторных регистров из внешней памяти.

Наиболее близким по технической сущности решением к предложенному является векторный процессор [2] содержащий арифметический блок, блок векторных регистров, ОЗУ данных, адресное АЛУ и блок управления, соединенный с ОЗУ данных и адресным АЛУ.

Известное устройство не обеспечивает высокого быстродействия вследствие затрат времени на загрузку векторных регистров из ОЗУ данных и загрузку в него результатов выполнения векторных операций.

Предлагаемое техническое решение позволяет повысить быстродействие за счет исключения потерь на перезагрузку векторных регистров, так как в предлагаемом устройстве использованы вместо векторных регистpов дополнительные блоки формирования адресов и быстродействующая память.

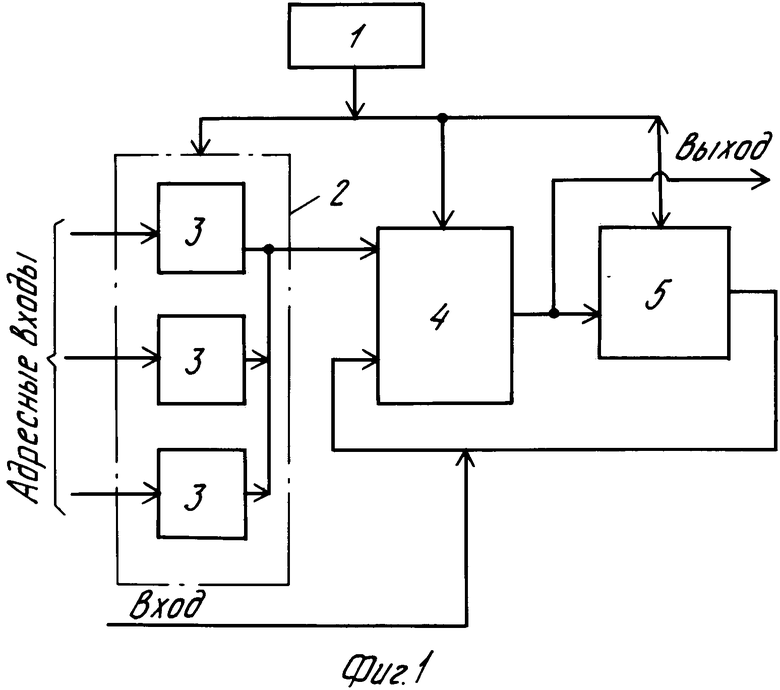

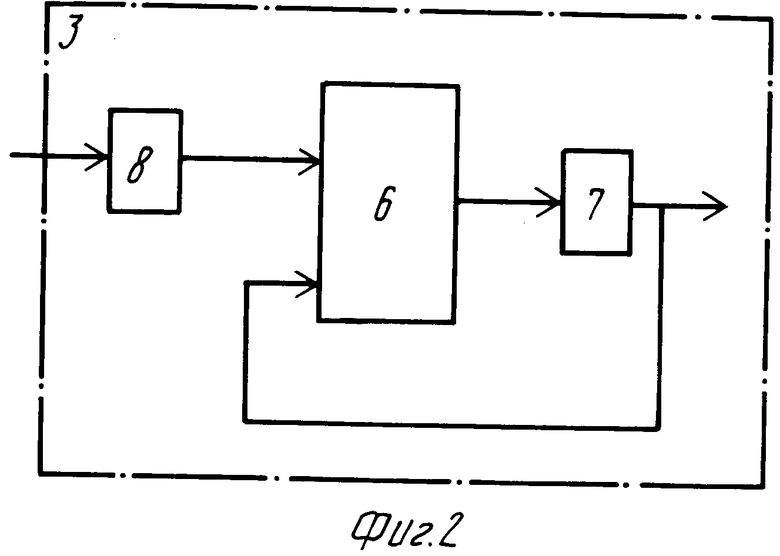

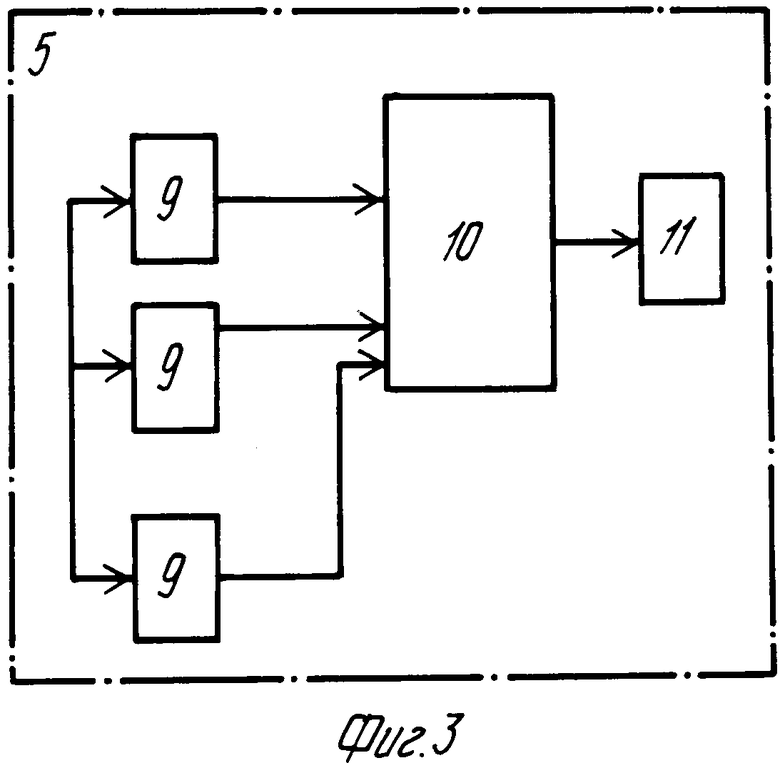

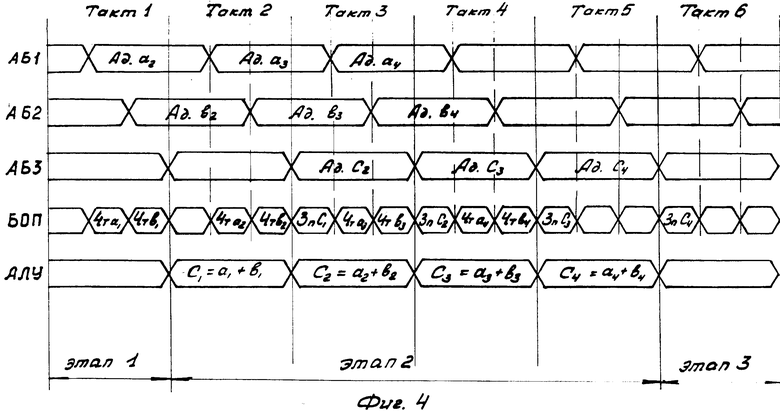

На фиг. 1 показана структурная схема векторного ускорителя; на фиг. 2 структура адресного узла; на фиг. 3 структура арифметического блока; на фиг. 4 временная диаграмма работы ускорителя.

Векторный ускоритель содержит блок 1 управления, блок 2 формирования адреса, состоящий из группы адресных узлов 3, блок 4 оперативной памяти (БОП) и арифметический блок 5.

Адресный узел (фиг. 2) содержит арифметико-логическое устройство (АЛУ) 6, регистр 7 адреса и регистр 8 инкремента.

Арифметический блок 5 (фиг. 3) содержит группу регистров 9, арифметико-логическое устройство 10 и выходной регистр 11.

Число входных регистров 9 и входов АЛУ равно количеству адресных блоков 3.

Рассмотрим работу векторного ускорителя, имеющего, например, три адресных узла 3: два из них адресуют элементы двух исходных векторов и один элемент результирующего вектора. В общем случае количество адресных узлов 3 в векторном ускорителе должно быть на единицу больше числа исходных векторов, участвующих в многоместных операциях. Кроме того, их количество определяет быстродействие блока 4 оперативной памяти. В рассматриваемом случае блок 4 оперативной памяти за один такт работы арифметического блока 5 должен выполнять три операции: две операции чтения и одну записи.

Описывая работу векторного ускорителя, предположим, что исходные векторы уже расположены в блоке 4 оперативной памяти. Они могли быть загружены перед началом работы или находится там в результате промежуточных вычислений.

Перед началом работы ускорителя в блок 1 управления загружается код операции выполняемой векторной команды, в регистры 7 адреса через регистры 8 инкремента начальные адреса, а в регистры 8 инкремента шаги между элементами исходных векторов.

Работа ускорителя поясняется временной диаграммой, приведенной на фиг. 4, на примере выполнения операции сложения двух векторов С А + В, где Аa1 a2 a3 a4} и Вb1 b2 b3 b4} исходные вектора, Сc1 c2 c3 c4} результирующий вектор, АБ1, АБ2, АБ3 выходы адресных АЛУ соответствующих адресных узлов, Чт операция чтения элемента вектора из блока оперативной памяти, БОП выход блока оперативной памяти, АЛУ выход арифметического блока.

Работу ускорителя можно разделить на три этапа. На первом выполняется разгон конвейера (такт 1). В такте 1 производится чтение из блока оперативной памяти элементов а1 и b1 по адресам, загруженным в регистры адресов адресных узлов при начальной загрузке.

На втором этапе арифметический блок полностью загружен выполнением операций с элементами вектором (такт 2 такт 4). В тактах 3 и 4 полностью загружен работой блок оперативной памяти.

На третьем этапе (такт 6) результат выполнения последней операции с4 записывается в блок оперативной памяти.

Время выполнения операции над двумя векторами в предлагаемом устройстве можно оценить по формуле:

t1 n + 2 тактов, где n число элементов вектора.

В прототипе это время составит:

t2 4n, где 3n тактов затрачивается на загрузку двух блоков векторных регистров исходными векторами и запись вектора результатов из третьего блока векторных регистров в блок оперативной памяти, n тактов на выполнение операции.

Техническая реализация векторного ускорителя может быть выполнена на стандартных микросхемах серии 1533, 132 и 1804; адресный узел на микросхемах 1533 ИР 22 (РИ, РА), 1533 ИПБ (АЛУ); блок оперативной памяти на микросхемах 132 РУ 10; арифметический блок на микросхемах 1804 ВС1 (АЛУ), 1533 ИР 22 (регистры); блок управления на микросхемах 1533 ИР 22 (регистр команд, регистр микрокоманд), 1804 ВУ 4(генератор адресов микрокоманд), 566 РТ 7 (память микрокоманд).

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

Изобретение относится к компьютерной технике и может быть использовано при производстве векторных устройств, обеспечивающих высокое быстродействие векторных операций. Векторный ускоритель состоит из блока управления, связанного с блоком формирования адресов, выполненным в виде группы из трех адресных узлов. Блок оперативной памяти предназначен для хранения исходных векторов и результатов выполнения операций. Количество адресных блоков определяет быстродействие блока оперативной памяти. Арифметический блок включает входные регистры, многовходовое АЛУ и выходной регистр. Число входных регистров и входов АЛУ равно количеству адресных блоков. За один такт работы арифметического блока АЛУ должен выполнять три операции: две операции чтения и одну записи. 2 з.п. ф-лы, 4 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электроника, 1986, N 8, с.43-46. | |||

Авторы

Даты

1995-08-27—Публикация

1992-12-15—Подача