Изобретение относится к вычислительной технике и может быть использовано при создании высоконадежных вычислительных систем.

Известно устройство, которое обеспечивает свертку по модулю путем последовательного сложения единиц числа в счетчике, при этом число поступает на вход устройства через схемы И по синхроимпульсу [1]

Недостатком устройства является невозможность свертки по модулю три.

Наиболее близким техническим решением к изобретению является устройство пирамидальной свертки по модулю три, содержащее n ступеней, каждая из которых содержит сумматоры, сумматоры с 1-й по (n-1)-ю ступени выполнены четырехразрядными, а сумматор n-й ступени двухразрядным, при этом выходы переноса каждого сумматора соединены с входом переноса этого сумматора [2]

Недостатком устройства является необходимость иметь большое количество четырехразрядных сумматоров при большой разрядности числа.

Целью изобретения является повышение надежности устройства путем уменьшения количества элементов за счет многократного использования элементов устройства в процессе свертки.

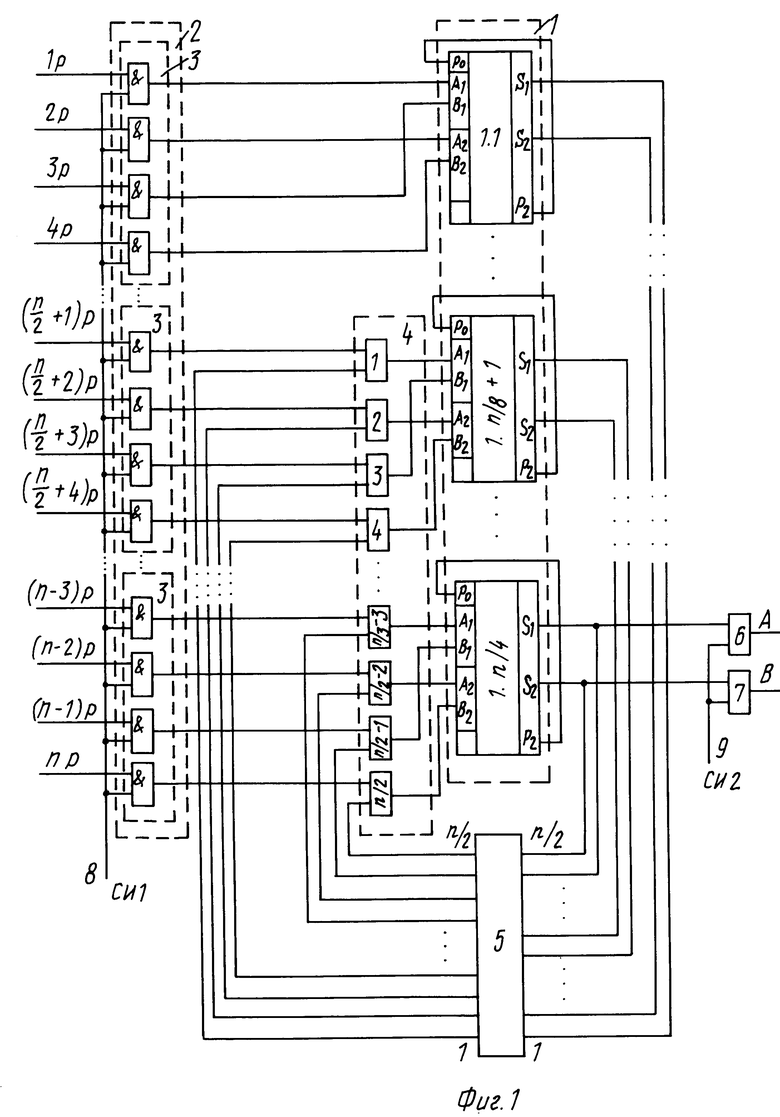

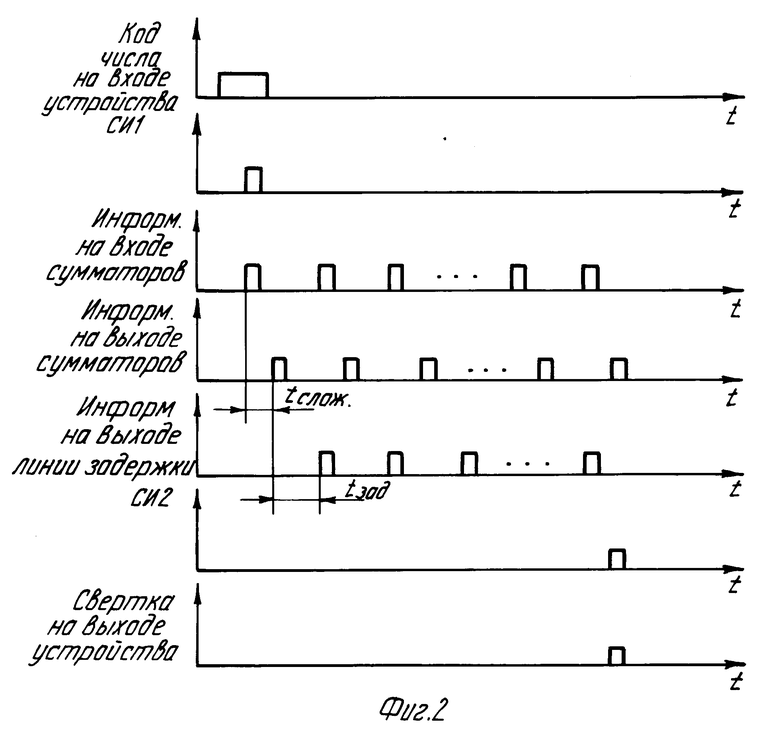

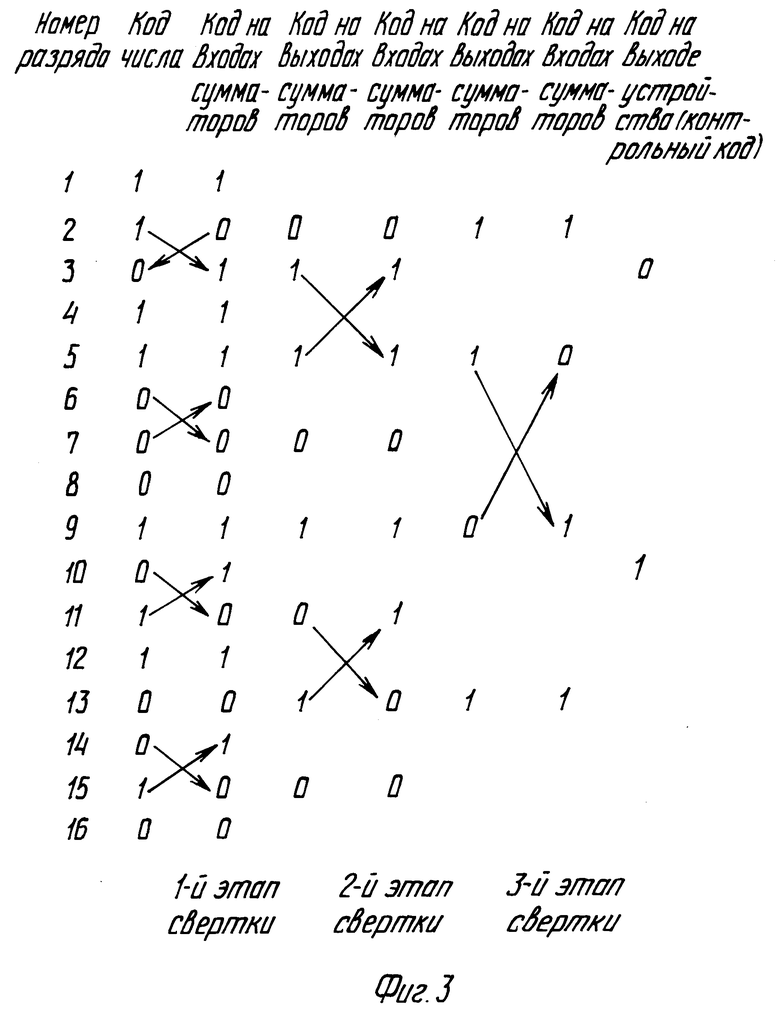

На фиг. 1 показана функциональная схема устройства; на фиг.2 временная диаграмма работы устройства; на фиг.3 схема процесса свертки по модулю три.

Устройство свертки по модулю три содержит сумматоры 1.1-1.n/4, группу 2 из n элементов И, разбитых на подгруппы 3 по четыре схемы И, элементы ИЛИ 4.1-4.n/2 элементы задержки 5.1-5.n/2, выходные элементы И 6 и 7, первый 8 и второй 9 синхронизирующие входы устройства.

Устройство работает следующим образом.

Контролируемое число подается на первые входы элементов И группы 2. При подаче на первый 8 синхронизирующий вход устройства синхроимпульса СИ 1 контролируемое число подается на входы сумматоров так, чтобы происходило суммирование четных разрядов с четными, нечетных разрядов с нечетными с учетом весовых функций разрядов. Результат сложения разрядов контролируемого числа по модулю три в виде n-разрядного числа через элементы задержки 5 подается на входы элементов ИЛИ 4 и далее на входы второй половины сумматоров с  +1

+1 -го по n/4-й. Результат второго этапа сложения разрядов контролируемого числа по модулю три вновь через элементы задержки 5 и элементы ИЛИ 4 с (n/4+1)-го по n/2-й подается на входы последней четвертой части сумматоров с

-го по n/4-й. Результат второго этапа сложения разрядов контролируемого числа по модулю три вновь через элементы задержки 5 и элементы ИЛИ 4 с (n/4+1)-го по n/2-й подается на входы последней четвертой части сумматоров с  +1

+1 -го по n/4-й. Свертка контролируемого числа по модулю три выполняется за (log2 n-1) этапов. Через время tсв после подачи синхроимпульса СИ 1 на второй 9 синхронизирующий вод устройства подается синхроимпульс СИ 2, который открывает элементы И 6 и 7 и результат свертки контролируемого числа по модулю три с выходов сумматора 1.n/4 подается на выходы устройства.

-го по n/4-й. Свертка контролируемого числа по модулю три выполняется за (log2 n-1) этапов. Через время tсв после подачи синхроимпульса СИ 1 на второй 9 синхронизирующий вод устройства подается синхроимпульс СИ 2, который открывает элементы И 6 и 7 и результат свертки контролируемого числа по модулю три с выходов сумматора 1.n/4 подается на выходы устройства.

Время свертки числа tсв определяется по формуле

tcв (log2 n-2)tзад + (log2 n-1)tслож, где tзад время задержки сигнала схемой задержки 5,

tслож время сложения чисел сумматором.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для свертки по модулю | 1991 |

|

SU1809443A1 |

| Сигнатурный анализатор | 1986 |

|

SU1472907A1 |

| Устройство вычисления функции @ @ с исправлением ошибок | 1984 |

|

SU1288690A1 |

| Преобразователь двоичного кода в код по модулю К | 1989 |

|

SU1732472A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

| Пирамидальная свертка по модулю три | 1989 |

|

SU1695308A2 |

| УСТРОЙСТВО ДЛЯ СВЕРТКИ ПО МОДУЛЮ ТРИ | 1991 |

|

RU2011215C1 |

| Устройство для свертки по модулю G=2 @ -1 | 1986 |

|

SU1325484A1 |

| Устройство для формирования остатков по модулю | 1986 |

|

SU1449986A1 |

| Устройство для приведения полиномов по модулям циклотомических полиномов | 1985 |

|

SU1357948A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании высоконадежных вычислительных систем. Цель изобретения повышение надежности устройства путем уменьшения количества элементов за счет многократного использования элементов устройства в процессе свертки. Устройство содержит сумматоры, группу элементов И, разбитых на подгруппы, элементы ИЛИ, элементы задержки, выходные элементы И. 3 ил.

УСТРОЙСТВО СВЕРТКИ ПО МОДУЛЮ ТРИ, содержащее сумматоры, причем выход переноса каждого сумматора соединен с входом переноса данного сумматора, и первую группу элементов ИЛИ, первые входы которых являются входами разрядов числа устройства, а вторые входы соединены с первым синхронизирующим входом устройства, отличающееся тем, что в него введены два выходных элемента И (n

разрядность сравниваемых чисел), n/2 элементов И, разбитых на подгруппы по четыре элемента, n/2 элементов задержки, сумматоры выполнены двухразрядными, элементы И первой группы разбиты на подгруппы по четыре элемента И в каждой подгруппе, причем выходы первых элементов И с 1 по n/8 подгрупп группы и выходы первых схем ИЛИ всех подгрупп соединены с входами первых разрядов первых слагаемых сумматоров с 1 по n/8-й и с (n/8 + 1)-го по n/4-й соответственно, входы вторых разрядов первых слагаемых которых соединены с выходами соответствующих вторых элементов И соответствующих подгрупп группы и вторых элементов ИЛИ всех подгрупп, выходы третьих элементов И с 1 по n/8 подгруппы группы и выходы третьих элементов ИЛИ всех подгрупп соединены с входами первых разрядов вторых слагаемых сумматоров с 1 по n/8 и с (n/8-й + 1)-го по n/4-й соответственно, входы вторых разрядов вторых слагаемых которых соединены с выходами соответствующих четвертых элементов И соответствующих подгрупп группы и четвертых элементов ИЛИ всех подгрупп, выходы сумматоров с 1 по n/4 соединены с входами элементов задержки соответственно с 1 по n/2, выходы которых соединены с первыми входами элементов ИЛИ всех подгрупп, вторые входы которых соединены с выходами элементов И группы с (n/2 + 1) по n соответственно, выходы n/4-го сумматора соединены с первыми входами соответственно первого и второго выходных элементов И, вторые входы которых подключены к второму синхронизирующему входу устройства, а выходы являются выходами устройства.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Пирамидальная свертка по модулю три | 1982 |

|

SU1105896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-10-27—Публикация

1992-06-15—Подача