j

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и диагностирования цифровой аппаратуры.

Целью изобретения является сокращение времени обнаружения многократных искажений входных сигналов - в нескольких тактах работы.

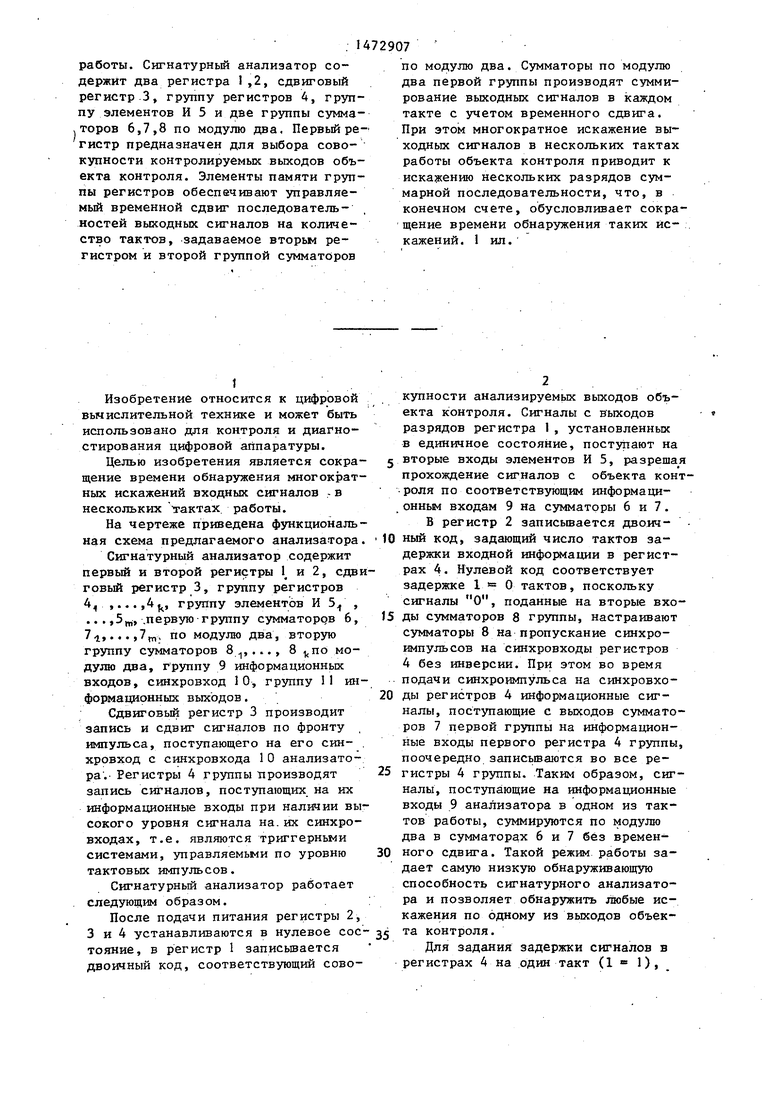

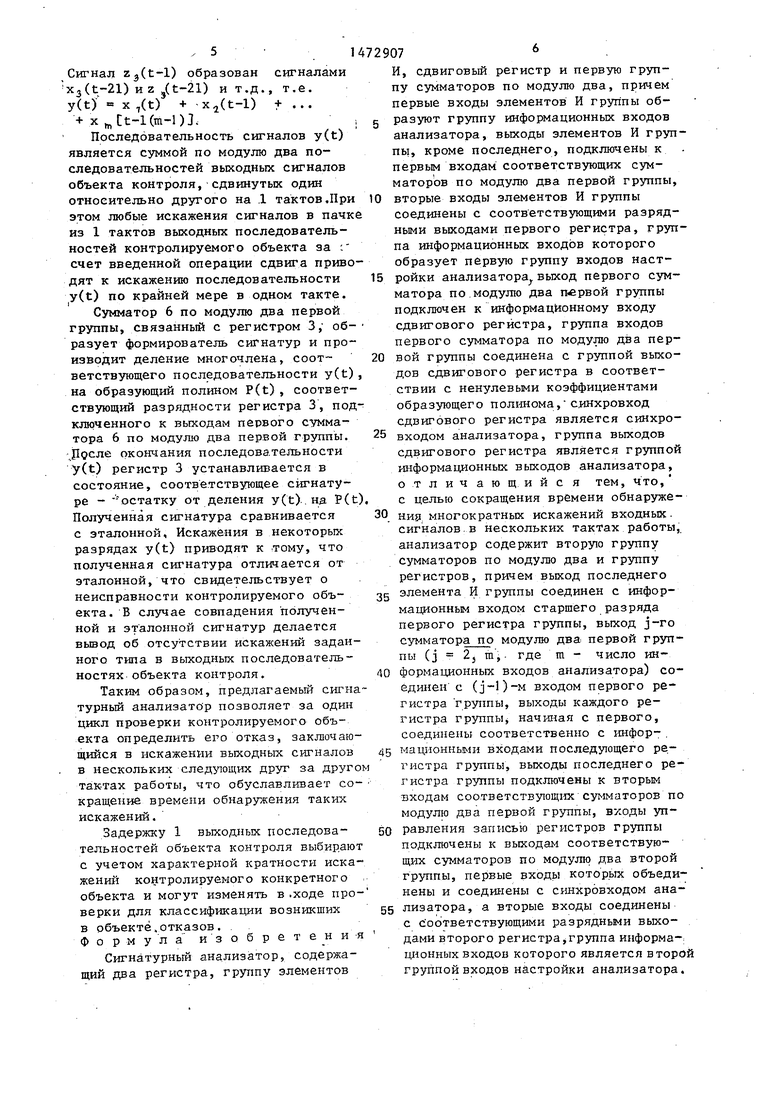

На чертеже приведена функциональная схема предлагаемого анализатора.

Сигнатурный анализатор содержит первый и второй регистры и 2, сдвиговый регистр 3, группу регистров 44 , ...,4, группу элементов И 5., , ... ,5№, .первую группу сумматоров 6, по модулю два, вторую группу сумматоров 8..., 8 по модулю два, группу 9 информационных входов, синхровход 10, группу П информационных выходов.

Сдвиговый регистр 3 производит запись и сдвиг сигналов по фронту , импульса, поступающего на его синхровход с синхровхода 10 анализатора. Регистры 4 группы производят запись сигналов, поступающих на их информационные входы при наличии высокого уровня сигнала на. их синхро- входах, т.е. являются триггерными системами, управляемыми по уровню тактовых импульсов.

Сигнатурный анализатор работает следующим образом.

После подачи питания регистры 2, 3 и 4 устанавливаются в нулевое состояние, в регистр 1 записывается двоичный код, соответствующий совокупности анализируемых выходов объекта контроля. Сигналы с выходов разрядов регистра 1 , установленных в единичное состояние, поступают на 5 вторые входы элементов И 5, разрешая прохождение сигналов с объекта контроля по соответствующим информаци- онным входам 9 на сумматоры 6 и 7. В регистр 2 записывается двоич10 ный код, задающий число тактов задержки входной информации в регистрах 4. Нулевой код соответствует задержке 1 « 0 тактов, поскольку сигналы О, поданные на вторые вхоJ5 ды сумматоров 8 группы, настраивают сумматоры 8 на пропускание синхроимпульсов на синхровходы регистров 4 без инверсии. При этом во время подачи синхроимпульса на синхровхо0 ды регистров 4 информационные сигналы, поступающие с выходов сумматоров 7 первой группы на информационные входы первого регистра 4 группы, поочередно записываются во все ре5 гистры 4 группы. Таким образом, сигналы, поступающие на информационные входы 9 анализатора в одном из тактов работы, суммируются по модулю два в сумматорах 6 и 7 без времен0 ного сдвига. Такой режим работы задает самую низкую обнаруживающую способность сигнатурного анализатора и позволяет обнаружить любые искажения по одному из выходов объек5 та контроля.

Для задания задержки сигналов в регистрах 4 на один такт (1 « 1),

31

необходимо в последний разряд регистра 2 записать I, а в остальные его разряды - О. Тогда последний сумматор 8 второй группы инвертирует синхроимпульсы и подает их на еин- хровход последнего регистра 4. При этом запись информации в него происходит после окончания очередного синхроимпульса, т.е. регистры 4 задерживают сигналы, поступающие с выходов сумматора 7, на один такт. - Этот режим соответствует обнаружению любых многократных искажений, возникающих либо в одной из выходных последовательностей объекта контроля, либо в одном из тактов работы объекта контроля.

Задержка сигналов с выходов сумматоров 7 на 1 тактов позволяет об- наружить любые многократные искажения в 1 тактах работы объекта контроля. Для задания задержки входной информации на 1 тактов необходимо : разбить множество из k регист- ров 4 на 1 подгрупп так, чтобы в каждой подгруппе было не менее двух регистров (при этом 1 не должно превышать k/2) -, разряды регистра 2, связанные через соответствующие сумматоры 8 с синхровходами последних регистров 4 в выбранных подгруппах, установить в единичное состояние, а остальные разряды регистра 2 установить в нулевое состояние.

После задания режима работы сигнатурного анализатора путем записи двоичных сигналов в регистры 1 и 2 на группу 9 входов сигнатурного анализатора подаются сигналы с вы- ходов контролируемого объекта xt(t), х (t) ,. . .ij xM(t) , а на вход 1 0 подаются импульсы, синхронизирующие работу объекта контроля и сигнатурного анализатора. Длительность синхроимпуль- сов должна превышать суммарное время переключения регистров 4, т.е.

V Л/ л Т

к v Э- t сц

е k - число регистров 4;

- время записи информации в один из регистров 4 при наличии на его синхровходе высокого уровня управляющего сигнала;

Т - период следования выходных сигналов объекта контроля. Сигнал х t) через первый элемент 5 поступает на первый сумматор 6 по

модулю два, где осуществляется его сложение по модулю два с сигналом, поступающим с выхода первого разряда регистра 3:

y(t) ) +

z,(x)

В случае задания задержки сигналов в регистрах 4 на,один такт, сигнал z t) записывается в последний регистр 4 в конце предыдущего такта t-1 и равен сумме по модулю два сигнала xi(t-l) с второго информационного входа и сигнала z2(t-i), поступающего с 2-го разряда последнего регистра 4,т.е. z t) « x2(t-l) + + zi(t-l). Сигнал z2(t-l), в свою

очередь, образован сигнала x(t-2) иг3(С-2), т.е. z2(t-l) x3(t-2) .+ + z3(t-2) и т.д.

Выразив значение сигналов на выходах последнего регистра 4 через значения сигналов, поступающих на информационные входы 9, получим

y(t) - х ,(t) + xm(t-m+l)

+ x,(t-l) +

Таким образом, последовательность сигналов y(t) является суммой по модулю два последовательностей выходных сигналов объекта контроля, сдвинутых один относительно другого на один такт.

В общем случае задания задержки сигналов в регистрах 4 на 1 тактов,1 где , сигнал zt(t) записывается в регистр 4, являющийся последним регистром 1-й подгруппы, на такте t-11 из последнего регистра 4 (1-1 )-1 подгруппы (поскольку для организации информации на 1 тактов группа регистров 4 должна быть разбита на 1 подгрупп, причем запись сигналов в последние регистры подгрупп выполняется после окончания текущего синхроимпульса, а в остальные регистры каждой подгруппы запись сигналов производится в течение действия текущего синхроимпульса) .

Таким образом, сигнал z 7(t) равен сумме по модулю два сигнала x(t-l) с второго информационного входа группы 9 и сигнала z (t-1) , поступающего с второго разряда последнего регистра 4, т.е.

zt(t) xt(t-l) + za(t-2).

Сигнал z3(t-l) образован

x3(t-21) кг 5(t-21) и т.д.

y(t) - х ,(t) + x2(t-l)

+ xmCt-l(m-l)J.

Последовательность сигналов y(t) является суммой по модулю два последовательностей выходных сигналов объекта контроля, сдвинутых один относительно другого на 1 тактов.При этом любые искажения сигналов в пачке из 1 тактов выходных последовательностей контролируемого объекта за : счет введенной операции сдвига приводят к искажению последовательности y(t) по крайней мере в одном такте.

Сумматор 6 по модулю два первой группы, связанный с регистром 3, об- разует формирователь сигнатур и производит деление многочлена, соответствующего последовательности y(t), на образующий полином P(t), соответствующий разрядности регистра 3, подключенного к выходам первого сумматора 6 по модулю два первой группы. Д1осле окончания последовательности y(t) регистр 3 устанавливается в состояние, соответствующее сигнатуре - остатку от деления y(t) на P(t). Полученная сигнатура сравнивается с эталонной. Искажения в некоторых разрядах y(t) приводят к тому, что полученная сигнатура отличается от эталонной, что свидетельствует о неисправности контролируемого объекта. В случае совпадения полученной и эталонной сигнатур делается вывод об отсутствии искажений заданного типа в выходных последовательностях объекта контроля.

Таким образом, предлагаемый сигнатурный анализатор позволяет за один цикл проверки контролируемого объекта определить его отказ, заключающийся в искажении выходных сигналов в нескольких следующих друг за другом тактах работы, что обуславливает сокращение времени обнаружения таких искажений.

Задержку 1 выходных последовательностей объекта контроля выбирают с учетом характерной кратности искажений контролируемого конкретного объекта и могут изменять в .ходе про- верки для классификации возникших

в объекте,отказов.

Формула изобретения

Сигнатурный анализатор, содержащий два регистра, группу элементов

1472907&

сигналами И, сдвиговый регистр и первую груп- , т.е. пу сумматоров по модулю два, причем + ... первые входы элементов И группы об- , с разуют группу информационных входов

анализатора, выходы элементов И груп25

пы, кроме последнего, подключены к первым входам соответствующих сумматоров по модулю два первой группы,

10 вторые входы элементов И группы

соединены с соответствующими разрядными выходами первого регистра, группа информационных входов которого образует первую группу входов наст15 ройки анализатора выход первого сумматора по модулю два первой группы подключен к информационному входу сдвигового регистра, группа входов первого сумматора по модулю два пер20 вой группы соединена с группой выходов сдвигового регистра в соответствии с ненулевыми коэффициентами образующего полинома, синхровход сдвигового регистра является синхро- входом анализатора, группа выходов сдвигового регистра является группой информационных выходов анализатора, отличающийся тем, что, с целью сокращения времени обнаруже30 нид многократных искажений входных сигналов в нескольких тактах работы, анализатор содержит вторую группу сумматоров по модулю два и группу регистров, причем выход последнего

35 элемента И группы соединен с информационным входом старшего разряда первого регистра группы, выход j-ro сумматора по модулю два первой группы (j 2} m, где m - число ин40 формационных входов анализатора) соединен с (j-l)-M входом первого регистра группы, выходы каждого регистра группы, начиная с первого, соединены соответственно с инфор45 мационными входами последующего регистра группы, выходы последнего регистра группы подключены к вторым входам соответствующих сумматоров по модулю два первой группы, входы уп50 равления записью регистров группы подключены к выходам соответствующих сумматоров по модулю два второй группы, первые входы которых объединены и соединены с синхровходом ана55 лизатора, а вторые входы соединены с соответствующими разрядными выходами второго регистра,группа информационных входов которого является второй группой входов настройки анализатора.

5

пы, кроме последнего, подключены к первым входам соответствующих сумматоров по модулю два первой группы,

вторые входы элементов И группы

соединены с соответствующими разрядными выходами первого регистра, группа информационных входов которого образует первую группу входов наст5 ройки анализатора выход первого сумматора по модулю два первой группы подключен к информационному входу сдвигового регистра, группа входов первого сумматора по модулю два пер0 вой группы соединена с группой выходов сдвигового регистра в соответствии с ненулевыми коэффициентами образующего полинома, синхровход сдвигового регистра является синхро- входом анализатора, группа выходов сдвигового регистра является группой информационных выходов анализатора, отличающийся тем, что, с целью сокращения времени обнаруже0 нид многократных искажений входных сигналов в нескольких тактах работы, анализатор содержит вторую группу сумматоров по модулю два и группу регистров, причем выход последнего

5 элемента И группы соединен с информационным входом старшего разряда первого регистра группы, выход j-ro сумматора по модулю два первой группы (j 2} m, где m - число ин0 формационных входов анализатора) соединен с (j-l)-M входом первого регистра группы, выходы каждого регистра группы, начиная с первого, соединены соответственно с инфор5 мационными входами последующего регистра группы, выходы последнего регистра группы подключены к вторым входам соответствующих сумматоров по модулю два первой группы, входы уп0 равления записью регистров группы подключены к выходам соответствующих сумматоров по модулю два второй группы, первые входы которых объединены и соединены с синхровходом ана5 лизатора, а вторые входы соединены с соответствующими разрядными выходами второго регистра,группа информационных входов которого является второй группой входов настройки анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1985 |

|

SU1256031A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Сигнатурный анализатор | 1987 |

|

SU1416997A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1795459A1 |

| Многовходовый сигнатурный анализатор | 1985 |

|

SU1332319A1 |

| Сигнатурный анализатор | 1986 |

|

SU1383360A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Сигнатурный анализатор | 1984 |

|

SU1270773A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и диагностирования цифровой аппаратуры.Целью изобретения является сокращение времени обнаружения многократных искажений выходных сигналов объекта контроля в нескольких тактах работы. Сигнатурный анализатор содержит два регистра 1, 2, сдвиговый регистр 3, группу регистров 4, группу элементов И 5 и две группы сумматоров по модулю два 6, 7,8. Первый регистр предназначен для выбора совокупности контролируемых выходов объекта контроля. Элементы памяти группы регистров обеспечивают управляемый временной сдвиг последовательностей выходных сигналов на количество тактов, задаваемое вторым регистром и второй группой сумматоров по модулю два. Сумматоры по модулю два первой группы производят суммирование выходных сигналов в каждом такте с учетом временного сдвига. При этом многократное искажение выходных сигналов в нескольких тактах работы объекта контроля приводит к искажению нескольких разрядов суммарной последовательности, что, в конечном счете, обусловливает сокращение времени обнаружения таких искажений. 1 ил.

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Бюл | |||

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Боронной оборотный зуб из углового металла | 1913 |

|

SU681A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сигнатурный анализатор | 1985 |

|

SU1256031A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1989-04-15—Публикация

1986-02-02—Подача