Изобретение относится к вычислительной технике и может быть использовано в адресном тракте ЭВМ, в частности для генерации адресов объектов, регулярно расположенных в памяти, по заданным: базе (адресу первого объекта), шагу, с которым объекты расположены в памяти, и количеству объектов,

Целью изобретения является повышение достоверности работы за счет контроля вычисления функции + (i-1)u p(l€i.6N) и восстановления работоспособности после сбоя.

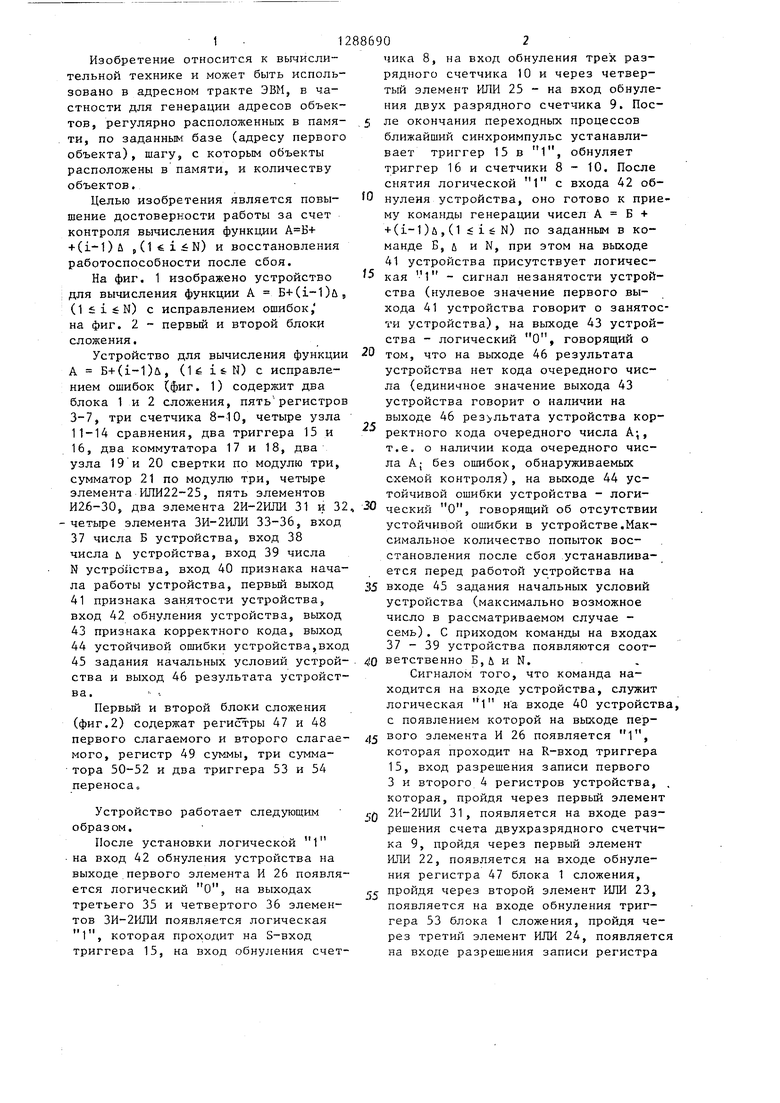

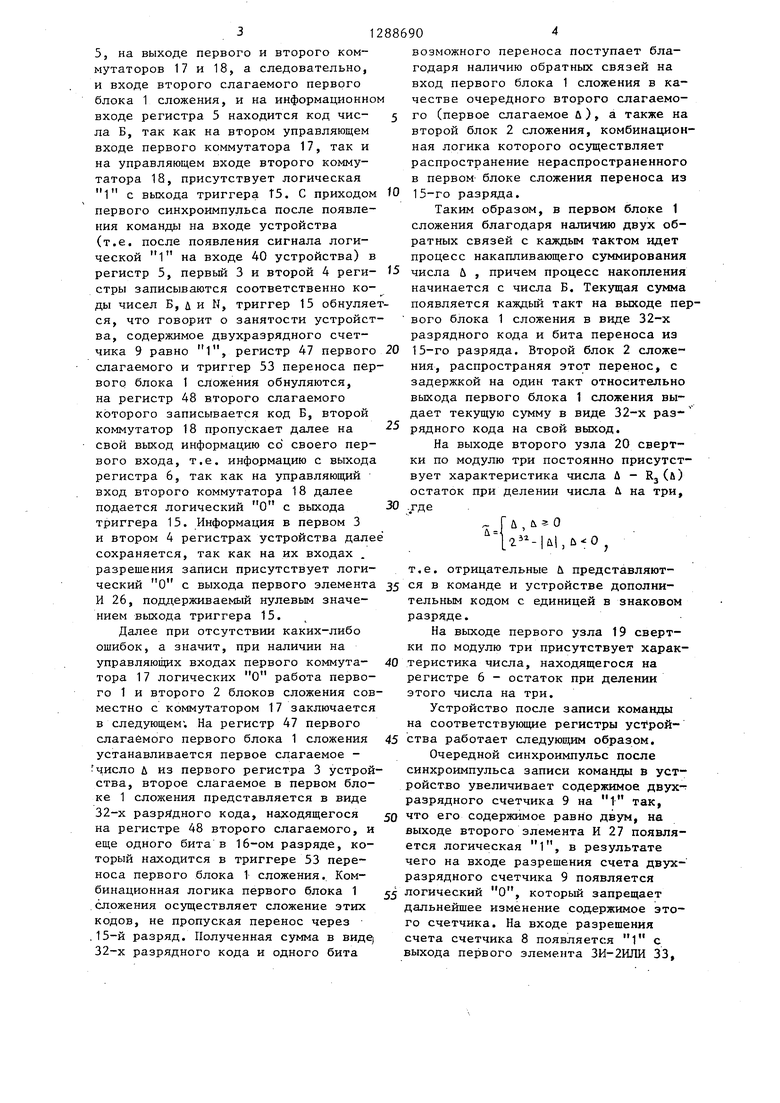

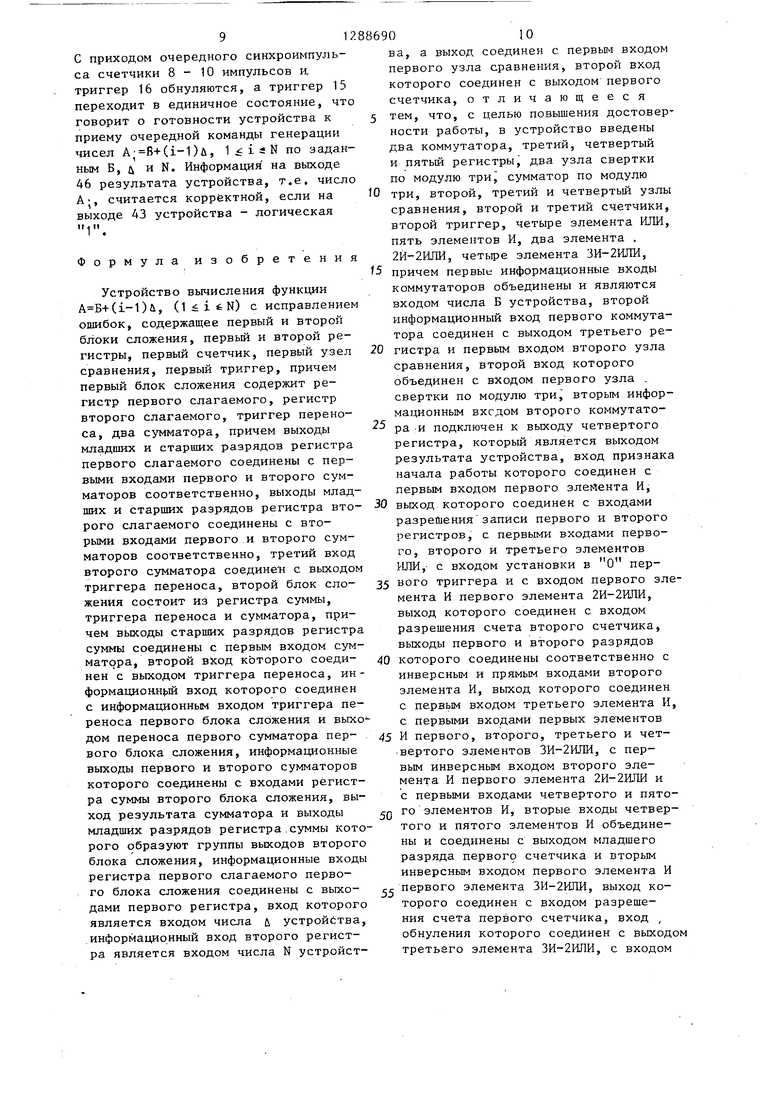

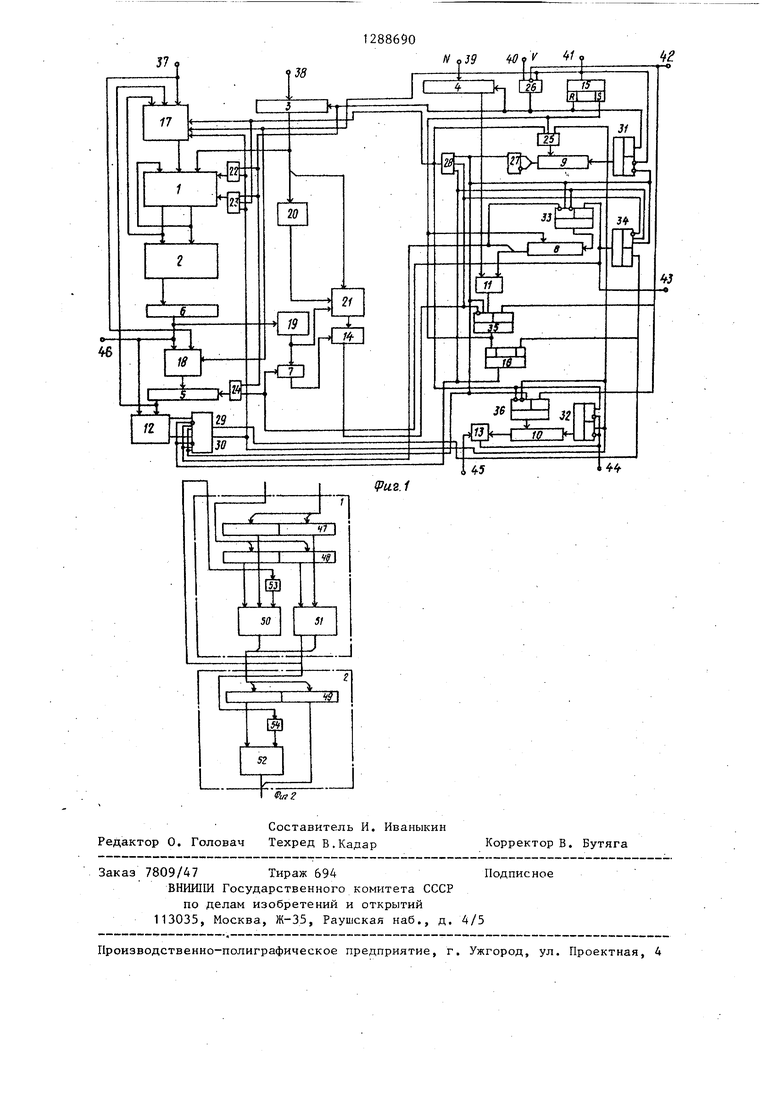

На фиг. 1 изображено устройство для вычисления функции А B+Ci-Du, (1 ) с исправлением ошибок, на фиг. 2 первый и второй блоки сложения.

Устройство для вычисления функции А B+(i-1)u, (1ё is-N) с исправлением ошибок (фиг. 1) содержит два блока 1 и 2 сложения, пять регистров 3-7, три счетчика 8--10, четыре узла 11-14 сравнения, два триггера 15 и 16, два коммутатора 17 и 18, два узла 19 и 20 свертки по модулю три, сумматор 21 по модулю три, четыре элемента ИЛИ22-25, пять элементов И26-30, два элемента 2И-2ИЛИ 31 и 32 -четыре элемента ЗИ-2ИЛИ 33-36, вход 37 числа Б устройства, вход 38 числа ь устройства, вход 39 числа N устро йства, вход 40 признака начала работы устройства, первый выход 41 признака занятости устройства, вход 42 обнуления устройства, выход

43признака корректного кода, выход

44устойчивой ошибки устройства,вход

45задания начальных условий устройства и выход 46 результата устройства. .

Первый и второй блоки сложения (фиг.2) содержат регистры 47 и 48 первого слагаемого и второго слагаемого, регистр 49 суммы, три сумматора 50-52 и два триггера 53 и 54 переноса

Устройство работает следующим образом.

После установки логической 1

на вход 42 обнуления устройства на выходе первого элемента И 26 появляется логический О, на выходах третьего 35 и четвертого 36 элементов ЗИ-2ИЛИ появляется логическая 1, которая проходит на S-вход триггера 15, на вход обнуления счет

чика 8, на вход обнуления трех разрядного счетчика 10 и через четвер- тьм элемент ИЛИ 25 - на вход обнуления двух разрядного счетчика 9. После окончания переходных процессов ближайший синхроимпульс устанавливает триггер 15 в 1, обнуляет триггер 16 и счетчики 8 - 10. После снятия логической 1 с входа 42 обнуленя устройства, оно готово к приему команды генерации чисел А Б + + (i-1 )й , (1 ii6 N) по заданным в команде Б, U и N, при этом на выходе 41 устройства присутствует логическая 1 - сигнал незанятости устройства (нулевое значение первого выхода 41 устройства говорит о занятости устройства), на выходе 43 устройства - логический О, говорящий о

том, что на выходе 46 результата устройства нет кода очередного числа (единичное значение выхода 43 устройства говорит о наличии на выходе 46 рез льтата устройства корректного кода очередного числа А-,, т.е. о наличии кода очередного числа AJ без ошибок, обнаруживаемых схемой контроля), на выходе 44 устойчивой ошибки устройства - логический О, говорящий об отсутствии устойчивой ошибки в устройстве.Максимальное количество попыток восстановления после сбоя устанавливается перед работой устройства на

входе 45 задания начальных условий устройства (максимально возможное число в рассматриваемом случае - семь). С приходом команды на входах 37 - 39 устройства появляются соответственно B,ii и N.

Сигналом того, что команда находится на входе устройства, служит логическая 1 н а входе 40 устройства, с появлением которой на выходе первого элемента И 26 появляется 1, которая проходит на R-вход триггера 15, вход разрешения записи первого 3 и второго 4 регистров устройства, , которая, пройдя через первый элемент

2И-2ИЛИ 31, появляется на входе разрешения счета двухразрядного счетчика 9, пройдя через первый элемент ИЛИ 22, появляется на входе обнуления регистра 47 блока 1 сложения,

пройдя через второй элемент ИЛИ 23, появляется на входе обнуления триггера 53 блока 1 сложения, пройдя через третий элемент ИЛИ 24, появляется на входе разрешения записи регистра

5, на выходе первого и второго коммутаторов 17 и 18, а следовательно, и входе второго слагаемого первого блока 1 сложения, и на информационном входе регистра 5 находится код числа Б, так как на втором управляющем входе первого коммутатора 17, так и на управляющем входе второго коммутатора 18, присутствует логическая 1 с выхода триггера Т5. С приходом первого синхроимпульса после появления команды на входе устройства (т.е. после появления сигнала логической 1 на входе 40 устройства) в регистр 5, первьй 3 и второй 4 регистры записываются соответственно коды чисел Б, U и N, триггер 15 обнуляется, что говорит о занятости устройства, содержимое двухразрядного счетчика 9 равно 1, регистр 47 первого 20 15-го разряда. Второй блок 2 сложеслагаемого и триггер 53 переноса первого блока 1 сложения обнуляются, на регистр 48 второго слагаемого которого записывается код Б, второй коммутатор 18 пропускает далее на свой выход информацию со своего первого входа, т.е. информацию с выхода регистра 6, так как на управляющий вход второго коммутатора 18 далее подается логический О с выхода триггера 15. Информация в первом 3 и втором 4 регистрах устройства далее сохраняется, так как на их входах разрешения записи присутствует логический О с выхода первого элемента 35 в команде и устройстве дополниИ 26, поддерживаемый нулевым значением выхода триггера 15.

Далее при отсутствии каких-либо ошибок, а значит, при наличии на управляющих входах первого коммутатора 17 логических О работа первого 1 и второго 2 блоков сложения совместно с коммутатором 17 заключается в следующем; На регистр 47 первого слагаемого первого блока 1 сложения устанавливается первое слагаемое число U из первого регистра 3 устройства, второе слагаемое в первом блоке 1 сложения представляется в виде 32-х разрядного кода, находящегося на регистре 48 второго слагаемого, и еще одного бита в 16-ом разряде, который находится в триггере 53 переноса первого блока 1 сложения. Комбинационная логика первого блока 1 сложения осуществляет сложение этих кодов, не пропуская перенос через

.15-й разряд. Полученная сумма в виде) 32-х разрядного кода и одного бита

т886904

возможного переноса поступает благодаря наличию обратных связей на вход первого блока 1 сложения в качестве очередного второго слагаемо5 го (первое слагаемое Л), а также на второй блок 2 сложения, комбинационная логика которого осуществляет распространение нераспространенного в первом блоке сложения переноса из

10 15-го разряда.

Таким образом, в первом блоке 1 сложения благодаря наличию двух обратных связей с каждым тактом идет процесс накапливающего суммирования

15 числа U , причем процесс накопления начинается с числа Б. Текущая сумма появляется каждый такт на выходе первого блока 1 сложения в виде 32-х разрядного кода и бита переноса из

ния, распространяя этот перенос, с задержкой на один такт относительно выхода первого блока 1 сложения выдает текущую сумму в виде 32-х разрядного кода на свой выход.

На выходе второго узла 20 свертки по модулю три постоянно присутствует характеристика числа Д - ) остаток при делении числа Д на три,

где

U , л О

й

,й-0,

т.е. отрицательные и представляюттельным кодом с единицей в знаковом разряде.

На выходе первого узла 19 свертки по модулю три присутствует харак40 теристика числа, находящегося на регистре 6 - остаток при делении этого числа на три.

Устройство после записи команды на соответствующие регистры уст рой45 ства работает следующим образом. Очередной синхроимпульс после синхроимпульса записи команды в устройство увеличивает содержимое двухразрядного счетчика 9 на 1 так,

50 что его содержимое равно двум, на выходе второго элемента И 27 появляется логическая 1, в результате чего на входе разрешения счета двухразрядного счетчика 9 появляется

55 логический О, который запрещает дальнейшее изменение содержимое этого счетчика. На входе разрешения счета счетчика 8 появляется 1 с выхода первого элемента ЗИ-2ИЛИ 33,

в результате чего следующий синхроимпульс переводит содержимое счетчика 8 из о в 1. После этого синхроимпульса на регистре 6 появляется код первого результата AJ , на выход узла 19 свертки по модулю три появляется RJ(А,) - остаток при делении AJ на три, код на регистре 6 сравнивается с кодом Б на регистре 5, содержимое которого не меняется с момента записи команды в устройство благодаря наличию логического О н выходе третьего элемента ИЛИ 24, который, в свою очередь, поддерживается нулевым значением выхода элеме та 34,

Сравнение кодов на регистрах 6 и 5 осуществляется в узле 12 сравнени Сигналом разрешения выхода сравнени служат нулевое значение выхода триг гера 16, единичное значение выхода второго элемента И 27 и единичное значение нулевого разряда выхода счетчика В, В случае несовпадения хотя бы в одном из разрядов указанн кодов, на выходе элемента И 30 появляется 1 (на выходе элемента И 29 остается О), которая проходит через первый 22 и второй 23 элементы ИЛИ на входы обнуления первого блока 1 сложения, через четвертьй элемент ИЛИ 25 - на вход обнуления двухразрядного счетчика 9, через второй элемент 2И-2ИЛИ 32 - на вход разрешения счета трехразрядного счетчика 10 благодаря наличию логического О на выходе трехраз)ядног узла 13 сравнения, а также проходит на первый управляющий вход первого коммутатора 17, в результате чего н его выходе появляется код с второго его информационного входа, т.е. код Б с выхода регистра 5. С приходом очередного синхроимпульса в этом случае двухразрядный счетчик 9 обнуляется, следовательно, на выходе второго элемента И27 появляется О в результате чего разрешается счет двухразрядного счетчика 9, запрещается счет счетчика 8, содержимое трехразрядного счетчика 10 переходи из О в 1, регистр 47 первого слагаемого и триггер 53 переноса первого блока 1 сложения обнуляются а на регистр 48 второго слагаемого первого блока 1 сложения записывается код Б из регистра 5, на выходе элемента И 30 устанавливается О, вследствие чего на выходе первого

0

}5

0 5

коммутатора 17 подается информация с его первого входа, т.е. информация с выхода первого блока 1 сложения.

Таким образом, происходит автоматический перезапуск команды. После прохождения двух синхроимпульсов после такого перезапуска на регистре 6 снова появляется код первого результата А,, на выходе узла 19 свертки по модулю три - Rj(А() - (характеристика А|), на выходе второго элемента И 27 появляется 1,т.е. устройство в том же состоянии, что и до перезапуска, за исключением того, что содержимое трехразрядного счетчика 10 равно 1. В случае повторного обнаружения несовпадения кодов на регистрах 6 и 5 производят повтор ный перезапуск команды, а содержимое трехразрядного счетчика 10 увеличивается на 1. В случае повтора ошибки К раз (где К - число на входе 45 устройства), на выходе 44 устройства появляется логическая 1 - сигнал устойчивой ошибки в устройстве. Если коды на регистрах 6 и 5 совпадают, то на выходе элемента И 29 появляется 1 (на выходе элемента И 30 остается О), которая проходит на S-вход триггера 16, на выход элемента ЗИ-2ИЛИ 34, а оттуда на управляющий вход регистра 7, через первую схему ЗИ-2ИЛИ 33 - на управляющий вход счетчика 8, через третий элемент ИЛИ 24 - иа вход разрешения записи регистра 5, кроме того, 1 появляется на входе обнуления трехразрядного счетчика 10 бла годаря наличию 1 на выходе элемента И 27 и О на выходах элементов И 28 и 30.

С приходом очередного синхроимпульса трехразрядный счетчик 10 нуляется, триггер 16 переключает- .ся в 1, к содержимому счетчика 8 импульсов прибавляется 1, в регистре 5 имеется первый результат А,, в . регистре 6 - второй результат А,, в

Q регистре 7 - R.j(A,), а на выходе узла 19 свертки по модулю три - Rj(Aj). Далее при отсутствии сигнала ошибки на выходе четвертого узла 14 сравнения с приходом следующего

ее синхроимпульса к содержимому счетчика 8 импульсов прибавляется 1 в регистр 5 записывается второй результат А с выхода регистра 6, в регистр 7 - Rj (А,) с выхода узла 19

30

35

40

свертки по модулю три, на выходе которого появляется теперь R(А), в то время как на выходе регистра 6 - AJ и так далее. Контроль выходного числа AJ, 2 ii N, находящегося на регистре 6, осуществляется в соответствии с формулой

Rj (A-)R3 (Кз (А.)+КЗ (л)+2 -Знй),

де

НЗ(А;)

- остаток при на три числа , находящегося на регистре 6;

R.(A; |) - остаток при делении

на три числа А,- ,, находящегося на регистре 5, который находится на регистре Т,

Кз(Л - остаток при делении на три числа

Л,Л 40 , находящегося на первом регистре 3 устройства,

ЗнU - значение 31-го разряда выхода первого регистра 3 устройства 4 - знак числа л..

ДПроверка равенства по этой формуле осуществляется при помощи сумматора 21 по модулю три и узла 14 сравнения. Номер результата i указывается на счетчике 8 импульсов, l на выходе 43 говорит о наличии корректного кода числа А, на регистре 6 и разрешает запись его в регистре 5, а также запись R(A;) на регистр 7 с выхода узла 19 свертки по модулю три. Если при появлении на регистре 6 результата кода A: 2ij rN, узел 14 сравнения выдает на свой выход логическую 1. то она проходит на выход третьего элемента И 28, так как на выходе второго элемента И27 и выходе триггера 16 присутствуют логические 1., откуда через элемент 2И-2ИЛИ 32 она проходит на вход разрешения счета трехразрядного счетчика 10, через четвертый элемент ИЛИ 25 - на вход обнуления двухразрядного счетчика 9, через второй элемент ИЛИ 23 - на вход обнуления триггера 53 первого блока 1 сложения, а также на третий управляющий вход первого коммутатора 17. В результате этого на выходе

}-«

20

2886908

первого коммутатора 17, а следовательно, и на втором входе первого блока 1 сложения оказывается код А с выхода регистра 5.

5 Таким образом, начинается процесс восстановления. С приходом следующего синхроимпульса содержимое трехразрядного счетчика 10 переходит из О

till

в 1 , двухразрядный счетчик 9 обну- 10 ляется, на выходе второго 27 и

третьего 28 элементов И и появляются логические О, в первом блоке 1 сложения обнуляется триггер 53 переноса, а на регистр 48 второго слагае- 5 мого записывается код Ау,/Кроме того, на выходе элемента ЗИ-2ИЛИ 34 оказывается логический О, который, пройдя на входы разрешения записи регистров 5 и 7, запрещает изменение содержимого этих регистров. После прохождения двух синхроимпульсов на регистре 6 и на выходе узла 19 свертки по модулю три снова оказываются соответственно Ai и Rj (AJ ), на вьпсоде второго элемента И 27 появляется логическая 1, что свидетельствует об окончании процесса восстановления кода AJ. Если на выходе узла 14 сравнения вновь 30 появляется логическая 1, то процесс восстановления повторяется, и к содержимому трехразрядного счетчика 10 прибавляется 1.

I

При повторении К раз процесса восстановления (где К - число на входе 45 устройства) появляется логическая 1 на выходе 44 устройства - сигнал об устойчивой ошибке в устройстве. Если после 1-го восстановления, 1 i К, на выходе узла 14 сравнения логическая 1 не появляется, то. трехразрядный счетчик 10 со следующим синхроимпульсом обнуляется и

4 работа устройства продолжается. При достижении содержимого счетчика 8 импульсов числа N, т.е. при получении последнего результата на регистре 6, на выходе узла 11 сравнения появляется логическая 1, которая при отсутствии сигнала ошибки на выходе узла 14 сравнения, т.е. при отсутствии ошибок в АИ, проходит на R-вход триггера 16, на вход обнуле„ ния счетчика 8, на S-вход триггера 15 и через элемент ИЛИ 25 - на вход обнуления двухразрядного счетчика 9,

На входе трехразрядного счетчика 10

It 111

35

40

50

также присутствует логическая

С приходом очередного синхроимпульса счетчики 8-10 импульсов и, триггер 16 обнуляются, а триггер 15 переходит в единичное состояние, что говорит о готовности устройства к приему очередной команды генерации чисел (1-1)л, по заданным Б, U и N. Информация на выходе 46 результата устройства, т.е. число А , считается корректной, если на

выходе 43 устройства - логическая

111 1

I

Формула изобретения

Устройство вычисления функции (i-1)u, (liifcN) с исправлением ошибок, содержащее первый и второй блоки сложения, первый и второй регистры, первый счетчик, первый узел сравнения, первый триггер, причем первый блок сложения содержит регистр первого слагаемого, регистр второго слагаемого, триггер переноса, два сумматора, причем выходы младших и старших разрядов регистра первого слагаемого соединены с первыми входами первого и второго сумматоров соответственно, выходы младших и старших разрядов регистра второго слагаемого соединены с вторыми входами первого и второго сумматоров соответственно, третий вход второго сумматора соединен с выходом триггера переноса, второй блок сложения состоит из регистра суммы, триггера переноса и сумматора, причем выходы старших разрядов регистра суммы соединены с первым входом сумматора, второй вход которого соединен с выходом триггера переноса, ин- фopмaциoнн JШ вход которого соединен с информационным входом триггера переноса первого блока сложения и выхо дом переноса первого сумматора первого блока сложения, информационные выходы первого и второго сумматоров которого соединены с входами регистра суммы второго блока сложения, выход результата сумматора и выходы младших разрядов регистра.суммы которого образуют группы выходов второго блока сложения, информационные входы регистра первого слагаемого первого блока сложения соединены с выходами первого регистра, вход которого является входом числа и устройства, .информационный вход второго регистра является входом числа N устройст

ва, а выход соединен с первьп входом первого узла сравнения, второй вход которого соединен с выходом первого счетчика, отличающееся

тем, что, с целью повышения достоверности работы, в устройство введены два коммутатора, третий, четвертый и пятый регистрыj два узла свертки по модулю три сумматор по модулю

три, второй, третий и четвертьш узлы сравнения, второй и третий счетчики, второй триггер, четыре элемента ИЛИ, пять элементов И, два элемента . 2И-2ИЛИ, четыре элемента ЗИ-2ИЛИ,

причем первые информационные входы коммутаторов объединены и являются входом числа Б устройства, второй информационный вход первого коммутатора соединен с выходом третьего регистра и первым входом второго узла сравнения, второй вход которого объединен с входом первого узла , свертки по модулю три| вторым информационным входом второго коммутатора -и подключен к выходу четвертого регистра, который является выходом результата устройства, вход признака начала работы которого соединен с nepBbiM входом первого элемента И,

выход которого соединен с входами разрешения записи первого и второго регистров, с первыми входами первого, второго и третьего элементов ИЛИ,- с входом установки в О первого триггера и с входом первого зле- мента И первого элемента 2И-2ИЛИ, выход которого соединен с входом разрешения счета второго счетчика, выходы первого и второго разрядов

которого соединены соответственно с инверсным и прямым входами второго элемента И, выход которого соединен с первым входом третьего элемента И, с первыми входами первых элементов

И первого, второго, третьего и чет- вертого элементов ЗИ-2ИЛИ, с первым инверсным входом второго элемента И первого элемента 2И-2Ш1И и с первыми входами четвертого и пятого элементов И, вторые входы четвертого и пятого элементов И объединены и соединены с выходом младшего разряда первог9 счетчика и вторым инверсным входом первого элемента И

первого элемента ЗИ-2ИЛИ, выход которого соединен с входом разрешения счета первого счетчика, вход обнуления которого соединен с выходом третьего элемента ЗИ-2ИЛИ, с входом

установки в 1 . первого триггера, с входом установки в О второго триггера и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с вторым инверсным входом первого элемента И четвертого элемента ЗИ-2ИЛИ, с первым входом первого элемента И второго элемента 2И-2ИЛИ, с выходом пятого элемента И, с вторыми входами первого и второго элементов ИЛИ и с первым управляющим входом первого коммутатора, второй управляющий вход которого соединен с управляющим входом второго коммутатора, с вторым входом первого элемента И, с вторым инверсным входом второго элемента И первого элемента 2И-2ИЛИ, с выходом первого триггера и подключен к выходу признака занятости устройства, вход обнуления которого соединен с третьим инверсным входом первого элемента И, с входом второго элемента И третьего элемента ЗИ-2ИЛИ и с входом второго элемента И четвертого элемента ЗИ-2ШШ, выход которого соединен с входом обнуления третьего счетчика, вход разрешения счета которого соединен с выходом второго элемента 2И-2ИЛИ, второй инверсный вход первого элемента И и первый инверсный вход второго элемента И которого соединены с выходом равенства третьего узла сравнения и подключены к выходу устойчивой .ошибки устройства, вход задания начальных условий которого соединен с первым входом третьего узла сравнения, второй вход которого соединен с выходом третьего счетчика, второй вход третьего элемента И соединен с вторым инверсным входом первого элемента И второго элемента ЗИ-2ИЛИ, с вторым инверсным входом первого элемента И третьего элемента ЗИ-2И11И и с выходом неравенства четвертого узла сравнения, первьй вход которого соединен с выходом пятого регистра, информационный вход которого соединен с выходом первого узла свертки по модулю три и с входом первого слагаемого сумматора по модулю три, вход второго слагаемого которого соединен с выходом второго узла свертки по модулю три, вход которого соединен с выходом первого регистра, выход старшего разряда которого соединен с входом старшего разряда третьего слагаемого сумматора по модулю три, вход младшего разряда третьего слагаемого которого подключен к шине логического нуля, выход сумматора по модулю три соединен с вторым входом четвертого узла сравнения, выход второго триггера соединен с третьим входом третьего элемента И, с .третьим инверсным входом первого элемента И первого элемента ЗИ-2Ш1И, с третьим входом первого элемента И второго элемента ЗИ-2ИЛИ и с третьими инверсными входами четвертого и пятого элементов И, четвертый вход четвертого элемента

И соединен с выходом неравенства

второго узла сравнения, выход равенства которого соединен с четвертым входом пятого элемента И, выход четвертого элемента И соединен с входом

установки в 1 второго триггера и с входом второго элемента И второго элемента ЗИ-2ИЛИ, выход которого соединен с входом второго элемента И первого элемента ЗИ-2ИЛИ, с вторым

входом третьего элемента ИЛИ, с входом разрешения записи пятого регистра и является выходом признака корректного кода, выход третьего элемента И соединен с третьим входом

четвертого элемента ИЛИ, с третьим инверсным входом первого элемента И четвертого элемента ЗИ-2ИЛИ, с вторым входом второго элемента И второго элемента 2И-2Ш1И, с третьим входом

второго элемента ИЛИ и с третьим управляющим входом первого коммутатора, третий информационный вход которого соединен с информационными выходами сумматоров первого блока

сложения, вход обнуления регистра первого слагаемого и вход обнуления триггера переноса первого блока сложения соединены соответственно с выходом первого элемента ИЛИ и с выходом второго элемента 1ШИ, выход четвертого элемента ИЛИ соединен с входом обнуления второго счетчика, выход равенства первого узла сравнения соединен с третьим входом первого

элемента И третьего элемента ЗИ-2ИЛИ выходы второго коммутатора и выходы второго блока сложения соединены соответственно с информационными входами третьего и четвертого регистров,

выход первого коммутатора соединен с входом регистра второго слагаемого первого блока сложения, выход третьего элемента ШШ соединен с входом разрешения записи третьего регистра.

J7

If иг г

Редактор О. Головач

Составитель И. Иваныкин Техред В.Кадар

Заказ 7809/47 Тираж 694Подписное

ВНИИ11И Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная 4

Корректор В. Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор кодов с иррациональным основанием | 1991 |

|

SU1837279A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Конвейерное вычислительное устройство | 1984 |

|

SU1213475A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| "Генератор чисел в кодах "золотой" пропорции" | 1989 |

|

SU1711143A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1113790A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

Изобретение относится к вычислительной технике и может быть использовано в адресном тракте ЭВМ, в частности для генерации адресов объектов, регулярно расположенных в памя- ти по заданным базе, шагу и количеству объектов. Цель изобретения - повышение достоверности работы за счет Контроля вычисления функции (i-1)A,

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Конвейерное вычислительное устройство | 1984 |

|

SU1213475A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-07—Публикация

1984-07-11—Подача