Изобретение относится к технике налаживания блоков электрической аппаратуры, в частности к устройствам для контроля логических блоков, и может найти применение для программного контроля печатных плат.

Известно устройство для контроля логических блоков, содержащее формирователь сигналов ошибки, соединенный с шинами испытательных сигналов и с выходной шиной результата контроля [1]

Недостаток известного устройства для контроля логических блоков состоит в значительной погрешности результата контроля.

Наиболее близким по своей технической сущности к предлагаемому техническому решению является устройство для контроля логических блоков, содержащее триггер, подсоединенный входом установки нуля к входной шине опроса, дешифратор, входные шины данных, входные шины выбора данных, входную шину начала контроля, входную шину тактовых импульсов приема, входную шину тактовых импульсов сдвига, выходную шину результата контроля и шины испытательных сигналов [2]

Недостаток подобного устройства для контроля логических блоков состоит в значительной длительности процесса контроля печатных плат. Известное устройство не обеспечивает возможность подачи на любые выбранные контакты сложной высокочастотной кодовой последовательности без применения дополнительного генераторного оборудования с возможностью одновременного контроля состояния как выходных, так и входных контактов тестируемого логического блока.

Технический результата, который может быть получен при осуществлении предлагаемого технического решения, выражается в уменьшении длительности процесса контроля логических блоков.

Для обеспечения этого технического результата в устройство для контроля логических блоков, содержащее триггер, подсоединенный входом установки нуля к входной шине опроса, дешифратор, входные шины данных, входные шины выбора данных, входную шину тактовых импульсов приема, входную шину тактовых импульсов передачи, входную шину предшествующего состояния, выходную шину результата контроля и шины испытательных сигналов, введены первый, второй, третий, четвертый и пятый регистры, подсоединенные информационными входами к входным шинам данных и соединенные входами синхронизации с выходами дешифратора, который подсоединен информационными входами к входным шинам выбора данных и соединен с управляющим входом соответственно с входной шиной выбора блока и с входной шиной тактовых импульсов приема, шестой регистр, подключенный выходом к выходной шине результата контроля и соединенный входом последовательной записи с входной шиной предшествующего состояния, элементы И с тремя устойчивыми состояниями, соединенные выходами с шинами испытательных сигналов, первый и второй элементы И, подсоединенные первыми входами к входной шине тактовых импульсов сдвига, мультиплексоры, элементы Исключающее ИЛИ, седьмой регистр и дополнительные элементы И, причем выходы первого регистра соединены с первыми входами элементов И с тремя устойчивыми состояниями, соединенных вторыми входами с выходами мультиплексоров, а выход первого элемента И подключен к другому входу синхронизации третьего регистра, выход которого соединен с его входом последовательной записи и с информационными входами мультиплексоров, соединенных другими информационными входами с выходами седьмого регистра, подключенными к входам элементов Исключающее ИЛИ, соединенных другими входами с шинами испытательных сигналов и подключенных выходами к первым входам дополнительных элементов И, которые соединены вторыми входами с выходами пятого регистра и подключены выходами к информационным входам шестого регистра, соединенного первым и вторым входами синхронизации соответственно с входной шиной опроса и с выходом второго элемента И, подсоединенного вторым входом к инверсному выходу триггера, который соединен прямым выходом с вторым входом первого элемента И и подсоединен входом установки единицы к входной шине начала контроля, подключенной к входу синхронизации седьмого регистра, подсоединенного информационными входами к выходам их второго регистра.

Сопоставительный анализ приведенной выше совокупности существенных признаков, характеризующей предлагаемое техническое решение, и прототипа показал, что предлагаемое техническое решение является новым, так как оно не известно из уровня техники.

Сравнение предлагаемого технического решения не только с прототипом, но и с другими техническими решениями в этой области техники не позволило выявить в них признаки, отличающие предлагаемое техническое решение от прототипа, что позволяет сделать вывод о том, что предлагаемое техническое решение имеет изобретательский уровень, так как оно явным образом не следует из уровня техники.

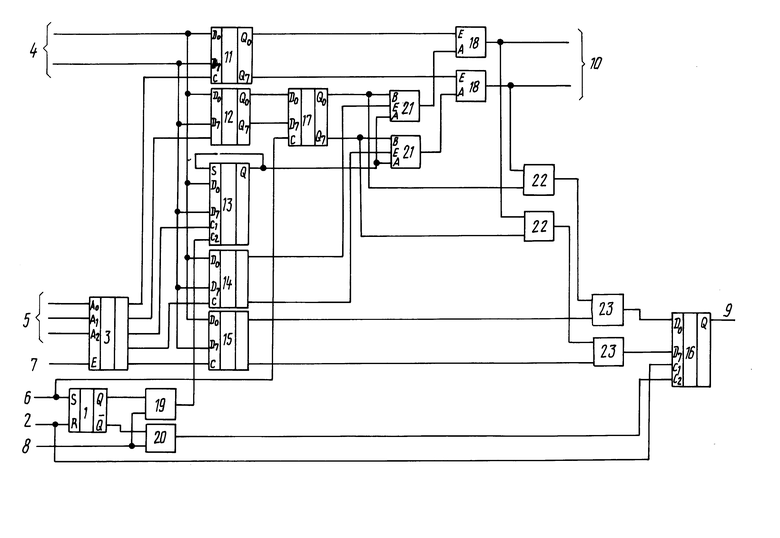

На чертеже изображен один из возможных вариантов предлагаемого устройства для контроля логических блоков.

Устройство содержит триггер 1, подсоединенный входом установки нуля к входной шине 2 опроса, дешифратор 3, входные шины 4 данных, входные шины 5 выбора данных, входную шину 6 начала контроля, входную шину 7 тактовых импульсов приема, входную шину 8 тактовых импульсов передачи, выходную шину 9 результата контроля и шины 10 испытательных сигналов.

Устройство содержит первый, второй, третий, четвертый и пятый регистры 11, 12, 13, 14, 15, подсоединенные информационными входами к входным шинам 4 данных и соединенные входами синхронизации с выходами дешифратора 3, шестой и седьмой регистры 16 и 17, элементы И 18 с тремя устойчивыми состояниями, первый и второй элементы И 19 и 20, мультиплексоры 21, элементы Исключающее ИЛИ 22 и дополнительные элементы И 23.

Дешифратор 3 подсоединен информационными входами к входным шинам 5 выбора данных и соединен управляющим входом с входной шиной 7 тактовых импульсов приема. Шестой регистр 16 подключен выходом к выходной шине 9 результата контроля. Элементы И 18 с тремя устойчивыми состояниями соединены выходами с шинами 10 испытательных сигналов. Первый и второй элементы И 19 и 20 подсоединены первыми входами к входной шине 8 тактовых импульсов передачи.

В устройстве выходы первого регистра 11 соединены с первыми входами элементов И 18 с тремя устойчивыми состояниями, соединенных вторыми входами с выходами мультиплексоров 21, а выход первого элемента И 19 подключен к другому входу синхронизации третьего регистра 13. Выход третьего регистра 13 соединен с его входом последовательной записи и с информационными входами мультиплексоров 21. Мультиплексоры 21 соединены другими информационными входами с выходами седьмого регистра 17, подключенными к входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 22. Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 22 соединены другими входами с шинами 10 испытательных сигналов и подключены выходами к первым входам дополнительных элементов И 23. Дополнительные элементы И 23 соединены вторыми входами с выходами пятого регистра 15 и подключены выходами к информационным входам шестого регистра 16. Шестой регистр 16 соединен первым и вторым входами синхронизации соответственно с входной шиной 2 опроса и с выходом второго элемента И 20, подсоединенного вторым входом к инверсному выходу триггера 1, который соединен прямым выходом с вторым входом первого элемента И 19 и подсоединен входом установки единицы к входной шине 6 начала контроля, подключенной ко входу синхронизации седьмого регистра 17, подсоединенного информационными входами к выходам второго регистра 12.

Работа предлагаемого устройства для контроля логических блоков происходит следующим образом.

Сигналом первого дешифратора 3 при наличии сигналов на входной шине 7 тактовых импульсов приема в соответствии с кодами трехфазной шины 5 выбора данных в первый, второй, третий, четвертый и пятый регистры 11, 12, 13, 14 и 15 производится запись кодов с восьмиразрядной входной шины 4 данных.

Причем, содержимое первого регистра 11 организует схему контроля в соответствии с разделением контактов тестируемого блока на входные и выходные, устанавливая выходы элементов И 18 в бестоковое высокоимпедансное состояние для выходных контактов. Информация второго регистра 12 состоит из свертки сигналов воздействия на входные контакты и эталона откликов с выходных контактов тестируемого блока. В третий регистр 13 записывается код последовательности, которая в соответствии с содержимым четвертого регистра 14, управляющим входами Е мультиплексоров 21, может быть выдана в качестве сигналов воздействия на любой из входных контактов блока.

Содержимое пятого регистра 15 определяет маскируемые контакты тестируемго блока, т.е. контакты, состояние которых не влияет на результаты тестирования.

Сигналом входной шины 6 начала контроля содержимое второго регистра 12 памяти переписывается в седьмой регистр памяти 17 и через мультиплексоры 21 и элементы И 18 поступает в качестве испытательных сигналов на восьмиразрядную шину 10 испытательных сигналов.

Причем, испытательные сигналы поступят только на те разряды выходной шины 10 испытательных сигналов, элементы И 18 которых не установлены в третье состояние. На выходные контакты тестируемого блока, отмеченные в содержимом четвертого регистра 14, через мультиплексоры 21 поступит последовательное логическое воздействие в соответствии с кодом третьего регистра13.

Этим же сигналом начала контроля входной шины 6 первый триггер 1 устанавливается в единичное состояние и высокочастотная серия импульсов передачи входной шины 8 тактовых импульсов передачи через первый элемент И 19 поступает на второй вход синхронизации третьего регистра 13, обеспечивая тем самым на выбранных контактах тестируемого блока наличие высокочастотной кодовой последовательности на фоне квазистатического состояния на невыбранных входных контактах.

Высокочастотная кодовая последовательность воздействует на выбранные входные контакты до появления сигнала на входной шине 2 опроса, сбрасывающего первый триггер 1 в нулевое состояние, переключая высокочастотную серию импульсов передачи входной шины 8 со входа синхронизации третьего регистра 13 на второй вход синхронизации сдвига шестого регистра 16 через второй элемент И 20.

Этим же сигналом опроса входной шины 2 по первому входу синхронизации параллельной записи производится запись через дополнительные элементы И 23 в шестой регистр 16 результата сверки на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 22 состояния всех контактов тестируемого блока с содержамым седьмого регистра 17.

Причем на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 22 производится сверка состояния входных контактов с требуемым тестовым логическим воздействием и сверка откликов на выходных контактах с эталоном откликов. Таким образом в процессе тестирования контролируются не только выходные, но и входные контакты блока.

Контакты, не подлежащие контролю, в коде пятого регистра 15 отмечены логическими нулями.

При совпадении состояния контакта тестируемого блока и содержимого, соответствующего этому контакту разряда седьмого регистра 17, на выходе одноименного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 вырабатывается сигнал логического нуля.

В результате тестирования сигналом входной шины 2 опроса, являющимся сигналом опроса состояния контактов тестируемого блока, в шестой регистр 16 записывается код, в котором логическими нулями отмечены контакты, состояние которых совпадает с ожидаемым, а логическими единицами контакты, состояние которых не совпадает с ожидаемым.

Результат сверки считывается в последовательном коде с выходной шины 9 результата контроля со скоростью, определяемой частотой тактовой последовательности входной шины 8 тактовых импульсов передачи.

Технико-экономическая эффективность предлагаемого устройства связана с уменьшением длительности процесса контроля логических блоков. Однако оценить экономический эффект от внедрения предлагаемого устройства в настоящее время не представляется возможным.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ БИИМПУЛЬСНОГО СИГНАЛА | 1992 |

|

RU2048706C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ | 1992 |

|

RU2018943C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2129338C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ | 1990 |

|

RU2029431C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1990 |

|

RU2007882C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 1990 |

|

RU2022453C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2090982C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДА | 1991 |

|

RU2010428C1 |

| УСТРОЙСТВО ДЛЯ ТАКТОВОЙ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 1992 |

|

RU2013015C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ЦИФРОВОГО СИГНАЛА В ДВУХПРОВОДНУЮ ЛИНИЮ СВЯЗИ | 1992 |

|

RU2019035C1 |

Изобретение используется для программного контроля печатных плат. Устройство содержит: триггер 1, входную шину 2 опроса, дешифратор 3, входные шины 4 данных, входные шины 5 выбора данных, входную шину 6 начала контроля, входную шину 7 тактовых импульсов приема, входную шину 8 тактовых импульсов передачи, выходную шину 9 результата контроля и шины 10 испытательных сигналов, регистры 11, 12, 13, 14, 15, 16, 17, элементы И с тремя устойчивыми состояниями, элементы И 19, 20, мультиплексоры 21, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 22, дополнительные элементы И 23. 1 ил.

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ, содержащее триггер, подсоединенный входом установки нуля к входной шине опроса, дешифратор, входные шины данных, входные шины выбора данных, входную шину начала контроля, входную шину тактовых импульсов приема, входную шину тактовых импульсов передачи, выходную шину результата контроля и шины испытательных сигналов, отличающееся тем, что в него введены первый пятый регистры, подсоединенные информационными входами к входным шинам данных и соединенные входами синхронизации с выходами дешифратора, который подсоединен информационными входами к входным шинам выбора данных и соединен управляющим входом с входной шиной тактовых импульсов приема, шестой регистр, подключенный выходом к выходной шине результата контроля, элементы И с тремя устойчивыми состояниями, соединенные выходами с шинами испытательных сигналов, первый и второй элементы И, подсоединенные первыми входами к входной шине тактовых импульсов передачи, мультиплексоры, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, седьмой регистр и дополнительные элементы И, причем выходы первого регистра соединены с первыми входами элементов И с тремя устойчивыми состояниями, соединенных вторыми входами с выходами мультиплексоров, соединенных входами управления с выходами четвертого регистра, выход первого элемента И подключен к другому входу синхронизации третьего регистра, выход которого соединен с его входом последовательной записи и с информационными входами мультиплексоров, соединенных другими информационными входами с выходами седьмого регистра, подключенными к входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, соединенных другими входами с шинами испытательных сигналов и подключенных выходами к первым входам дополнительных элементов И, которые соединены вторыми входами с выходами пятого регистра и подключены выходами к информационным входам шестого регистра, соединенного первым и вторым входами синхронизации соответственно с входной шиной опроса и с выходом второго элемента И, подсоединенного вторым входом к инверсному выходу триггера, который соединен прямым выходом с вторым входом первого элемента И и подсоединен входом установки единицы к входной шине начала контроля, подключенной к входу синхронизации седьмого регистра, подсоединенного информационными входами к выходам второго регистра.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сортировки плоских модулей и микросхем | 1984 |

|

SU1285640A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1995-11-10—Публикация

1992-08-04—Подача