ND

;о со сд

Изобретение относится к вычислительной технике, а именно к микропроцессорным устройствам с динамическим ОЗУ,

Цель изобретения - расширение функциональных возможностей за счет использования контроллера в ждущем режиме

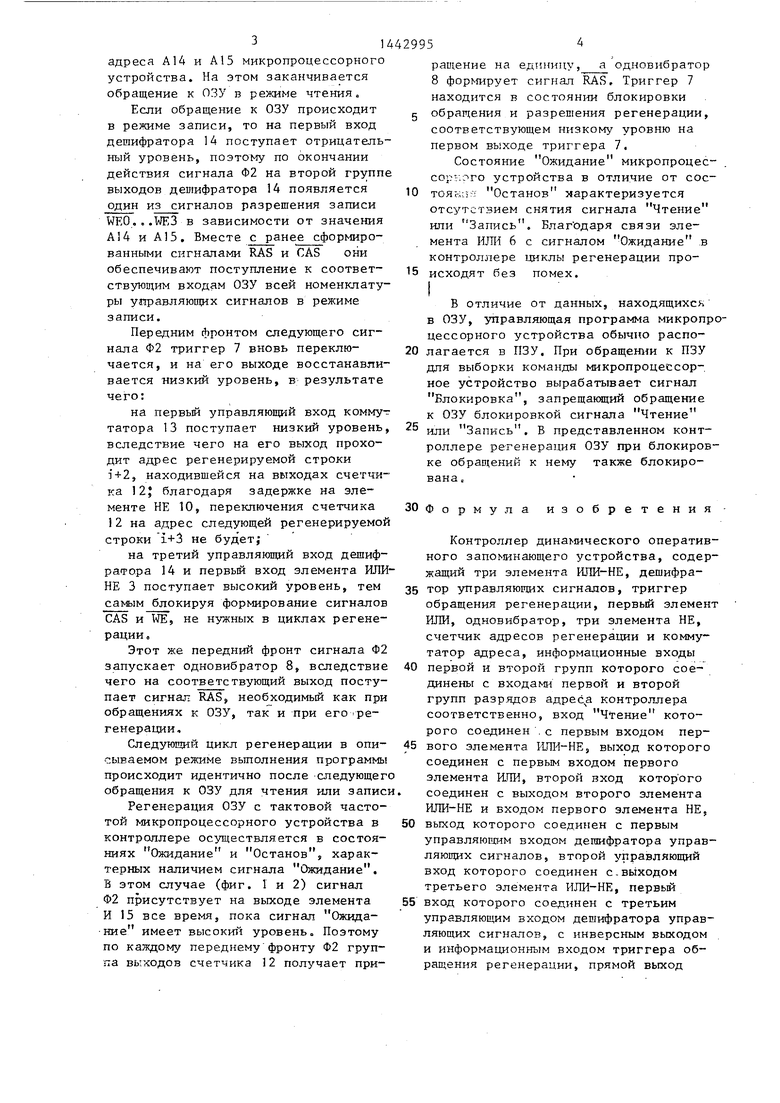

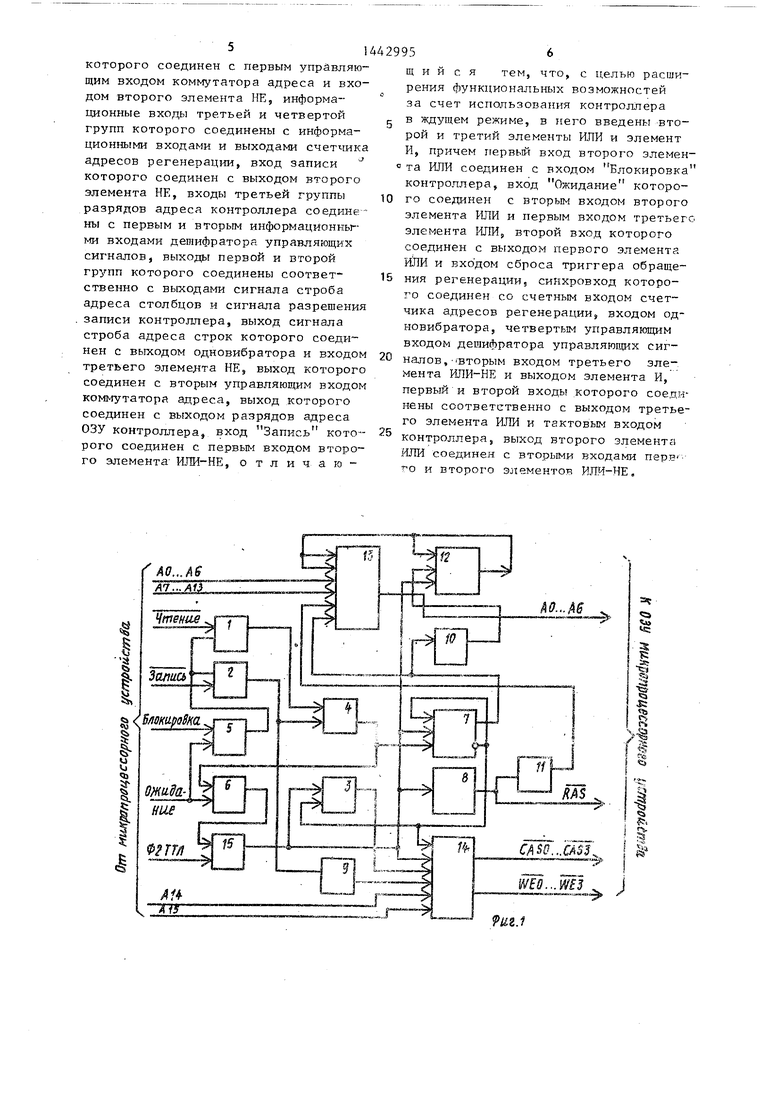

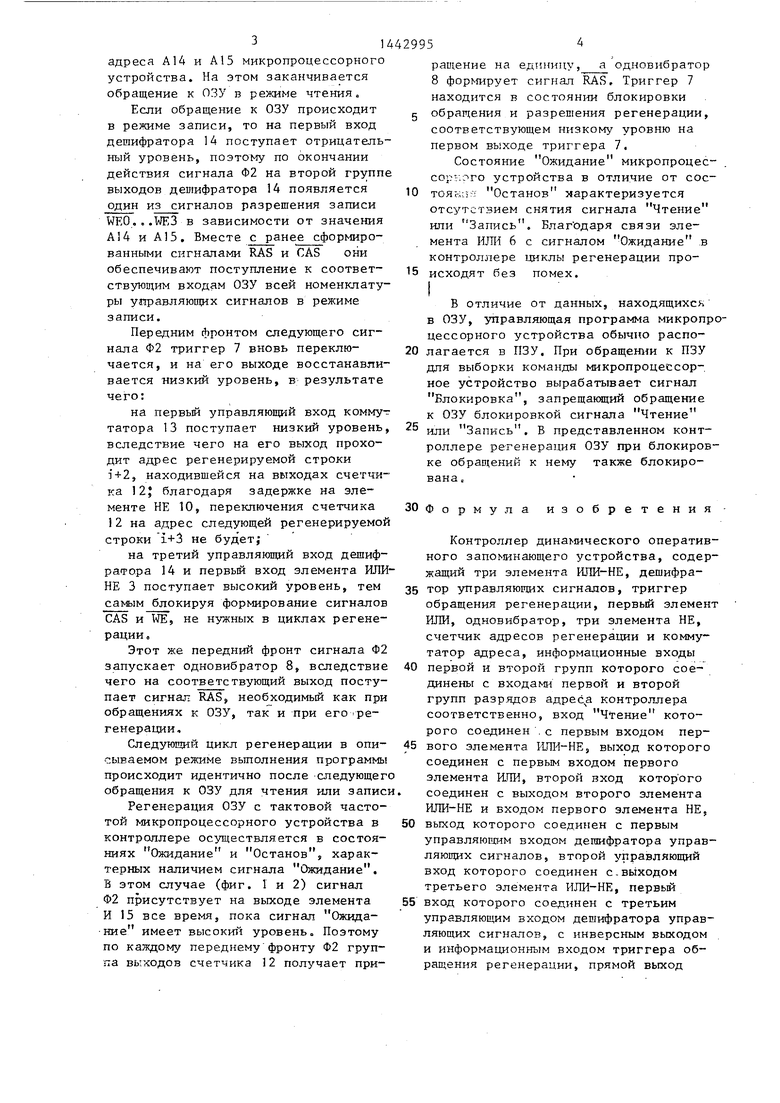

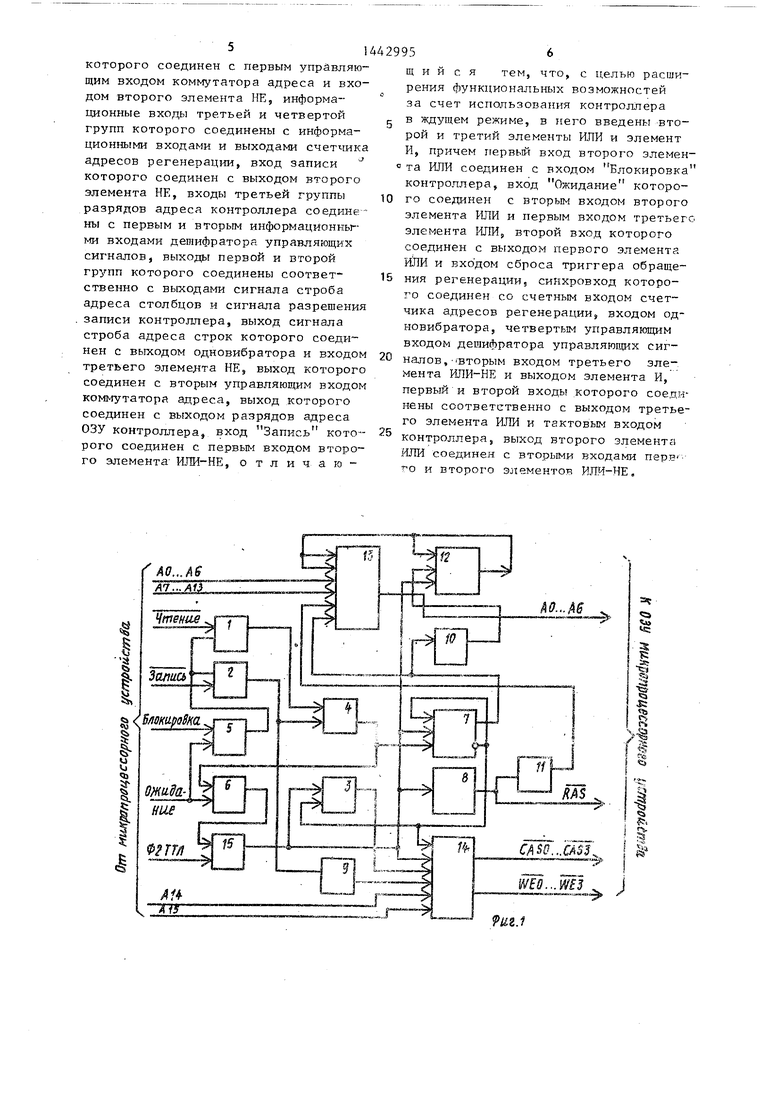

На фиг,1 приведена функциональная схема контроллера динамического ОЗУ; на фиг,2 - временная диаграмма работы контроллера.

Контроллер (фигЛ) содержит первый If второй 2 и третий 3 элементы ВДИ-НЕ, первый 4, второй 5 и третий 6 элементы ИЛИ, триггер 7 обращения регенерации, одновибратор 8, первый 9, второй 0 и третий П элементы НЕ счетчик 12 адресов регенерациИу комм татор 13 адреса, дешифратор 14 упраляющих сигналов, элемент И 15«

Контроллер предназначен для реализации обращений к ОЗУ в режимах чтения и записи и периодической регенерации информдции ОЗУо При этом регенерация обеспечивается в обычно;м режиме выполнения программы и в состояниях Оэ ;идание и Останов процессорного устройства

Рассмотрим работу контроллера в основном режиме - выполнение программы, характеризующемся отсутствием сигналов Ожидание и Блокировкг. (фиг,2), До поступления сигнала Чте ние или Запись на входе сброса триггера 7 - низкий уровень,, вследствие чего на входе записи счетчика 12- высокий уровеньJ разрешающий ,ро вание счетчика при условии поступле- НИН на синхровход счетчика 12 тактового сигнала Ф2„ На первый управляющий вход коммутатора 13 поступает низкий уровень с прямого выхода три; гера 7, поэтому адрес прсдадущей регенерированной строки i-i-1 будет поступать через коммутатор ,13 не выходы разрядов адреса АО...А6 ОЗУ устройства. Одновременно высокий уровень с инверсного выхода триггера 7j поступая на третий управляющими вход десшфратора 14 и на вход зле-- мента ИЛИ-НЕ 3, запрещает формкрсва- ние дешифратором 14 сигналов строба адреса столбцов CAS и разрешения записи WE.

С поступлениен сигнала Чтений или Зага-1сь тактовый сигнал Ф2 че-S

g

5 0

0

5 0 -S 0 5

рез элемент И 15 поступает на синхровход счетчика 12, в результате чего счетчик переключается и на информационных входах третьей группы коммутатора 13 появляется адрес следующей, ()-й строки, подлежащей регенерации. Поскольку тактовый сигнал Ф2 одновременно поступает на синхровход триггера 7, последний переключается, вследствие чего:

на первый управляющий вход коммутатора 13 поступает высокий уровеньj тем самым запрещая прохождение на группу выходов коммутатора 13 адреса следующей регенерируемой строки и разрешая прохождение на группу выходов коммутатора 13 мл.адших (АО,..А6) или старших (А7,,,А13) разрядов адреса ОЗУ, поступающих соответственно на первую и вторую группы входов коммутатора 13;

запускается одновибратор 8, на выходе которого появляется положительный импульс, после его инверсии на торой управляющий вход ;;оммут тор : 3 поступает отрицательньгй jiM,,b(. ri результате чего на выход ком г/та- тора 13 проходят разряды адреса АО,,,А6 от микропроцессорного устройства (фиг,2, М - младшие разряды);

на вход записи счетчика 12 через- элемент НЕ 10 отрицательный уровеньJ посредством которого текущее состояние группы выходов счетчика 2,, т,е, адрес строки i+2j зaпo mнaeтcя в счетчике 12;

на третий управ.пягоший вход п,ев;яог- ратора 14 поступает разреша Г ;; отрицательный уровень,

на первый вход элемента ИЛИ-НЕ 3 поступает отрицательный уровень.

По окончании действия выходтог: сигнала одновибрато э S сигня - с ,- ба адреса строк (RAS) поступай г Нй одноименный вход ОЗУ„ После зглзрк- ки на элементе НЕ 11 на второй управ- ляюший вход коммутатора 13 поступает положитёль гый уровень, в ре;лу, 1Ь гате чего на выход ко -1му атора 13 прохг дят разряды А7,., от микропроцег; сорного устройства (фиг,2, С стар - шие разряды),

По окончании действия сигнала Ф2 на первой группе выходов дешифратора 14 появляется один из сигналов стро- За адреса столбцов СЛЗ О . t.. в зависимости от значения разрядо ч

31

адреса А14 и А15 микропроцессорного устройства. На этом заканчивается обращение к ОЗУ в режиме чтения.

Если обращение к ОЗУ происходит в режиме записи, то на первый вход дешифратора 14 поступает отрицательный уровень, поэтому по окончании действия сигнала Ф2 на второй групп выходов дешифратора 14 появляется один из сигналов разрешения записи WEO,..WE3 в зависимости от значения А14 и А15. Вместе с ранее сформироони

ванными сигналами RAS и CAS обеспечивают поступление к соответствующим входам ОЗУ всей номенклатуры управляющих сигналов в режиме записи.

Передним фронтом следующего сигнала Ф2 триггер 7 вновь переключается, и на его выходе восстанавливается низкий уровень, в результате чего:

на первьй управляющий вход комму

В отличие от данных, находящихся в ОЗУ, управляющая программа микропро цессорного устройства обычно распо- 20 лагается в ПЗУ. При обращении к ПЗУ для выборки команды микропроцессорное устройство вырабатывает сигнал Блокировка, запрещакяций обращение к ОЗУ блокировкой сигнала Чтение

татора 13 поступает низкий уровень, 25 Запись. В представленном конт- вследствие чего на его выход проходит адрес регенерируемой строки i-i-2, находившейся на выходах счетчика 12; благодаря задержке на элементе НЕ 10, переключения счетчика 12 на адрес следующей регенерируемой строки i+3 не будет;

на третий управляющий вход дешифратора 14 и первый вход элемента ИЛИ- НЕ 3 поступает высокий уровень, тем блокируя формирование сигналов

роллере регенерация ОЗУ при блокировке обращений к нему также блокирована

30 Форму л а изобретения

Контроллер динамического оперативного запоминающего устройства, содержащий три элемента ИЛИ-НЕ, дешифра35 тор управляюшцх сигналов, триггер

обращения регенерации, первый элемент ИЛИ, одновибратор, три элемента НЕ, счетчик адресов регенерации и коммутатор адреса, информационные входы

CAS и WE, не нужных в циклах регенерации.

Этот же передний фронт сигнала Ф2 запускает одновибратор 8, вследствие чего на соответствующий выход поступает сигнал RAS, нeoбJ coдимьш как при обращениях к ОЗУ, так и при его .регенерации.

Следующий цикл регенерации в описываемом режиме вьтолнения программы происходит идентично после -следующег обращения к ОЗУ для чтения или запис

Регенерация ОЗУ с тактовой частотой микропроцессорного устройства в контроллере осуществляется в состояниях Ожидание и Останов, характерных наличием сигнала Ожидание. Б этом случае (фиг. 1 и 2) сигнал Ф2 присутствует на выходе элемента И 15 все время, пока сигнал Ожидание имеет высокий уровень. Поэтому по каждому переднему фронту Ф2 группа выходов счетчика 12 получает приращение на единицу, а одновибратор

8 формирует сигнал RAS, Триггер 7 находится в состоянии блокировки обращения и разрешения регенерации, соответствующем низкому уровню на первом выходе триггера 7.

Состояние Ожидание микропроцес сорг.ого устройства в отличие от сос- тоя-гл:- ;-; Останов марактеризуется отсутствием снятия сигнала Чтение Ш1И Запись. Благ одаря связи элемента ИЛИ 6 с сигналом Ожидание .в контроллере даклы регенерации происходят без помех.

В отличие от данных, находящихся в ОЗУ, управляющая программа микропроцессорного устройства обычно распо- 20 лагается в ПЗУ. При обращении к ПЗУ для выборки команды микропроцессорное устройство вырабатывает сигнал Блокировка, запрещакяций обращение к ОЗУ блокировкой сигнала Чтение

25 Запись. В представленном конт-

Запись. В представленном конт-

роллере регенерация ОЗУ при блокировке обращений к нему также блокирована

Форму л а изобретения

Контроллер динамического оперативного запоминающего устройства, содержащий три элемента ИЛИ-НЕ, дешифратор управляюшцх сигналов, триггер

обращения регенерации, первый элемент ИЛИ, одновибратор, три элемента НЕ, счетчик адресов регенерации и коммутатор адреса, информационные входы

первой и второй групп которого соединены с входами первой и второй групп разр.ядов адреска контроллера соответственно, вход Ч гение которого соединен . с первым входом первого элемента ИЛИ-НЕ, выход которого соединен с первым входом первого элемента ИЛИ, второй вход котор ого соединен с выходом второго элемента ИЛИ-НЕ и входом первого элемента НЕ,

выход которого соединен с первым

управляюшим входом дешифратора управляющих сигналов, второй управляющий вход которого соединен с.выходом третьего элемента ИЛИ-НЕ, первьй

ход которого соединен с третьим

правляющим входом дешифратора управяющих сигналов, с инверсным выходом информационным входом триггера обащения регенерации, прямой выход

которого соединен с первым управляющим входом коммутатора адреса и входом второго элемента НЕ, информационные входы третьей и четвертой групп которого соединены с информационными входами и выходами счетчика адресов регенеращт, вход записи которого соединен с выходом второго элемента НЕ, входы третьей группы разрядов адреса контроллера соединены с первым и вторым информационными входами дешифратора управляющих сигналов, выходы первой и второй групп которого соединены соответ- ственно с выходами сигнала строба адреса столбцов и сигнала разрешения записи контроллера, выход сигнала строба адреса строк которого соединен с выходом одновибратора и входом третьего элемента НЕ, выход которого соединен с вторым управляющим входом коммутатора адреса, выход которого соединен с выходом разрядов адреса ОЗУ контроллера, вход Запись кото- рого соединен с первым входом второго элемента- ИЛИ-НЕ, отличающий с я тем, что, с целью расширения функциональных возможностей за счет использования контроллера в ждущем режиме, в него введены второй и третий элементы ИЛИ и элемент И, причем первый вход второго элемен- та ИЛИ соединен с входом Блокировка контроллера, вход Ожидание которого соединен с вторым входом второго элемента ИЛИ и первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента и входом сброса триггера обращения регенерации, синхровход которого соединен со счетным входом счетчика адресов регенерации, входом одновибратора, четвертым управляющим входом дешифратора управляющих сигналов, вторым входом третьего элемента ИЛИ-НЕ и выходом элемента И, первый и второй входы которого соединены соответственно с выходом третьего элемента ИЛИ и тактовым входом контроллера, выход второго элемента ИЛИ соединен с вторыми входами перБ-- го и второго элементов ИЛИ-НЕ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления памятью | 1983 |

|

SU1151975A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для синхронизации обмена микропроцессора с памятью отображения | 1989 |

|

SU1786489A1 |

| Устройство для управления памятью | 1980 |

|

SU962963A1 |

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ЗНАКОВ НА ЭКРАНЕ ТЕЛЕВИЗИОННОГО ИНДИКАТОРА | 1991 |

|

RU2023314C1 |

| Устройство для преобразования сейсморазведочной информации | 1987 |

|

SU1497599A1 |

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

Изобретение относится к вычислительной технике, а именно к микропроцессорным устройствам с динамическим ОЗУ. Цель изобретения - расширение функциональных возможностей за счет использования контроллера в ждущем режиме. Контроллер содержит первый, второй и третий элементы ИЛИ-НЕ, дешифратор управляющих сигналов, триггер обращения(регенерации, элемент ИЛИ, одновибратор, три эле мента НЕ, счетчик адресов регенерации, коммутатор адреса. Новым в контроллере является введение второго и третьего элементов ИЛИ и элемента И. Контроллер реяпизует обра- ;щения к ОЗУ в режимах чтения и записи и периодической регенерации информации ОЗУ. При этом рёгеиерация обеспечивается в обычном режиме выполнения программы, состояниях ОЖИДАНИЕ и ОСТАНОВ микропроцессорного устройства и состоянии блокировки обращений к ОЗУ. Период регенерации, в котором количество циклов регенерации равно количеству обращений к ОЗУ, зависит от конкретной программа. Частота регенерации снижается более чем на порядок, значительно уменьшая мощность, затрачиваемую на регенерацию. 2 ил. с (Л

«а

f

§ Ж:

«ts

R

S

f&

.

9U.Z.1

| Козевич О.П | |||

| и др | |||

| Применение динамических ОЗУ в микропродессорных системах | |||

| - Вопросы радиоэлектроники | |||

| Сер | |||

| ЭВТ, 1981, вьт | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

| Еремин Ю.А., Морозов А.Г | |||

| Контроллер динамического ОЗУ для микропроцессорных устройств | |||

| - Микропроцессорные средства и системы, 1986, № 3, с | |||

| Фальцовая черепица | 0 |

|

SU75A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-12-07—Публикация

1987-04-01—Подача