Изобретение относится к вычислительной технике и может быть использовано для выявления циклических процессов анализируемой программы, регистрации их параметров (адресов команд начала и конца цикла, количества повторений и времени выполнения цикла) и хранения регистрируемой информации в блоке памяти с последующей выдачей по запросу. Эта информация необходима для верификации разрабатываемых программ и выбора оптимального внутреннего языка проектируемой ЭВМ.

Целью изобретения является сокращение времени выдачи результатов регистрации параметров циклов, а также сокращение аппаратных затрат.

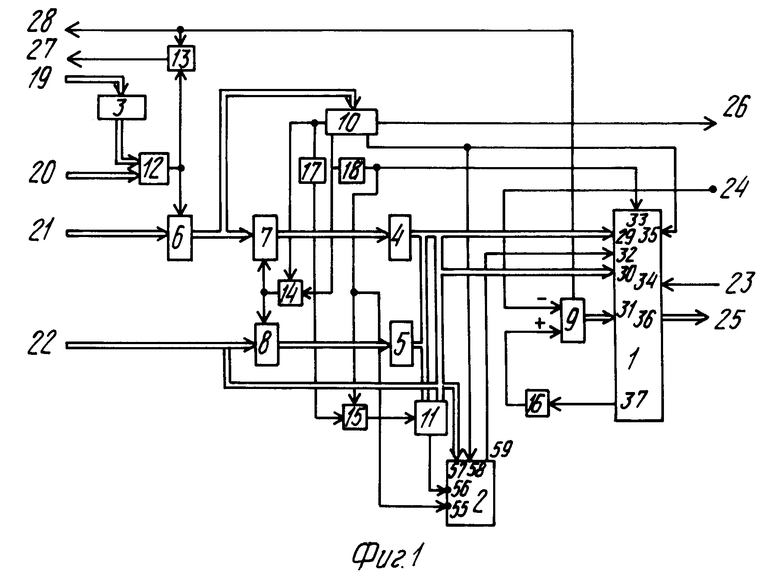

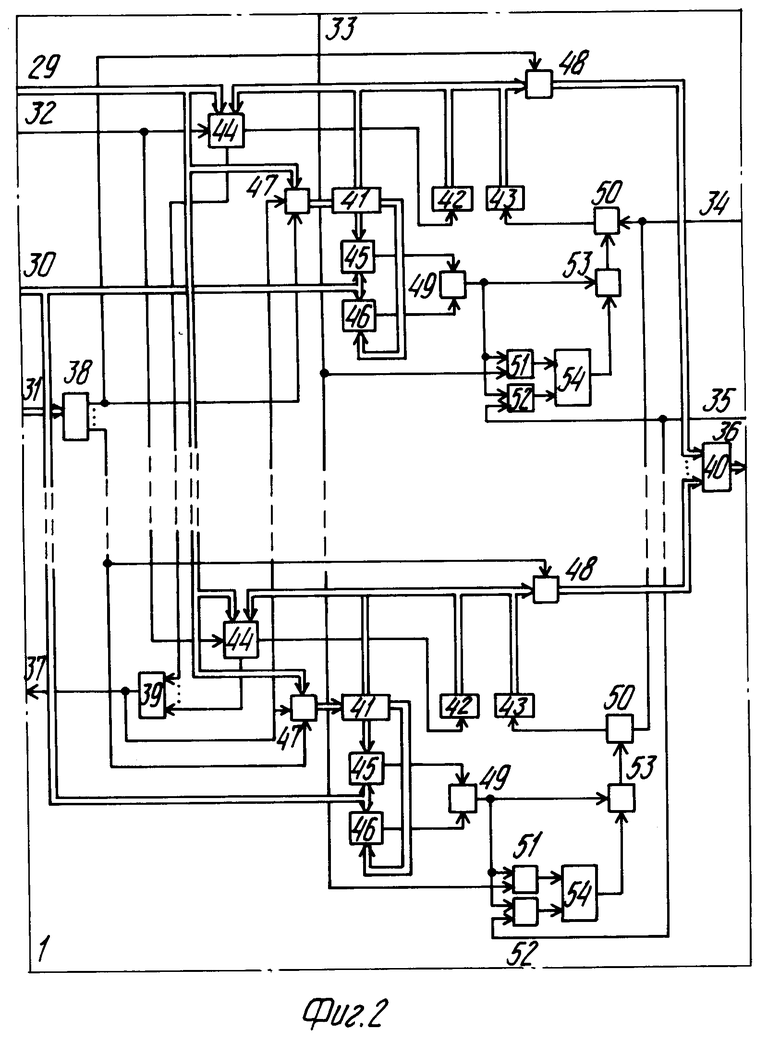

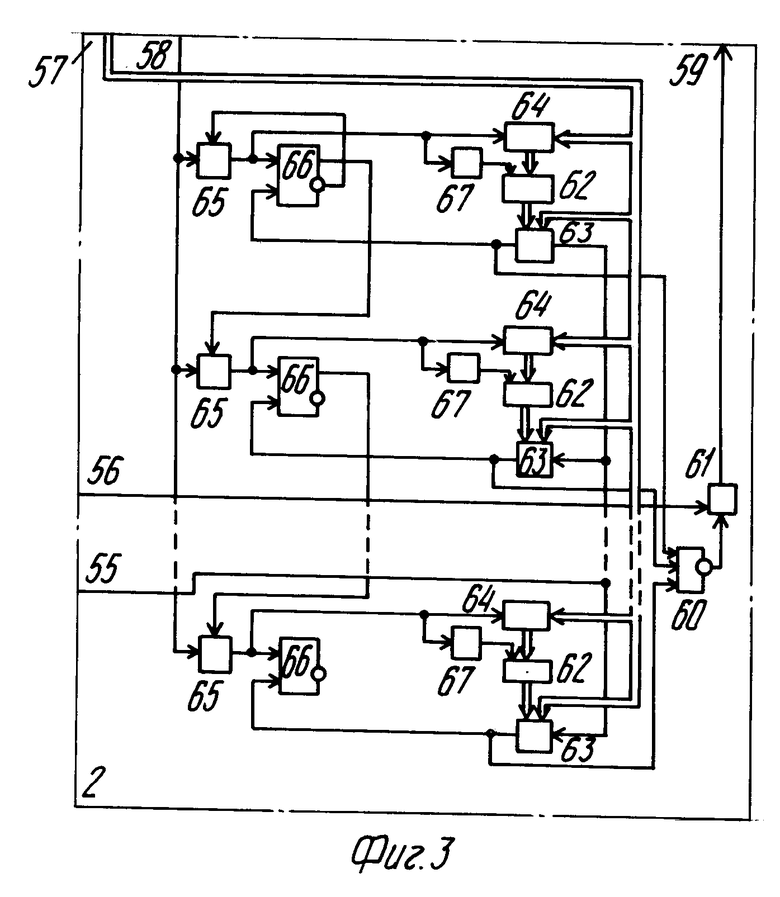

На фиг. 1 показана блок-схема устройства; на фиг.2 схема блока буферной памяти; на фиг.3 -схема блока ассоциативной памяти.

Устройство для отладки программ содержит (фиг.1) блок 1 буферной памяти (БП), блок 2 ассоциативной памяти (АП), регистр 3 ключа защиты, регистр 4 кода команды, регистр 5 адреса команды, группы 6-8 элементов И, реверсивный счетчик 9 адреса, дешифратор 10 команд, схемы 11, 12 сравнения, элемент И 13, элементы ИЛИ 14 и 15, элементы 16-18 задержки, группы 19-22 информационных входов устройства, управляющие входы 23 и 24 устройства, группу 25 информационных выходов устройства, выходы 26-28 устройства.

Блок 1 буферной памяти содержит (фиг.2) группы 29 и 30 информационных входов, группу 31 адресных выходов, входы 32-35 блока, группу 36 информационных выходов, выход 37, дешифратор 38 адреса, элемент И 39, группу 40 элементов ИЛИ и N запоминающих ячеек (N количество циклов, регистрируемых устройством), каждая из которых включает регистр 41 цикла, счетчик 42 цикла, счетчик 43 времени, схемы 44-46 сравнения, группы 47 и 48 элементов И, элементы И 49-52, элемент ИЛИ 53 и триггер 54.

Блок 2 ассоциативной памяти содержит (фиг.3) входы 55 и 56 блока, группу 57 информационных входов, вход 58 блока, выход 59, элемент ИЛИ-НЕ 60, элемент И 61 и М ячеек (М максимально допустимое количество вложенных друг в друга модулей программ), каждая из которых включает счетчик 62 адреса возврата, схему 63 сравнения, группу 64 элементов И, элемент И 65, триггер 66 и элемент 67 задержки.

Группа информационных входов 22 устройства соединена с информационными входами группы элементов И 8, выходы которых соединены с группой информационных входов регистра 5 адреса команды, группа выходов которого соединена с соответствующими входами первого сравниваемого числа схем 44 сравнения каждой запоминающей ячейки блока 1, выходы группы элементов ИЛИ 40 блока 1 являются группой информационных выходов 25 устройства, выход элемента И 39 блока 1 через элемент задержки 16 соединен с суммирующим входом реверсивного счетчика 9 адреса, вход чтения устройства 24 соединен с вычитающим входом реверсивного счетчика 9 адреса, группа информационных выходов реверсивного счетчика адреса 9 соединена с группой входов дешифратора адреса 38 блока 1, группа информационных входов 21 устройства соединена с информационными входами группы элементов И 6, выходы которых соединены с информационными входами группы элементов И 7 и с входами дешифратора 10 команд, выходы группы элементов И 7 соединены с информационными входами регистра 4 кода команд, выходы которого соединены с входами соответствующих элементов И 47 и соответствующими входами первого сравниваемого числа схемы 44 сравнения всех запоминающих ячеек блока 1, группы информационных входов 29 и 19 устройства соединены соответственно с группой входов первого сравниваемого числа схемы 12 сравнения и группой информационных входов регистра ключа защиты 3, выход которого соединен с входом второго сравниваемого числа схемы 12 сравнения, выход схемы сравнения 12 соединен с входом элемента И 13 и с входами элементов И 6, выход элемента И 13 является выходом ошибки устройства, группа информационных входов 22 устройства соединена с группой информационных входов 57 блока 2 ассоциативной памяти, с группой входов первого сравниваемого числа схемы 11 сравнения, с группой входов первого сравниваемого числа схем 45 и 46 сравнения всех запоминающих ячеек блока 1, с входами соответствующих элементов И 47 и соответствующими входами первого сравниваемого числа схемы 44 сравнения всех запоминающих ячеек блока 1, первый, второй, третий и четвертый выходы дешифратора 10 команд соединены соответственно с первым входом элемента ИЛИ 14, с вторым входом элемента ИЛИ 14, с входом обращения блока 2 ассоциативной памяти и с выходом останова устройства, первый, второй и третий выходы дешифратора 10 команд соединены соответственно через элемент задержки 17 с первым входом элемента ИЛИ 15, через элемент задержки 18 с вторым входом элемента ИЛИ 15, с первым входом элемента И 52 всех запоминающих ячеек блока 1, выход элемента задержки 18 соединен с тактовым входом 55 блока 2 и с первым входом элемента И 51 всех запоминающих ячеек блока 1, выход элемента ИЛИ 14 соединен с входами групп элементов И 8 и 7, выход элемента ИЛИ 15 соединен с тактовым входом схемы сравнения 11, выход равенства которой соединен с входом 56 считывания блока 2, выход признака которого соединен с тактовым входом 32 схемы сравнения 44 всех запоминающих ячеек блока 1, вход 23 меток времени устройства соединен с первым входом элемента И 50 всех запоминающих ячеек блока 1, выход переполнения реверсивного счетчика адреса 9 соединен с вторым входом элемента И 13 и является выходом 28 конца чтения устройства, группа информационных выходов регистра 5 адреса команды соединена с группой входов второго сравниваемого числа схемы сравнения 11, i-й выход дешифратора адреса 38 блока 1 (i  ) соединен с первыми входами групп элементов И 47, 48 i-й запоминающей ячейки блока 1, выходы группы элементов И 48 i-й запоминающей ячейки блока 1 соединены с i-ми входами элементов ИЛИ 40 группы блока 1 памяти, выход неравенства схемы 44 сравнения i-й запоминающей ячейки блока 1 соединен с i-м входом элемента И 39 блока 1, вторые входы группы элементов И 47 каждой запоминающей ячейки блока 1 соединены с выходом элемента И 39 блока 1, группа информационных выходов регистра 5 адреса команды соединена с третьими входами соответствующей группы элементов И 47 всех запоминающих ячеек блока 1, выходы группы элементов И 47 i-й запоминающей ячейки соединены с информационными входами регистра цикла 41 i-й запоминающей ячейки, информационные выходы регистра цикла 41 i-й запоминающей ячейки соединены с входами второго сравниваемого числа схемы сравнения 44 i-й запоминающей ячейки, информационные выходы регистра цикла 41 и счетчика циклов 42 i-й запоминающей ячейки соединены с вторыми входами соответствующей группы элементов И 48, выход равенства схемы сравнения 44 i-й запоминающей ячейки соединен со счетным входом счетчика циклов 42 i-й запоминающей ячейки блока 1, выходы кода адреса конца цикла и начала цикла регистра цикла 41 i-й запоминающей ячейки соединены с входами второго сравниваемого числа соответственно схем сравнения 45 и 46 i-й запоминающей ячейки, выходы "Меньше" и "Больше" схем сравнения 45 и 46 i-й запоминающей ячейки соединены соответственно с первым и вторым входами элемента И 49 i-й запоминающей ячейки, выход которого соединен с вторыми входами элементов И 52 и 51 и первым входом элемента ИЛИ 53 i-й запоминающей ячейки, выходы элементов И 51 и 52 i-й запоминающей ячейки соединены соответственно с входами установки "нуля" и "единицы" триггера i-й запоминающей ячейки, прямой выход которого соединен с вторым входом элемента ИЛИ 53 i-й запоминающей ячейки, выход которого соединен с вторым входом элемента И 50 i-й запоминающей ячейки, выход которого сравнен со счетным входом счетчика сравнения 43 i-й запоминающей ячейки, выходы счетчика времени 42 i-й запоминающей ячейки соединены с вторыми входами соответствующей группы элементов И 48 i-й запоминающей ячейки, группа информационных входов 57 блока 2 соединена с информационными входами всех групп элементов И 64 и группой входов первого сравниваемого числа всех схем сравнения 63, тактовый вход 55 блока 2 соединен с тактовыми входами всех схем сравнения 63, выход К-го счетчика 62 адреса возврата (К

) соединен с первыми входами групп элементов И 47, 48 i-й запоминающей ячейки блока 1, выходы группы элементов И 48 i-й запоминающей ячейки блока 1 соединены с i-ми входами элементов ИЛИ 40 группы блока 1 памяти, выход неравенства схемы 44 сравнения i-й запоминающей ячейки блока 1 соединен с i-м входом элемента И 39 блока 1, вторые входы группы элементов И 47 каждой запоминающей ячейки блока 1 соединены с выходом элемента И 39 блока 1, группа информационных выходов регистра 5 адреса команды соединена с третьими входами соответствующей группы элементов И 47 всех запоминающих ячеек блока 1, выходы группы элементов И 47 i-й запоминающей ячейки соединены с информационными входами регистра цикла 41 i-й запоминающей ячейки, информационные выходы регистра цикла 41 i-й запоминающей ячейки соединены с входами второго сравниваемого числа схемы сравнения 44 i-й запоминающей ячейки, информационные выходы регистра цикла 41 и счетчика циклов 42 i-й запоминающей ячейки соединены с вторыми входами соответствующей группы элементов И 48, выход равенства схемы сравнения 44 i-й запоминающей ячейки соединен со счетным входом счетчика циклов 42 i-й запоминающей ячейки блока 1, выходы кода адреса конца цикла и начала цикла регистра цикла 41 i-й запоминающей ячейки соединены с входами второго сравниваемого числа соответственно схем сравнения 45 и 46 i-й запоминающей ячейки, выходы "Меньше" и "Больше" схем сравнения 45 и 46 i-й запоминающей ячейки соединены соответственно с первым и вторым входами элемента И 49 i-й запоминающей ячейки, выход которого соединен с вторыми входами элементов И 52 и 51 и первым входом элемента ИЛИ 53 i-й запоминающей ячейки, выходы элементов И 51 и 52 i-й запоминающей ячейки соединены соответственно с входами установки "нуля" и "единицы" триггера i-й запоминающей ячейки, прямой выход которого соединен с вторым входом элемента ИЛИ 53 i-й запоминающей ячейки, выход которого соединен с вторым входом элемента И 50 i-й запоминающей ячейки, выход которого сравнен со счетным входом счетчика сравнения 43 i-й запоминающей ячейки, выходы счетчика времени 42 i-й запоминающей ячейки соединены с вторыми входами соответствующей группы элементов И 48 i-й запоминающей ячейки, группа информационных входов 57 блока 2 соединена с информационными входами всех групп элементов И 64 и группой входов первого сравниваемого числа всех схем сравнения 63, тактовый вход 55 блока 2 соединен с тактовыми входами всех схем сравнения 63, выход К-го счетчика 62 адреса возврата (К  ) соединен с группой входов второго сравниваемого числа К-й схемы сравнения 63, выход "Равно" К-й схемы сравнения 63 соединен с входом установки "нуля" К-го триггера 66 и с К-м входом элемента ИЛИ-НЕ 60, выход которого соединен с входом элемента И 61, вход 56 блока 2 соединен с входом элемента И 61, выход которого является выходом 59 признака блока 2, вход 58 обращения блока 2 соединен с входом М элементов И 65, инверсный выход первого триггера 66 соединен с входом триггера И 65, единичный выход К-го триггера 66 соединен с входом (К+1)-го элемента И 65, выход К-го элемента И 65 соединен с единичным входом К-го триггера 66, с входами элементов И 64 К-й группы и через К-й элемент задержки 67 со счетным входом К-го счетчика 62 адреса возврата, выходы элементов И 64 К-й группы соединены с информационными входами счетчика 62 адреса возврата.

) соединен с группой входов второго сравниваемого числа К-й схемы сравнения 63, выход "Равно" К-й схемы сравнения 63 соединен с входом установки "нуля" К-го триггера 66 и с К-м входом элемента ИЛИ-НЕ 60, выход которого соединен с входом элемента И 61, вход 56 блока 2 соединен с входом элемента И 61, выход которого является выходом 59 признака блока 2, вход 58 обращения блока 2 соединен с входом М элементов И 65, инверсный выход первого триггера 66 соединен с входом триггера И 65, единичный выход К-го триггера 66 соединен с входом (К+1)-го элемента И 65, выход К-го элемента И 65 соединен с единичным входом К-го триггера 66, с входами элементов И 64 К-й группы и через К-й элемент задержки 67 со счетным входом К-го счетчика 62 адреса возврата, выходы элементов И 64 К-й группы соединены с информационными входами счетчика 62 адреса возврата.

Устройство работает следующим образом.

В исходном состоянии регистры 4 и 5, реверсивный счетчик 9 адреса, а в каждой запоминающей ячейке блока 1 БП регистр 41, счетчики 42 и 43, триггер 54, а в каждой ячейке блока 2 АП счетчик 62 и триггер 66 находятся в нулевом состоянии.

Перед началом работы по группе 19 входов устройства в регистр 3 ключа защиты заносится код ключа защиты анализируемой программы, параметры циклов которой регистрируются в БП. Устройство готово к работе.

Возможны два режима работы устройства. Работа устройства в 1-м режиме (регистрации параметров циклов анализируемой программы) аналогична работе устройства, описанного в авт.ст. СССР N 1348840.

Во 2-м режиме (считывания) устройство работает следующим образом. По управляющему входу 24 устройства из ЭВМ на первый счетный вход (вычитающий) реверсивного счетчика 9 адреса поступают сигналы выдачи, каждый из которых выдается после считывания содержимого очередной ячейки БП с группы 25 информационных выходов устройства. В отличие от прототипа, содержимое реверсивного счетчика 9 адреса в конце работы устройства в первом режиме не сбрасывается. В результате остается возбужденной та выходная шина дешифратора 38 адреса БП, по разрешающему сигналу которой в ячейку памяти была занесена информация о последнем цикле анализируемой программы. Так как шина соединена с разрешающим входом группы 48 элементов И соответствующей ячейки, то начинается считывание информации из данной ячейки памяти. По окончании считывания на управляющий вход 24 поступает сигнал выдачи, который уменьшает содержимое счетчика на единицу. Этим достигается поочередное (от N до 1) считывание содержимого регистра 41, счетчика 42, счетчика 43 времени очередной ячейки БП через группу 40 элементов ИЛИ на группу 36 информационных выходов БП и далее на группу 25 информационных выходов устройства.

Сигналы выдачи поступают на первый счетный вход реверсивного счетчика 9 адреса до тех пор, пока сигнал его переполнения (наличие нулевого значения в cчетчике) не будет выдан на управляющий выход 28 устройства, сигнализируя об окончании работы устройства во втором режиме.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1985 |

|

SU1348840A1 |

| Устройство для измерения частот появления групп команд | 1986 |

|

SU1405062A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Устройство для формирования управляющей информации при обработке данных сейсмических колебаний | 1981 |

|

SU1000766A1 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

Изобретение относится к вычислительной технике и может быть использовано для выявления циклических процессов анализируемой программы, регистрации их параметров и хранения регистрируемой информации в блоке памяти с последующей выдачей по запросу. Цель изобретения сокращение времени выдачи результатов регистрации параметров циклов и аппаратных затрат. Устройство содержит схему управления, обеспечивающую управление устройством для отладки программ, блок буферной памяти, обеспечивающий хранение регистрируемой информации, а также блок ассоциативной памяти, обеспечивающий фиксацию переходов к подпрограммам и возвратов к основной программе. 3 ил.

УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ, содержащее блок буферной памяти, блок ассоциативной памяти, регистр адреса команды, регистр ключа защиты программы, регистр кода команды, реверсивный адрес команды, реверсивный счетчик адреса, первую, вторую и третью группы элементов И, первый и второй элементы ИЛИ, первый, второй и третий элементы задержки, первую и вторую схемы сравнения, дешифратор команд, элемент И, причем блок буферной памяти содержит дешифратор адреса, элемент И, группу элементов ИЛИ и N запоминающих ячеек, где N максимальное количество циклов исследуемой программы, а каждая запоминающая ячейка содержит первую, вторую и третью схемы сравнения, регистр цикла, счетчик времени, первую и вторую группы элементов И, четыре элемента И, элемент ИЛИ и триггер, блок ассоциативной памяти содержит элемент ИЛИ-НЕ, M элементов И (M максимально допустимое количество вложенных друг в друга модулей программы), M триггеров, M элементов задержки, M счетчиков адресов возврата, M групп элементов И, M схем сравнения, (M + 1)-й элемент И, причем первая группа информационных входов устройства соединена с первыми входами элементов И первой группы, выходы которых соединены с группой информационных входов регистра адреса команды, группа выходов регистра адреса команды соединена с соответствующими входами первого сравниваемого числа первой схемы сравнения каждой запоминающей ячейки блока буферной памяти, выходы элементов ИЛИ группы блока буферной памяти являются группой информационных выходов устройства, группа информационных выходов реверсивного счетчика адреса соединена с группой входов дешифратора адреса блока буферной памяти, вторая группа информационных входов устройства соединена с первыми входами элементов И второй группы, выходы которых соединены с первыми входами элементов И третьей группы и входами дешифратора команд, выходы элементов И третьей группы соединены с информационными входами регистра кода команд, выходы которого соединены с третьими входами соответствующих элементов И первой группы и соответствующими входами первого сравниваемого числа первой схемы сравнения всех запоминающих ячеек блока буферной памяти, третья и четвертая группы информационных входов устройства соединены соответственно с группой входов первого сравниваемого числа первой схемы сравнения и группой информационных входов регистра ключа защиты, выход которого соединен с входом второго сравнивания числа первой схемы сравнения, выход сравнения первой схемы сравнения соединен с первым входом элемента И и с вторыми входами элементов И второй группы, выход элемента И является выходом ошибки устройства, первая группа информационных входов устройства соединена с группой информационных входов блока ассоциативной памяти, группой входов первого сравниваемого числа второй схемы сравнения, группой входов первого сравниваемого числа второй и третьей схем сравнения всех запоминающих ячеек блока буферной памяти, третьими входами соответствующих элементов И первой группы и соответствующими входами первого сравниваемого числа первой схемы сравнения всех запоминающих ячеек блока буферной памяти, первый, второй, третий и четвертый выходы дешифратора команд соединены соответственно с первым входом первого элемента ИЛИ, вторым входом второго элемента ИЛИ, с входом обращения блока ассоциативной памяти и выходом останова устройства, первый, второй и третий выходы дешифратора команд соответственно через второй элемент задержки с первым входом второго элемента ИЛИ, через третий элемент задержки с вторым входом второго элемента ИЛИ, с первым входом первого элемента И всех запоминающих ячеек блока буферной памяти, выход третьего элемента задержки соединен с тактовым входом блока ассоциативной памяти и первым входом второго элемента И всех запоминающих ячеек блока буферной памяти, выход первого элемента ИЛИ соединен с вторыми входами элементов И первой и третьей групп, выход второго элемента ИЛИ соединен с тактовым входом второй схемы сравнения, выход равенства которой соединен с входом считывания блока ассоциативной памяти, выход признака которого соединен с тактовым входом первой схемы сравнения всех запоминающих ячеек блока буферной памяти, выход меток времени устройства соединен с первым входом третьего элемента И всех запоминающих ячеек блока буферной памяти, выход переполнения реверсивного счетчика адреса соединен с вторым входом элемента И и является выходом конца чтения устройства, группа информационных выходов регистра адреса команды соединена с группой входов второго сравниваемого числа второй схемы сравнения, в блоке буферной памяти i-й выход дешифратора адреса  соединен с первыми входами элементов И первой и второй групп i-й запоминающей ячейки, выходы элементов И второй группы i-й запоминающей ячейки соединены с i-ми входами элементов ИЛИ группы, выход неравенства первой схемы сравнения i-й запоминающей ячейки соединен с i-м входом элемента И, вторые входы элементов И первой группы каждой запоминающей ячейки соединены с выходом элемента И, группа информационных выходов регистра адреса команды соединена с третьими входами соответствующих элементов И первой группы всех запоминающих ячеек, выходы элементов И первой группы i-й запоминающей ячейки соединены с информационными входами регистра цикла i-й запоминающей ячейки, информационные выходы регистра цикла i-й запоминающей ячейки соединены с входами второго сравниваемого числа первой схемы сравнения i-й запоминающей ячейки, информационные выходы регистра цикла и счетчика циклов i-й запоминающей ячейки соединены с вторыми входами соответствующих элементов И второй группы, выход равенства первой схемы сравнения i-й запоминающей ячейки соединен со счетным входом счетчика циклов i-й запоминающей ячейки, выходы кода адреса конца цикла и начала цикла регистра цикла i-й запоминающей ячейки соединены с входами второго сравниваемого числа соответственно второй и третьей схем сравнения i-й запоминающей ячейки, выходы "Меньше" и "Больше" второй и третьей схем сравнения i-й запоминающей ячейки соединены соответственно с первым и вторым входами четвертого элемента И i-й запоминающей ячейки, выход которого соединен с вторыми входами первого и второго элементов И и первым входом элемента ИЛИ i-й запоминающей ячейки, выходы первого и второго элементов И i-й запоминающей ячейки соединены соответственно с входами установки нуля и единицы триггера i-й запоминающей ячейки, прямой выход которого соединен с вторым входом элемента ИЛИ i-й запоминающей ячейки, выход которого соединен с вторым входом третьего элемента И i-й запоминающей ячейки, выход которого соединен со счетным входом счетчика времени i-й запоминающей ячейки, выходы счетчика времени i-й запоминающей ячейки соединены с вторыми входами соответствующих элементов И второй группы i-й запоминающей ячейки, а в блоке ассоциативной памяти группа информационных входов блока соединена с первыми входами элементов И всех групп и группой входов первого сравниваемого числа всех схем сравнения, тактовый вход блока соединен с тактовыми входами всех схем сравнения, выход K-го счетчика адреса возврата

соединен с первыми входами элементов И первой и второй групп i-й запоминающей ячейки, выходы элементов И второй группы i-й запоминающей ячейки соединены с i-ми входами элементов ИЛИ группы, выход неравенства первой схемы сравнения i-й запоминающей ячейки соединен с i-м входом элемента И, вторые входы элементов И первой группы каждой запоминающей ячейки соединены с выходом элемента И, группа информационных выходов регистра адреса команды соединена с третьими входами соответствующих элементов И первой группы всех запоминающих ячеек, выходы элементов И первой группы i-й запоминающей ячейки соединены с информационными входами регистра цикла i-й запоминающей ячейки, информационные выходы регистра цикла i-й запоминающей ячейки соединены с входами второго сравниваемого числа первой схемы сравнения i-й запоминающей ячейки, информационные выходы регистра цикла и счетчика циклов i-й запоминающей ячейки соединены с вторыми входами соответствующих элементов И второй группы, выход равенства первой схемы сравнения i-й запоминающей ячейки соединен со счетным входом счетчика циклов i-й запоминающей ячейки, выходы кода адреса конца цикла и начала цикла регистра цикла i-й запоминающей ячейки соединены с входами второго сравниваемого числа соответственно второй и третьей схем сравнения i-й запоминающей ячейки, выходы "Меньше" и "Больше" второй и третьей схем сравнения i-й запоминающей ячейки соединены соответственно с первым и вторым входами четвертого элемента И i-й запоминающей ячейки, выход которого соединен с вторыми входами первого и второго элементов И и первым входом элемента ИЛИ i-й запоминающей ячейки, выходы первого и второго элементов И i-й запоминающей ячейки соединены соответственно с входами установки нуля и единицы триггера i-й запоминающей ячейки, прямой выход которого соединен с вторым входом элемента ИЛИ i-й запоминающей ячейки, выход которого соединен с вторым входом третьего элемента И i-й запоминающей ячейки, выход которого соединен со счетным входом счетчика времени i-й запоминающей ячейки, выходы счетчика времени i-й запоминающей ячейки соединены с вторыми входами соответствующих элементов И второй группы i-й запоминающей ячейки, а в блоке ассоциативной памяти группа информационных входов блока соединена с первыми входами элементов И всех групп и группой входов первого сравниваемого числа всех схем сравнения, тактовый вход блока соединен с тактовыми входами всех схем сравнения, выход K-го счетчика адреса возврата  соединен с входом второго сравниваемого числа K-й схемы сравнения, выход элемента ИЛИ-НЕ соединен с первым входом (M + 1)-го элемента И, вход считывания блока соединен с вторым входом (M + 1)-го элемента И, выход которого является выходом признака блока, вход обращения блока соединен с первыми входами первых M элементов И, инверсный выход первого триггера соединен с вторым входом первого элемента И, единичный выход K-го триггера соединен с вторым входом (K + 1)-го элемента И, выход K-го элемента И соединен с единичным входом K-го триггера, вторыми входами элементов И K-й группы и через K-й элемент задержки со счетным входом K-го счетчика адреса возврата, выходы элементов И K-й группы соединены с информационными входами счетчика адреса возврата, отличающееся тем, что выход элемента И блока буферной памяти через первый элемент задержки соединен с суммирующим входом реверсивного счетчика адреса, вход чтения устройства соединен с вычитающим входом реверсивного счетчика адреса, а в блоке ассоциативной памяти выход "Равно" K-й

соединен с входом второго сравниваемого числа K-й схемы сравнения, выход элемента ИЛИ-НЕ соединен с первым входом (M + 1)-го элемента И, вход считывания блока соединен с вторым входом (M + 1)-го элемента И, выход которого является выходом признака блока, вход обращения блока соединен с первыми входами первых M элементов И, инверсный выход первого триггера соединен с вторым входом первого элемента И, единичный выход K-го триггера соединен с вторым входом (K + 1)-го элемента И, выход K-го элемента И соединен с единичным входом K-го триггера, вторыми входами элементов И K-й группы и через K-й элемент задержки со счетным входом K-го счетчика адреса возврата, выходы элементов И K-й группы соединены с информационными входами счетчика адреса возврата, отличающееся тем, что выход элемента И блока буферной памяти через первый элемент задержки соединен с суммирующим входом реверсивного счетчика адреса, вход чтения устройства соединен с вычитающим входом реверсивного счетчика адреса, а в блоке ассоциативной памяти выход "Равно" K-й  схемы сравнения соединен с входом установки нуля K-го триггера и K-входом элемента ИЛИ-НЕ.

схемы сравнения соединен с входом установки нуля K-го триггера и K-входом элемента ИЛИ-НЕ.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для отладки программ | 1985 |

|

SU1348840A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-11-27—Публикация

1991-07-30—Подача