мального внутреннего языка проектируемой ЭВМ, Целью изобретения является расширение функциональных возможностей за счет запоминания команды начала, адреса команды конца, количества повторений цикла и времени выполнения цикла. Устройство содержит блок 1 буферной памяти, блок 2 ассоциативной памяти, регистр 3 клю-, ча защиты, регистр 4 кода команды.

1

Изобретение относится к вычислительной технике, в частности к устройствам регистрации результатов испытаний программ в цифровых системах обработки данных.

Целью изобретения является расширение функциональных возможностей за счет запоминания команды начала, адреса команды начала количества повторений цикла и времени выполне- ния цикла.

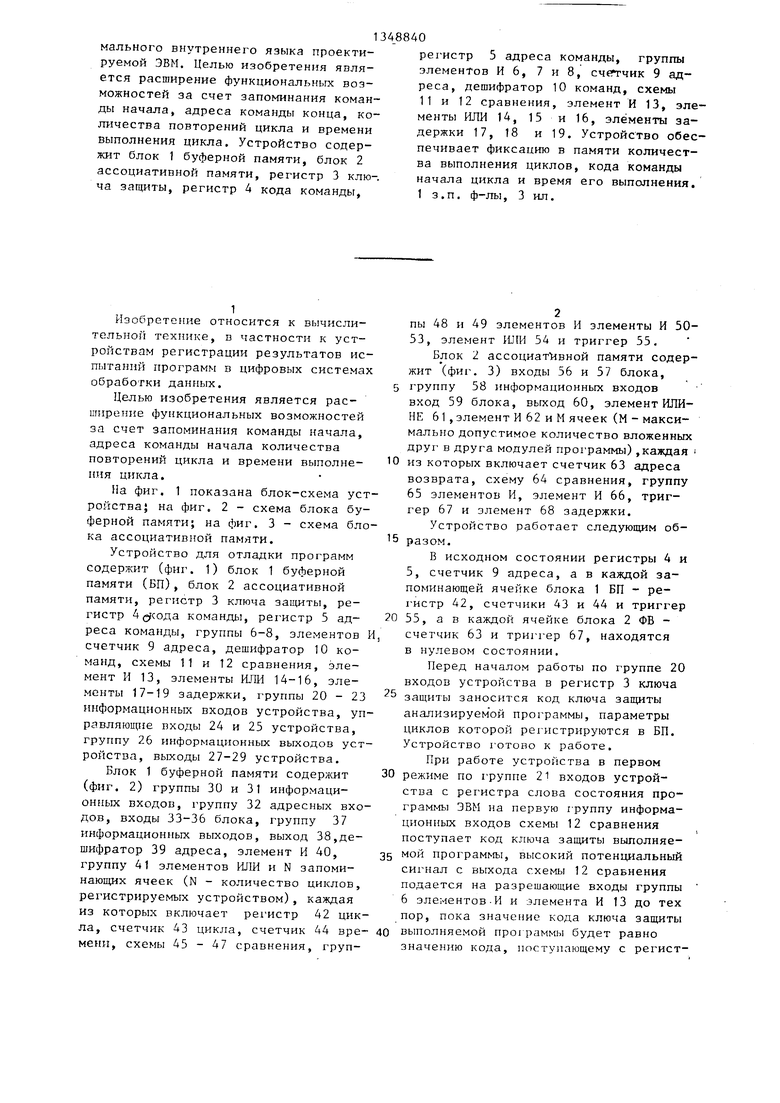

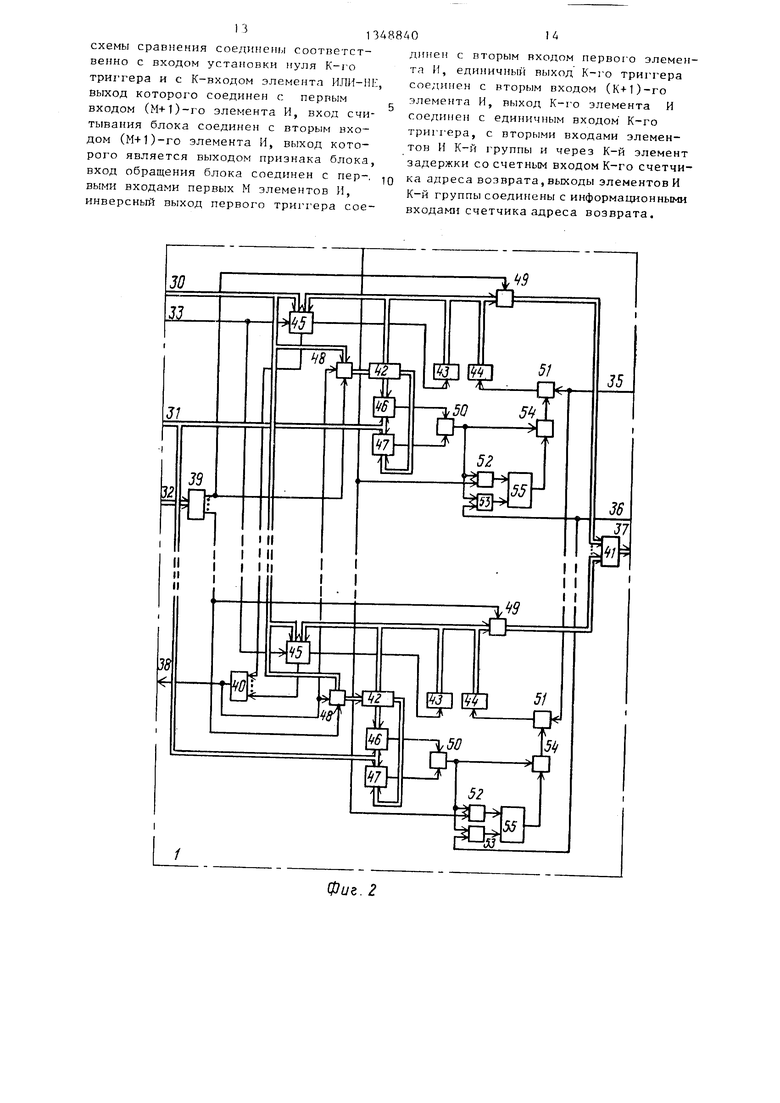

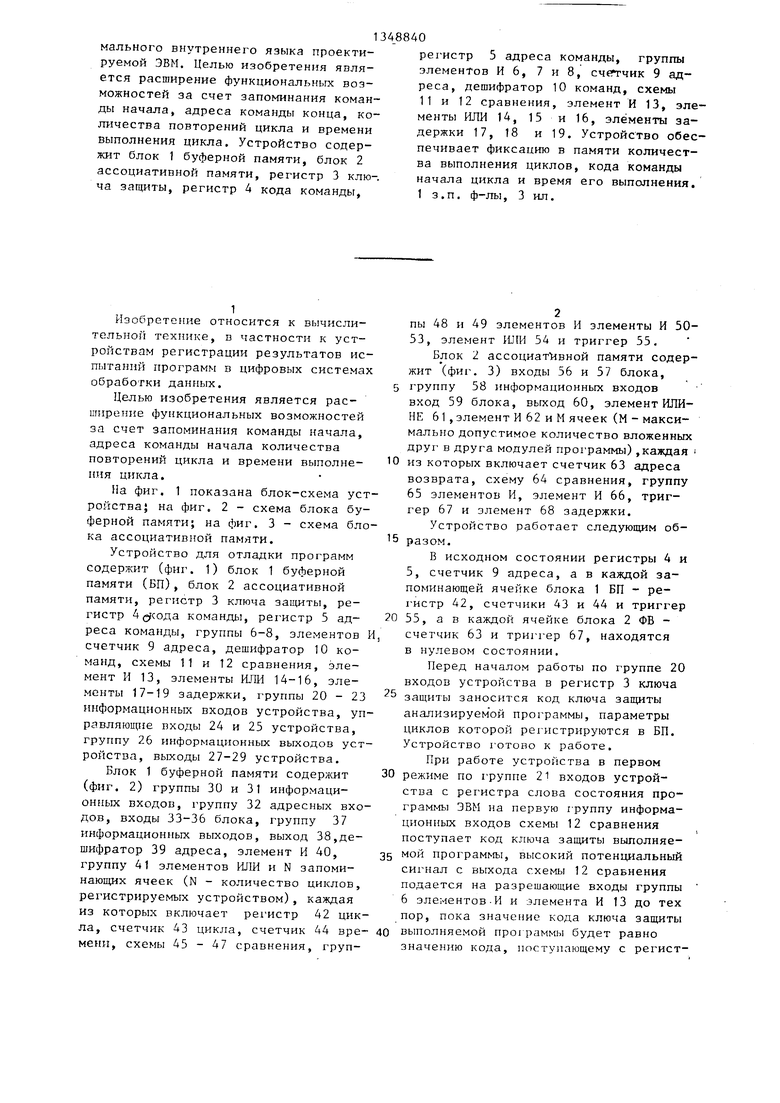

Яа фиг. 1 показана блок-схема устройства; на фиг. 2 - схема блока буферной памяти; на фиг. 3 - схема блока ассоциатив}юй памяти.

Устройство для отладки программ содержит (фиг. 1) блок 1 буферной памяти (БП), блок 2 ассоциативной памяти, регистр 3 ключа защиты, регистр 4gfcoAa команды, регистр 5 ад- реса команды, группы 6-8, элементов счетчик 9 адреса, дешифратор 10 команд, схемы 11 и 12 сравнения, элемент И 13, элементы ИЛИ 14-16, элементы 17-19 задержки, группы 20 - 23 информационных входов устройства, управляющие входы 24 и 25 устройства, группу 26 информационных выходов устройства, выходы 27-29 устройства.

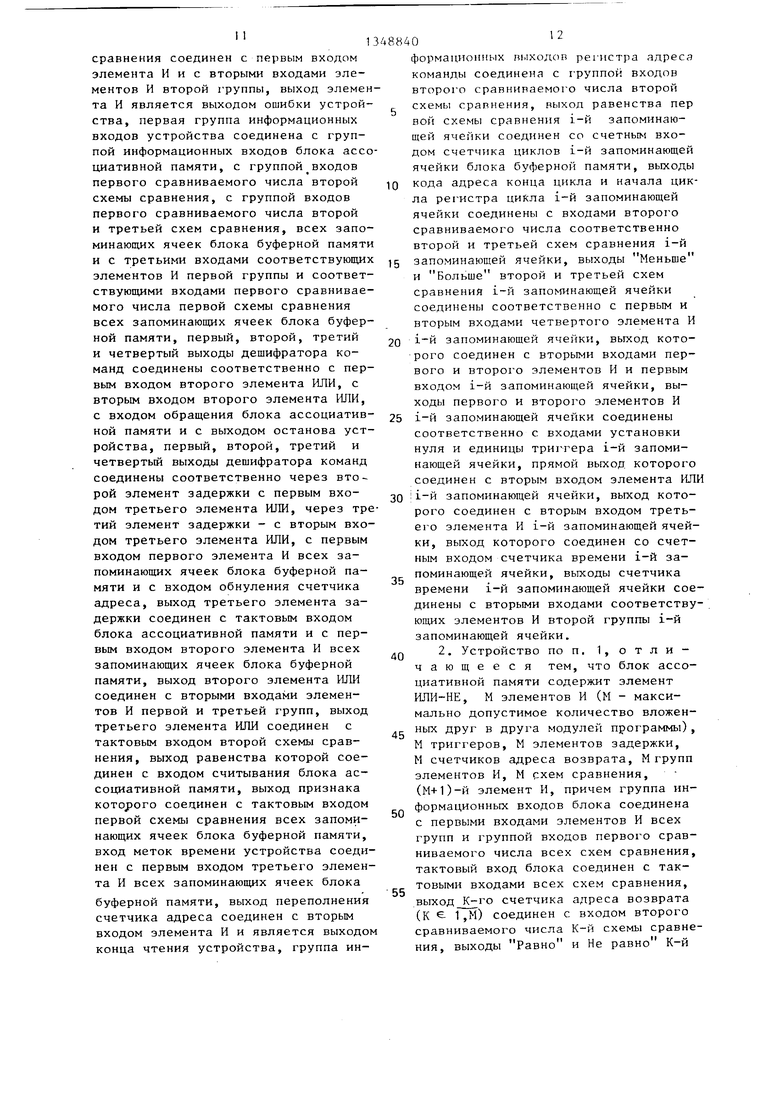

Блок 1 буферной памяти содержит (фиг. 2) группы 30 и 31 информационных входов, группу 32 адресных входов, входы 33-36 блока, группу 37 информационных выходов, выход 38,дешифратор 39 адреса, элемент И 40, группу 41 элементов ШШ и N запоминающих ячеек (N - количество циклов, регистрируемых устройством), каждая из которых включает регистр 42 цикла, счетчик 43 цикла, счетчик 44 вре меня, схемы 45 - 47 сравнения, груп48840

регистр 5 адреса команды, группы элементов И 6, 7 и 8, счегтчик 9 адреса, дешифратор 10 команд, схемы 11 и 12 сравнения, элемент И 13, элементы ИЛИ 14, 15 и 16, элементы задержки 17, 18 и 19. Устройство обеспечивает фиксацию в памяти количества выполнения циклов, кода команды начала цикла и время его выполнения. 1 3.п. ф-лы, 3 ил.

пы 48 и 49 элементов И элементы И 50 53, элемент ШШ 54 и триггер 55,

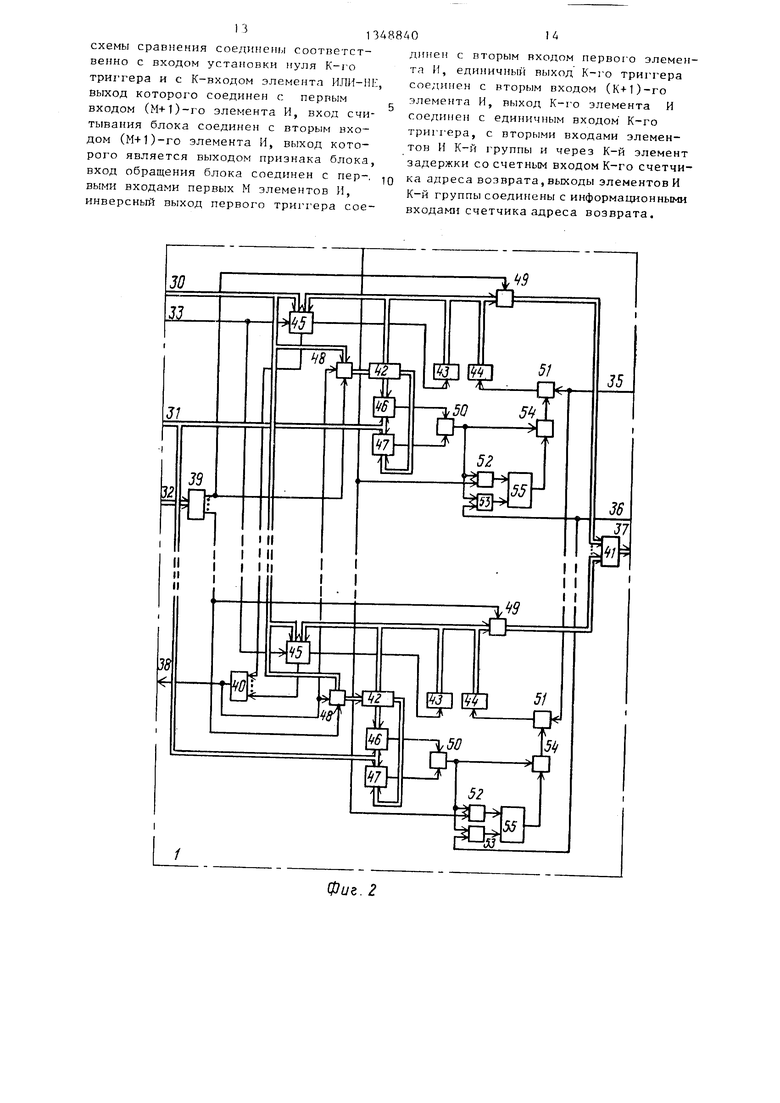

Блок 2 ассоциат Ивной памяти содержит (фиг, 3) входы 56 и 57 блока, группу 58 информационных входов вход 59 блока, выход 60, элемент ИЛИ- НЕ 61 , элемент И 62 и М ячеек (М - максимально допустимое количество вложенных друг в друга модулей программы),каждая из которых включает счетчик 63 адреса возврата, схему 64 сравнения, группу 65 элементов И, элемент И 66, триггер 67 и элемент 68 задержки.

Устройство работает следующим образом.

В исходном состоянии регистры 4 и 5, счетчик 9 адреса, а в каждой запоминающей ячейке блока 1 БП - ре- 1-истр 42, счетчики 43 и 44 и триггер 55, а в каждой ячейке блока 2 ФВ - счетчик 63 и триггер 67, находятся в нулевом состоянии.

Перед началом работы по группе 20 входов устройства в регистр 3 ключа защиты заносится код ключа защиты анализируем ой программы, параметры циклов которой регистрируются в БП. Устройство готово к работе.

При работе устройства в первом режиме по группе 21 входов устройства с регистра слова состояния программы ЭВМ на первую г-руппу информационных входов схемы 12 сравнения поступает код ключа защиты выполняемой программы, высокий потенциальный сигнал с выхода схемы 12 сравнения подается на разрешающие входы группы 6 элементов-И и элемента И 13 до тех пор, пока значение кода ключа защиты выполняемой программы будет равно значению кода, поступающему с регист31348840

pa 3 ключа защиты на вторую группу информационных входов схемы 12 сравнения .

Коды команд анализируемой программы (по г руппе 22 входов устройства поступают коды выполняемых ЭВМ команд) через группу 6 элементов И поступают на первый вход группы 7 элеуправления не является адресом возврата (а в начале работы так и будет) , то на выходе несовпадения схемы 6А сравнения каждой ячейки блока 2 присутствует низкий потендиал (ситуация несовпадения кодов на входах схемы сравнения), а на выходе элемента ИЛН-НР 61 - высокий (разрешаюментов И и группу информационных вхо- Ю ,тий) потенциал, подаваемый на первый

доз дешифратора 10 команд. Адреса команд на группе 23 входов устройства поступают на первый вход группы 8 элементов И, первую группу информационных входов схемы 11 сравнения, группу 58 входов блока 2, соответст- вуюЕцие входы группы 30 информационных входов БП и группу 31 информационных входов БП.

Если очередная команда является командой условной или безусловной передачи управления, то соответственно с первого или второго выхода дешифратора 10 команд выдается импульсный

вход элемента Н 62. Этот сигнал поступает через второй вход 57, элемент И 62, выход 60, вход 33 БП на управляюпцп вход всех схем 45 срав15 нения БП,

В случае, если ни в одном регистр 42 цикла не содержится кода (поступа ет на вторую группу информационных входов соответствующих схем 45 срав20 нения), равного коду, поступающему в данный момент на первую группу информационных входов схем 45 сравнения (состоит из кода команды передачи управления, кода адреса конца цик

сигнал, который через элемент ПЛИ 14 25 д j кода адреса начала цикла), то

поступает на разрешающие входы группы 7 и 8 элементов И, в результате чего код команды фиксируется в регистре 4 кода команды, а адреса этой команды - в регистре 5 адреса команды. Код с регистра 4 поступает на соответствующие входы группы 30 информационных входов БП, а код с регистра 5 - на соответствующие входы группы 30 входов БП и на вторую группу информационных входов схемы 11 сравнения, на выходе которой при отсутствии сигнала на управляющем входе присутствует низкий потенциал. Сигнал, появившийся на первом или втором выходе дешифратора 10,через соответственно элемент 18 задержки или элемент 19 задержки и элемент ИЛ 16 поступает на управляющий вход схемы 1 1 сравнения в тот момент, когда на группе 23 входов устройства появляется код адреса команды, на который в данный момент передано управление. Если код, поступающий на вторую группу информационных входов, больше кода, поступающего на первую группу информационных входов (призна наличия цикла), то по сигналу на управляющем входе схема 11 сравнения выдает импульсный сигнал, признак выявления цикла. При этом, если в блоке 2 не было ранее зафиксировано ни одной передачи управления с возвратом или текущий адрес передачи

управления не является адресом возврата (а в начале работы так и будет) , то на выходе несовпадения схемы 6А сравнения каждой ячейки блока 2 присутствует низкий потендиал (ситуация несовпадения кодов на входах схемы сравнения), а на выходе элемента ИЛН-НР 61 - высокий (разрешаювход элемента Н 62. Этот сигнал поступает через второй вход 57, элемент И 62, выход 60, вход 33 БП на управляюпцп вход всех схем 45 сравнения БП,

В случае, если ни в одном регистре 42 цикла не содержится кода (поступает на вторую группу информационных входов соответствующих схем 45 сравнения), равного коду, поступающему в данный момент на первую группу информационных входов схем 45 сравнения (состоит из кода команды передачи управления, кода адреса конца j кода адреса начала цикла), то

0

5

при поступлении сигнала на управляю- вход все схемы 45 сравнения вырабатывают сигнал на первом выходе (в начале работы так и будет). Эти сигналы поступают на соответствующие входы элемента И 40 БП, на выходе которого тогда формируется сигнал . (сигнал занесения), поступающий на выход 38 БП и второй вход группы 48 элементов И каждой ячейки. Сигнал занесения обеспечивает занесение кода цикла (кода команды передачи управления, кода адреса конца цикла, кода адреса начала цикла) в соответствую- 0 разряды регистра 42 цикла соответствующей ячейки БП, адрес которой определяется разрешающим потенциалом на соответствующем номеру этой ячейки БП выходе дешифратора 39 адреса (в начале работы это первая ячейка).

После занесения кода цикла в регистр 42 соответствующей ячейки БП с второй группы информационных выходов этого регистра на вторую группу информационных входов схемы 47 сравнения данной ячейки поступает код адреса конца цикла, а с третьей группы информационных выходов этого регистра на вторую 1 руг1пу информационных входов схемы 45 сравнения данной ячейки поступает код адреса начала данного цикла. На первые группы информационных входов схем 46 и 47 сравнения каждой ячемки Ы1 с груп5

0

5

пы 31 входов БП поступает код адреса текущей команды программы.

Схема 46 сравнения каждой ячейки БП выдает разрешающий потенциал с выхода, если этот код больше, а схема 47 сравнения каждой ячейки БП - если меньше значений кодов, поступающих на их вторые группы информационных входов. Эти разрешающие потен- циалы обеспечивают формирование разрешающего потенциала на выходе соответствующего элемента И 50, который поступает на вторые входы элементов И 52 и 53 соответствующей ячейки БП и через соответствующий элемент ИЛИ 54 на второй вход соответствующего элемента И 51, разрешая тем самым поступление счетных импульсов на ЭВМ (через упрапляюшпй вход 24 устройства, вход 35 БП и открытый элемент И 51) на счетный вход соответствующего счетчика 44 времени, на котором формируется код, соответствующий суммарному времени реализации данного цикла.

Сиг нал с выхода 38 БП через элемент 17 задержки и элемент ИЛИ 15 поступает на счетный вход счед чика 9 адреса, увеличивая его содержимое на единицу. Код с группы выходов счетчика 9 через группу 32 адресных входов БП поступает на вход дешифратора 39, на соответствующем выходе которого появляется разрешающий потенциал, обеспечивающий запись информации в следующую ячейку БП при возникновении описанной ситуации.

В случае, если в регистре 42 цикла одной из ячеек БП хранится код, равный коду цикла, поступающему в данный момент на первую группу информационных входов схемы 45 сравнения всех ячеек БП, то при поступлении сигнала на управляющий вход с ее второго выхода выдается сигнал, посту- паю1днй на счетный вход соответствующего счетчика 43 цикла и увеличиваю- п;ий его содержимое на единицу (счетчик содержит количество реализаций цикла, уменьшенное на единицу, нулевой код данного счетчика при ненулевом значении кода соответствующего регистра 42 цикла после окончания работы устройства в первом режиме свидетельствует о выделении вырож- / денного, однократно реализуемого цикла).

0

5

В случае, если код (адрес текущей команды), поступающий по группе 31 входов БП на первые группы информационных входов схем 46 и 47 сравнения каждой ячейки, не удовлетворяет описанным условиям выдачи разрешающих потенциалов с выхода этих схем (что соответствует выходу из цикла, зафиксированного в данной ячейке), то запрещающий потенциал с выхода элемента И 50 соответствующей ячейки (при отсутствии разрешающего потенциала на единичном выходе

5 соответствующего триггера 55) запрещает поступление счетных импульсов на вход соответствующего счетчика 44 времени.

В процессе выполнения анализируемой программы возможна передача уп- равления в другую часть программы (модуль) по команде безусловной передачи управления с возвратом. Если такая ситуация возникает в процессе реализации цикла, то время выполнения команд модуля, к которому передается управление, должно учитываться в суммарном времени реализации цикла. Поэтому, если очередная команда анализируемой программы является командой безусловной передачи управления с возвратом, что с третьего выхода дешифратора 10 команд выдается импульсный сигнал, который поступает на взсод 36 БП (работа БП в этом случае описана ниже) и вход 59. При этом блок 2 работает следующим образом.

Сигнал, поступающий с входа 59, через открытый элемент И 66 соответствующей ячейки (первоначально первой) устанавливает соответствующий триггер 67 в единичное состояние и поступает на вторые входы элементов

5 группы 65 данной ячейки (высокий потенциал на единичном выходе триггера 67 данной ячейки открывает элемент И 66 последующей ячейки), Этот сигнал обеспечивает занесение кода

Q адреса команды безусловной передачи управления с возвратом в соответст- счетчик 63 адреса возврата. Этот лее сигнал, пройдя через соответствующий элемент 68 задержки, поg ступает на счетный вход соответствующего счетчика 63 адреса возврата и увеличивает его содержимое на единицу, тем самым в счетчике формируется значение адреса возврата в вы0

5

0

зывающую часть (модуль) программы из вызываемой. Код с группы выходов счетчика 63 адреса возврата каждой ячейки поступает на вторую группу информационных входов соответствующих схем 64 сравнения, на первые группы информационных входов которых поступает значение текущего адреса выполняемой программы с группы 58 информационных входов.

При поступлении сигнала с третьего выхода дещифратора 10 команд на вход 36 БП блок 1 буферной памяти работает следующим образом. Этот сигнал поступает на первый вход элемента И 53 каждой ячейки. На выходе элементов И 53 ячеек БП, имеющих разрешающие потенциалы на втором входе (для ячеек, в которых подсчитывается суммарное время реализации соответствующих им циклов), формируется сигнал установки триггера 55 соответствующих ячеек в единичное состояние, чем обеспечивается наличие разрешающего потенциала на выходе соответствующего элемента ИЛИ 54. В результате обеспечивается подсчет суммарного времени реализации данного цикла несмотря на появление признака окончания цикла после выполнения команды безусловной передачи управления с возвратом. Возврат из вызываемой части программы (модуля) в вызывающую осуществляется по команде безусловно передачи управления, при этом импульсный сигнал с второго выхода дешифратора 10 команд через элемент 19 задержки и вход 56 поступает на управ - ляющие входы схем 64 сравнения. Импульсный сигнал появляется на втором выходе только той схемы 64 сравнения ячейки, для которой сравниваемые в данный момент времени коды равны (т.е. передается управление по адресу, зафиксированному в счетчике 63 адреса возврата данной ячейки). Этим сигналом сбрасывается соответствующий триггер 67. В данньш момент времени (при равенстве кодов) на первом выходе схемы 64 сравнения будет высокий потенциал, а на выходе элемента ИЛИ-НЕ 61 - низкий (запрещающий), который запрещает прохождение через элементы И 62 сигнала вьщеления цикла в блок БП (возврат из одного модуля в другой не будет воспринят как признак цикла).

348840

Сигнал, выработанный с второго выхода дешифратора 10 команд, через элемент 19 задержки поступает также на вход 34 БП, при этом БП работает следующим образом. Этот сигнал поступает на элемент И 52 каждой ячейки.

но сбрасывает триггер 55 только

0

тех ячеек БП, для которых текущий адрес передачи управления находится внутри соответствующих им циклов, т.е. в которых осуществляется подсчет суммарного времени.

После расшифровки команды конца

5 работы анализируемой программы импульсный сигнал с четвертого выхода дешифратора 10 команд сбрасывает содержимое счетчика 9 адреса и по управляющему выходу 27 устройства сигQ нализирует в ЭВМ об окончании работы устройства в первом режиме. В случае, если при работе устройства в первом режиме количество обнаруженных в программе циклов превышает емкость

5 БП, то сигнал переполнения с выхода счетчика 9 адреса через элемент И 13 выдается через управляющий выход 28 устройства в ЭВМ, сигнализируя об аварийной ситуации. При работе устройства во втором режиме по управляющему входу 25 устройства через элемент ИЛИ 15 из ЭВМ на счетный вход счетчика 9 адреса поступают сигналы выдачи, каждый из которых выдается после считывания содержимого очередной ячейки БП с группы 26 информационных выходов устройства. В зависимости от кода, находящегося на счетчике 9 адреса, возбуждается соответствующая выходная шина дешифратора 39 адреса БП, соединенная с разрешающим входом группы 49 элементов И соответствующей ячейки. Этим обеспечивается поочередная (от 1 до N) передача содержимого регистра 42, счетчика 43, счетчика 44 времени очередной ячейки БП через группу 41 элементов ИЛИ на группу 37 информационных выходов БП и далее на группу 26 информационных выходов устройства.

Сигнал выдачи поступает на счетный вход счетчика 9 адреса до тех пор, пока сигнал его переполнения не будет выдан на управляющий выход 29 устройства, сигнализируя об окончании работы устройства во втором режиме.

5

0

5

0

Формула изобретени

1. Устройство для отладки программ, содержащее блок буферной памяти, регистр адреса команды, счетчик адреса, первую группу элементов И, первый элемент ИЛИ и первый элемент задержки, блок буферной памяти содержит дешифратор адреса, элемент И, группу элементов ИЛИ и N запоминающих ячеек, где N - максимальное количество циклов исследуемой программы, а каждая запоминающая ячейка содержит первую схему сравнения, регистр цикла, счетчик цикла, первую и вторую группы элементов И, причем первая группа информационных входов устройства соединена с первыми входами элементов И первой группы,выходы которых соединены с группой информационных входов регистра адреса команды, группа выходов регистра адреса команды соединена с соответствующими входами первого сравниваемого числа первой схемы сравнения каждой запоминающей ячейки блока буферной памяти, выходы элементов ИЛИ группы блока буферной памяти являются группой информационных выходов устройства, выход элемента И блока буферной памяти через первьй элемент задержки соединен с первым входом первого элемента ИЛИ, выход которого соединен со счетным входом счетчика адреса, группа информационных выходов счетчика адреса соединена с группой входов дешифратора адреса блока буферной памяти, вход чтения устройства соединен с вторым входом первого элемента ЯЛИ, i-й выход дешифра- ,тора адреса блока буферной памяти (1 1,п) соединен с первыми входами элементов И первой и второй групп i-й запоминающей ячейки блока буферной памяти, выходы элементов И второй группы i-й запоминающей ячейки блока буферной памяти соединены с i-ми входами элементов ИЛИ группы блока буферной памяти, выход неравенства первой схемы сравнения i-й запоминающей ячейки блока буферной памяти соединен с i-м входом элемента И блока буферной памяти, вторые входы элементов И первой группы каждой запоминающей яче11ки блока буферной памяти соединены с выходом элемента И блока бу1)ерной памяти, г руппа информационных выходов регистра

48840

адреса команд соединена с третьими входами соответствующих элементов И первой группы всех запоминающих яче- г ек блока буферной памяти, выходы элементов И первой группы i-й запоминаю- щей ячейки соединены с информационными входами регистра цикла i-й запоминающей ячейки, информационные

10 выходы регистра цикла i-й запоминающей ячейки соединены с входами второго сравниваемого числа первой схемы сравнения i-й запоминающей ячейки,информационные выходы регистра цикла и

15 счетчика циклов i-й запоминающей ячейки соединены с вторыми входами соответствующих элементов И второй группы, отличающееся тем, что, с целью расширения функциональ2Q ных возможностей за счет запоминания команды начала, адреса команды начала, адреса команды конца, количества повторений цикла и времени выполнения цикла, в устройство введены ре25 гистр ключа защиты программы, регистр кода команды, первая и вторая схемы сравнения, вторая и третья группы элементов И, второй и третий элементы ИЛИ, второй и третий элементы за3Q держки, дешифратор команд, элемент И и блок ассоциативной памяти, причем в каждую запоминаюп1ую ячейку блока буферной памяти введен счетчик времени, вторая и третья схемы сравнения, четыре элемента И, элемент ИЛИ и триггер, причем вторая группа информационных входов устройства соединена с первыми входами элементов И второй группы, выходы которых соеди.„ нены с первыми входами элементов И третьей группы и с входами дешифратора команд, выходы элементов И третьей группы соединены с информационными входами регистра кода команд,вы- . ходы которого соединены с третьими входами соответствующих элементов И первой группы и соответствующими входами первого сравниваемого числа первой схемы сравнения всех запоминающих ячеек блока буферной памяти, третья и четвертая группы информационных входов устройства соединены cd- ответственно с х руппой входов первого сравниваемого числа Г1ервой схемы сравнения и группой информационных входов регистра ключа защиты, выход которого соединен с входом второго сравниваемого числа первой схемы сравнения, выход сравнения первой схемы

35

50

1

сравнения соединен с первым входом элемента И и с вторыми входами элементов И второй группы, выход элемента И является выходом ошибки устройства, первая группа информационных входов устройства соединена с группой информационных входов блока ассоциативной памяти, с группой входов первого сравниваемого числа второй схемы сравнения, с группой входов первого сравниваемого числа второй и третьей схем сравнения, всех запоминающих ячеек блока буферной памяти и с третьими входами соответствующих элементов И первой группы и соответствующими входами первого сравниваемого числа первой схемы сравнения всех запоминающих ячеек блока буферной памяти, первый, второй, третий и четвертый выходы дешифратора команд соединены соответственно с первым входом второго элемента ИЛИ, с вторым входом второго элемента ИЛИ, с входом обращения блока ассоциативной памяти и с выходом останова устройства, первый, второй, третий и четвертый выходы дешифратора команд соединены соответственно через второй элемент задержки с первым входом третьего элемента ИЛИ, через третий элемент задержки - с вторым входом третьего элемента ИЛИ, с первым входом первого элемента И всех запоминающих ячеек блока буферной памяти и с входом обнуления счетчика адреса, выход третьего элемента задержки соединен с тактовым входом блока ассоциативной памяти и с первым входом второго элемента И всех запоминающих ячеек блока буферной памяти, выход второго элемента ИЛИ соединен с вторыми входами элементов И первой и третьей групп, выход третьего элемента ИЛИ соединен с тактовым входом второй схемы сравнения, выход равенства которой соединен с входом считывания блока ассоциативной памяти, выход признака которого соединен с тактовым входом первой схемы сравнения всех запоминающих ячеек блока буферной памяти, вход меток времени устройства соединен с первым входом третьего элемента И всех запоминающих ячеек блока буферной памяти, выход переполнения счетчика адреса соединен с вторым входом элемента И и является выходом конца чтения устройства, группа ин8840 2

формационных выходсш регистра адреса команды соединена с группой входов второго сравнипаемого числа второй схемы сравнения, выход равенства пер вой схемы сравнения i-й запоминающей ячейки соединен со счетным входом счетчика циклов i-й запоминающей ячейки блока буферной памяти, выходы

0 кода адреса конца цикла и начала цикла регистра циЛла i-й запоминающей ячейки соединены с входами второго сравниваемого числа соответственно второй и третьей схем сравнения i-й

15 запоминающей ячейки, выходы Меньше и Больше второй и третьей схем сравнения i-й запоминающей ячейки соединены соответственно с первым и вторым входами четвертого элемента И

20 i-й запоминающей ячейки, выход которого соединен с вторыми входами первого и второго элементов И и первым входом i-й запоминающей ячейки, выходы первого и второго элементов И

25 i-й запоминающей ячейки соединены соответственно с входами установки нуля и единицы триггера i-й запоминающей ячейки, прямой выход которого соединен с вторым входом элемента ИЛИ

30 запоминающей ячейки, выход которого соединен с вторым входом третьего элемента И i-й запоминающей ячейки, выход которого соединен со счетным входом счетчика времени i-й запоминающей ячейки, выходы счетчика времени i-й запоминающей ячейки соединены с вторыми входами соответствующих элементов И второй группы i-й запоминающей ячейки.

Q 2. Устройство по п. 1, отличающееся тем, что блок ассоциативной памяти содержит элемент ИЛИ-НЕ, М элементов И (М - максимально допустимое количество вложен.g ньгх друг в друга модулей программы) , М триггеров, М элементов задержки, М счетчиков адреса возврата, Мгрупп элементов И, М схем сравнения, (М+1)-й элемент И, причем группа информационных входов блока соединена с первыми входами элементов И всех групп и группой входов первого сравниваемого числа всех схем сравнения, тактовый вход блока соединен с тактовыми входами всех схем сравнения.

50

55

выход К-го счетчика адреса возврата (К Г/Й) соединен с входом второго сравниваемого числа К-й схемы сравнения, выходы Равно и Не равно К-й

3134

схемы сравнения соединены соответственно с входом установки нуля К-го трИ1тера и с К-входом элемента ИЛИ-НЕ, выход которого соединен с первым входом (М+1)-го элемента И, вход считывания блока соединен с вторым входом (М+1)-го элемента И, выход которого является выходом признака блока, вход обращения блока соединен с пер-, выми входами первых М элементов И, инверсный выход первого триггера сое

М

0

динен с вторым входом первого элемента И, единичный выход K-i o триггера соединен с вторым входом (K-t-l)-ro элемента И, выход К-г-о элемента И соединен с единичным входом К-го триггера, с вторыми входами элементов И К-й группы и через К-й элемент задержки со счетным входом К-го счетчика адреса воз врата, выходы элементов И Кй группы соединены с информационными входами счетчика адреса возврата.

Фиг. 2

56

S6 гО

фие. 3

Составитель И.Сигалов Редактор Е.Копча Техред А.Кравчук Корректор А.Обручар

Заказ 4803/49 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ | 1991 |

|

RU2049349C1 |

| Устройство для определения частот обращения к программам | 1986 |

|

SU1387001A1 |

| Устройство для определения частот обращения к программам | 1985 |

|

SU1357963A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Устройство для измерения частот появления групп команд | 1986 |

|

SU1405062A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Устройство для сопряжения управляющего вычислительного комплекса с внешними устройствами | 1985 |

|

SU1262514A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для отладки программ | 1981 |

|

SU980096A1 |

| G | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для испытания материалов на абразивный износ | 1985 |

|

SU1295294A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (ЗА) УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ | |||

Авторы

Даты

1987-10-30—Публикация

1985-08-19—Подача