Изобретение относится к области вычислительной техники и микроэлектроники и может быть использовано для построения средств аппаратурного контроля и цифровых устройств, работающих в системе остаточных классов.

Известно устройство для вычисления суммы произведений, содержащее накапливающий сумматор, регистры множимых и множителей, три группы элементов И, группу элементов ИЛИ, две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, дешифратор, три комбинационных сумматора и два элемента задержки на один такт [1]

Недостатком устройства для вычисления суммы произведений является высокая конструктивная сложность при выполнении операции сложения произведений по модулю три.

Наиболее близким по конструкции техническим решением к предлагаемому является сумматор по модулю три, содержащий мажоритарный элемент, два элемента ИЛИ, два элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, четыре входа и два выхода [2]

Недостатком известного сумматора по модулю три являются ограниченные функциональные возможности, поскольку он не реализует операцию сложения произведений по модулю три.

Вычислительное устройство по модулю три содержит мажоритарный элемент с порогом четыре, восемь элементов И и два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Выход каждого из элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с соответствующим выходом устройства, а первый вход соединен с выходом мажоритарного элемента. Входы мажоритарного элемента с первого по четвертый соединены, соответственно, с входами первого и второго разрядов первого операнда устройства и с входами первого и второго разрядов второго операнда устройства. Выходы элементов И с первого по четвертый соединены, соответственно, с входами со второго по пятый первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы элементов И с пятого по восьмой соединены, соответственно, с входами со второго по пятый второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Входы мажоритарного элемента с пятого по восьмой соединены, соответственно, с входами первого и второго разрядов третьего операнда устройства и с входами первого и второго разрядов четвертого операнда устройства. Вход первого разряда первого операнда устройства соединен с первыми входами первого и седьмого элементов И. Вход первого разряда второго операнда устройства соединен со вторым входом первого элемента И и с первым входом восьмого элемента И. Вход первого разряда третьего операнда устройства соединен с первыми входами второго и пятого элементов И. Вход первого разряда четвертого операнда устройства соединен со вторым входом второго элемента И и с первым входом шестого элемента И. Вход второго разряда первого операнда устройства соединен с первым входом третьего элемента И и со вторым входом восьмого элемента И. Вход второго разряда второго операнда устройства соединен со вторыми входами третьего и седьмого элементов И. Вход второго разряда третьего операнда устройства соединен с первым входом четвертого элемента И и со вторым входом шестого элемента И. Вход второго разряда четвертого операнда устройства соединен со вторыми входами четвертого и пятого элементов И.

На чертеже представлена схема вычислительного устройства по модулю три.

Устройство содержит восемь элементов И 1.8, мажоритарный элемент с порогом четыре 9, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 и 11, входы младших разрядов 12, 13, 14 и 15, соответственно, первого, второго, третьего и четвертого операндов, выходы младшего 20 и старшего 21 разрядов результата.

Вычислительное устройство по модулю три работает следующим образом.

На входы 12 и 16 устройства поступают соответственно младший a1 и старший a2 разряды первого операнда A 2a2+а1, на входы 13 и 17 устройства поступают, соответственно, младший b1 и старший b2 разряды второго операнда B 2b2+b1, на входы 14 и 18 устройства поступают, соответственно, младший c1 и старший c2 разряды третьего операнда C 2c2+c1, на входы 15 и 19 устройства поступают, соответственно, младший d1 и старший d2 разряды четвертого операнда D 2d2+d1, где a1, b1, c1, d1, a2, b2, c2, d2 ∈0, 1} и A, B, C, D e0, 1, 2}

На выходах 20 и 21 формируется двухразрядный двоичный код результата S 2s2+s1 операции сложения произведений A•B и C•D по модулю три, где s1, s2 e 0, 1} и S e0, 1, 2} На выходе 20 реализуется младший разряд s1, а на выходе 21 старший разряд s2 результата S A•B + C•D (mod 3).

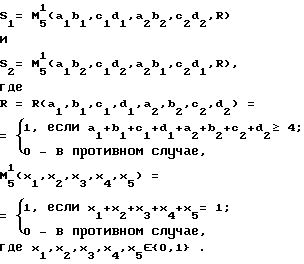

Работа вычислительного устройства по модулю три описывается следующими соотношениями:

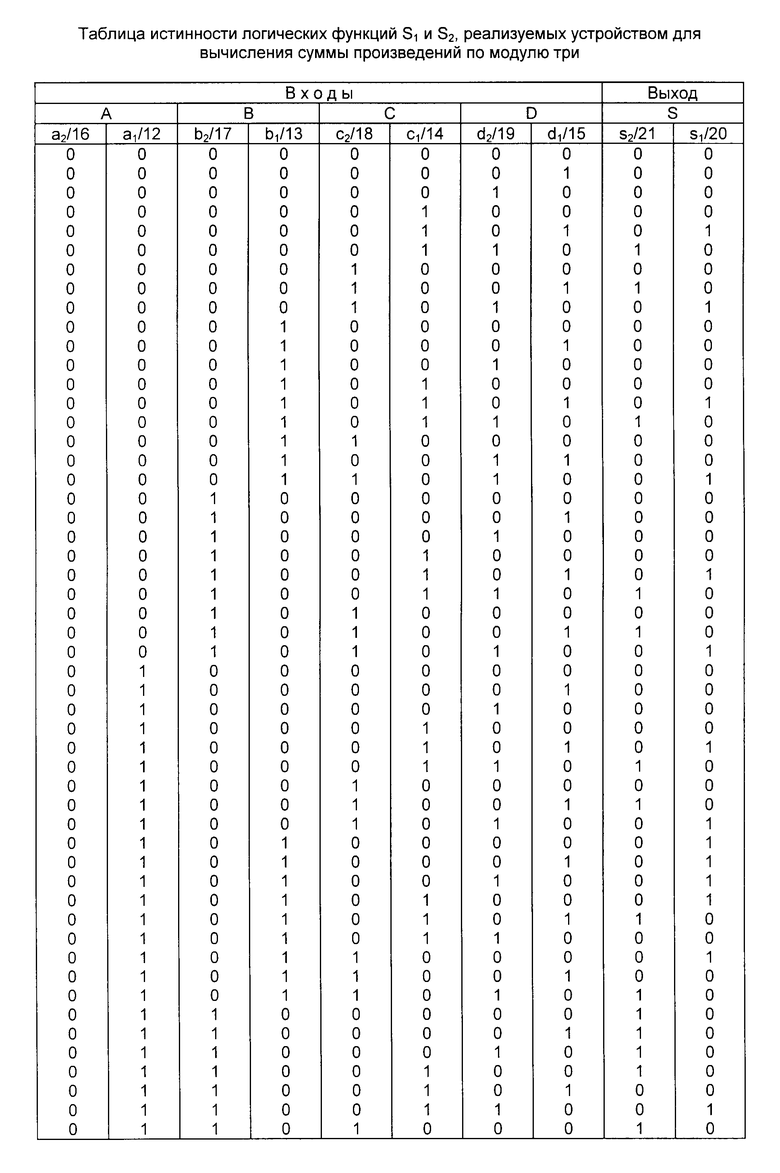

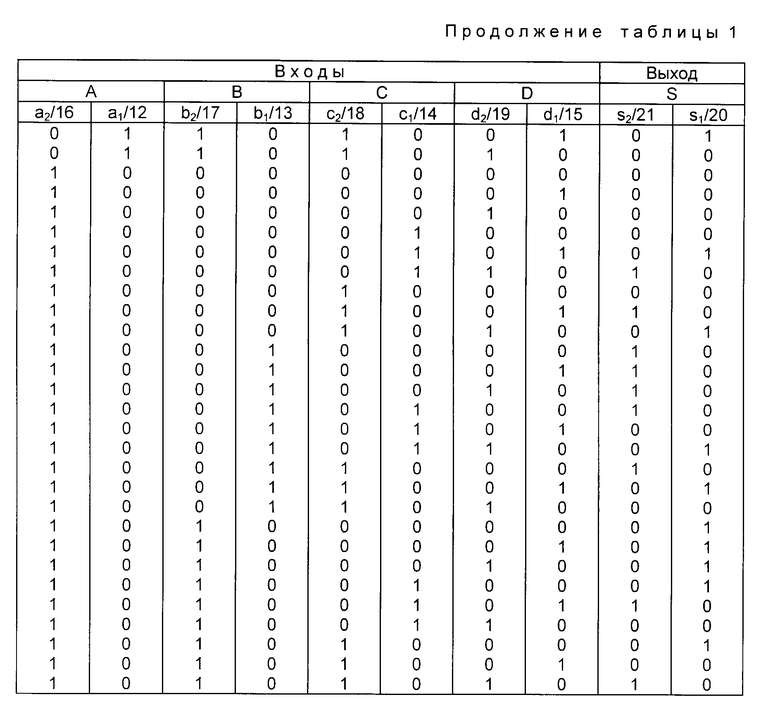

В таблице приведены значения реализуемых устройством функций s1, s2, зависящих от переменных a1, b1, c1, d1, a2, b2, c2, d2.

Достоинствами вычислительного устройства по модулю три являются широкие функциональные возможности, а также простая конструкция и высокое быстродействие. Так, его сложность по числу входов логических элементов равна 34, а быстродействие, определяемое глубиной схемы, составляет 2τ где t - задержка на вентиль.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2021630C1 |

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 1992 |

|

RU2018931C1 |

| Сумматор по модулю пять | 1991 |

|

SU1803911A1 |

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 1992 |

|

RU2012038C1 |

| Сумматор по модулю три | 1991 |

|

SU1830528A1 |

| Сумматор по модулю три | 1991 |

|

SU1800453A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ | 1992 |

|

RU2047894C1 |

| Сумматор по модулю три | 1991 |

|

SU1798777A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018927C1 |

Использование: для построения средств аппаратурного контроля и цифровых устройств, работающих в системе остаточных классов. Устройство содержит восемь элементов И, мажоритарный элемент с порогом четыре, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы старшего и младшего разрядов операнда А, входы старшего и младшего разрядов операнда В, входы старшего и младшего разрядов операнда С, входы старшего и младшего разрядов операнда D, выходы старшего и младшего разрядов результата S. Сложность устройства по числу входов логических элементов равна 34, а быстродействие, определяемое глубиной схемы, составляет 2τ , где τ - задержка на вентиль. 1 табл., 1 ил.

Вычислительное устройство по модулю три, содержащее мажоритарный элемент и два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход каждого из которых соединен с соответствующим выходом устройства, а первый вход соединен с выходом мажоритарного элемента, входы мажоритарного элемента с первого по четвертый соединены соответственно с входами первого и второго разрядов первого операнда устройства и с входами первого и второго разрядов второго операнда устройства, отличающееся тем, что содержит восемь элементов И, выходы с первого по четвертый которых соединены соответственно с входами с второго по пятый первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы элементов И с пятого по восьмой соединены соответственно с входами с второго по пятый второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы мажоритарного элемента с пятого по восьмой соединены соответственно с входами первого и второго разрядов третьего операнда устройства и с входами первого и второго разрядов четвертого операнда устройства, вход первого разряда первого операнда устройства соединен с первыми входами первого и седьмого элементов И, вход первого разряда второго операнда устройства соединен с вторым входом первого элемента И и с первым входом восьмого элемента И, вход первого разряда третьего операнда устройства соединен с первыми входами второго и пятого элементов И, вход первого разряда четвертого операнда устройства соединен с вторым входом второго элемента И и с первым входом шестого элемента И, вход второго разряда первого операнда устройства соединен с первым входом третьего элемента И и с вторым входом восьмого элемента И, вход второго разряда второго операнда устройства соединен с вторыми входами третьего и седьмого элементов И, вход второго разряда третьего операнда устройства соединен с первым входом четвертого элемента И и с вторым входом шестого элемента И, вход второго разряда четвертого операнда устройства соединен с вторыми входами четвертого и пятого элементов И.

| Устройство для вычисления суммы произведений | 1985 |

|

SU1269125A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сумматор по модулю три | 1990 |

|

SU1751747A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1997-09-20—Публикация

1992-09-14—Подача