Изобретение относится к вычислительной технике и автоматике и может быть использовано для построения систем передачи и переработки дискретной информации.

Известен сумматор по модулю пять, содержащий пятнадцать элементов И, восемь элементом ИЛИ, один элемент И-НЕ, три элемента ИЛИ-НЕ, один элемент ЗАПРЕТ, шесть входов и три выхода [1] .

Недостатком сумматора по модулю пять является низкое быстродействие, определяемое глубиной схемы и равное 5 τ , где τ - задержка на вентиль.

Наиболее близким по конструкции и функциональным возможностям к предлагаемому является сумматор по модулю пять, содержащий восемь элементов И, шесть элементов ИЛИ, три элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, три элемента ЗАПРЕТ, шесть входов и три выхода [2] .

Недостатком известного сумматора по модулю пять является низкое быстродействие, которое равно 5 τ .

Сумматор по модулю пять содержит три элемента ЗАПРЕТА, пять элементов И, элемент ИЛИ, мажоритарный элемент с порогом три и три элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА. Вход первого разряда первого слагаемого соединен с первым входом первого элемента И, первым входом первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, первыми входами запрета первого и второго элементов ЗАПРЕТ, первыми входами третьего и четвертого элементов И и первым входом мажоритарного элемента. Вход первого разряда второго слагаемого соединен с вторым входом первого элемента И, вторым входом первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, вторым входом запрета первого элемента ЗАПРЕТ, первым входом запрета третьего элемента ЗАПРЕТ, первым входом пятого элемента И и вторыми входами четвертого элемента И и мажоритарного элемента. Вход второго разряда первого слагаемого соединен с первым входом второго элемента И, первым входом второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, первым прямым входом первого элемента ЗАПРЕТ, вторым входом запрета второго элемента ЗАПРЕТ и третьими входами четвертого элемента И и мажоритарного элемента. Вход второго разряда второго слагаемого соединен с вторым входом второго элемента И, вторым входом второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, вторым прямым входом первого элемента ЗАПРЕТ, вторым входом запрета третьего элемента ЗАПРЕТ и с четвертыми входами четвертого элемента И и мажоритарного элемента. Вход третьего разряда первого слагаемого соединен с первым прямым входом третьего элемента ЗАПРЕТ, вторым входом пятого элемента И и первым входом элемента ИЛИ. Вход третьего разряда второго слагаемого соединен с первым прямым входом второго элемента ЗАПРЕТ, вторым входом третьего элемента И и вторым входом элемента ИЛИ. Выход элемента ИЛИ соединен с третьими входами первого и второго элементов СЛОЖЕНИЕ ПО МОДУЛЮ ДВА. Выходы первого, второго и третьего элементов ЗАПРЕТ соединены соответственно с четвертым, пятым и шестым входами первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, седьмой вход которого соединен с выходом второго элемента И и первым входом третьего элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА. Второй и третий входы третьего элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединены соответственно с выходами второго и третьего элементов ЗАПРЕТ, а четвертый вход соединен с выходом мажоритарного элемента. Четвертый и пятый входы второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединены соответственно с выходами второго и третьего элементов ЗАПРЕТ, а шестой, седьмой, восьмой и девятый входы соединены соответственно с выходами первого, третьего, четвертого и пятого элементов И. Выходы первого, второго и третьего элементов СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединены соответственно с первым, вторым и третьим разрядными выходами сумматора.

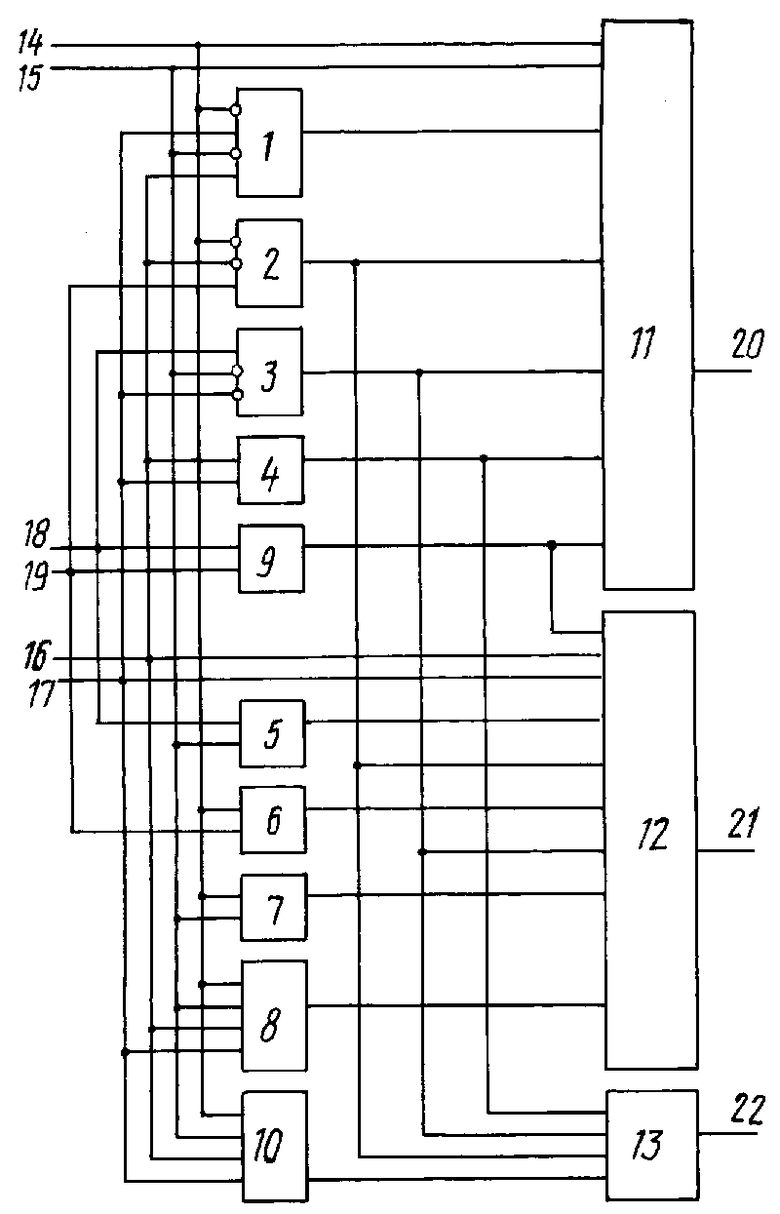

На чертеже представлена схема сумматора по модулю пять.

Сумматор по модулю пять содержит три элемента ЗАПРЕТ 1,2 и 3, пять элементов И 4. . . 8, элемент ИЛИ 9, мажоритарный элемент 10 с порогом три, три элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА 11, 12 и 13, шесть входов 14. . . 19 и три выхода 20, 21 и 22.

Сумматор работает следующим образом.

Суммируемые операнды X и Y задаются трехразрядными двоичными кодами X = x3x2x1, У = y3y2y1, где x1 и y1 - первые (младшие) разряды операндов; x2, y2 - вторые (средние) разряды операндов; x3, y3 - третьи (старшие) разряды операндов, т. е. X = x1 + +2x2 + 4x3 и Y = y1 +2y2 + 4y3.

В соответствии с выбранным модулем Р = 5 каждый операнд может принимать значения 0(000), 1(001), 2(010), 3(011) и 4(100). Результатом работы сумматора по модулю пять является операнд Z, заданный трехразрядным двоичным кодом Z = z3z2z1, где Z= z1 + 2z2 + 4z3.

На входы 14,15 подаются значения младших разрядов x1, y1 операндов X и Y соответственно на входы 16,17 - значения средних разрядов x2, y2операндов X и Y соответственно на входы 18, 19 - значения старших разрядов x3, y3 операндов X и Y соответственно на выходе 20 реализуется младший разряд z1, на выходе 21 - средний разряд z2, а на выходе 22 - старший разряд z3 операнда Z, где Z = X + Y (mod5).

Логические функции z1, z2 и z3 реализуются сумматором согласно следующим аналогическим выражениям:

z1= x1 ⊕ y1 ⊕  x

x y2 ⊕

y2 ⊕  y3 ⊕ x

y3 ⊕ x ⊕ x2y2 ⊕ (x3∨y3);

⊕ x2y2 ⊕ (x3∨y3);

z2= (x3∨y3) ⊕ x2 ⊕ y2 ⊕ x3y1 ⊕  y3 ⊕ x1y3 ⊕ x

y3 ⊕ x1y3 ⊕ x ⊕

⊕

⊕ x1y1 ⊕ x1x2y1y2;

z3= x2y2 ⊕ x ⊕

⊕  y3 ⊕ M

y3 ⊕ M

Достоинством сумматора по модулю пять является высокое быстродействие. Так, его быстродействие, определяемое глубиной схемы, равно 2τ , в то время как быстродействие устройства-прототипа равно 5τ . Сложность сумматора по числу входов логических элементов не намного превосходит сложность устройства-прототипа и равна 48, тогда как сложность устройства-прототипа равна 42.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 1992 |

|

RU2018931C1 |

| ДВОИЧНЫЙ СУММАТОР | 2013 |

|

RU2533078C1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1837280A1 |

| РЕЛЯТОРНЫЙ ПРОЦЕССОР ДЛЯ АДРЕСНО-РАНГОВОЙ ИДЕНТИФИКАЦИИ, СЕЛЕКЦИИ И РАНЖИРОВАНИЯ ТРЕХ АНАЛОГОВЫХ СИГНАЛОВ | 1999 |

|

RU2149450C1 |

| Устройство для подсчета числа единиц | 1988 |

|

SU1730621A1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2028660C1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1797110A1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2018924C1 |

| Сумматор по модулю пять | 1991 |

|

SU1803911A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ АРИФМЕТИЧЕСКИХ ВЫЧИСЛЕНИЙ ПО ЗАДАННОМУ МОДУЛЮ | 2011 |

|

RU2477513C1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано для построения систем передачи и переработки дискретной информации. Сумматор по модулю пять содержит три элемента ЗАПРЕТ, пять элементов И, элемент ИЛИ, мажоритарный элемент с порогом три, три элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, шесть входов и три выхода. Сложность сумматора по числу входов логических элементов равна 48, а быстродействие, определяемое глубиной схемы, равно 2τ , где t - задержка на вентиль. На выходы поступают двоичные переменные X1, Y1, X2, Y2, X3, Y3 , представляющие собой первые, вторые и третьи разряды суммируемых операндов X и Y соответственно, на выходах реализуются логические функции Z1, Z2, Z3 , где Z1 - первый разряд, Z2 - второй разряд, Z3 - третий разряд операнда Z и Z = X + Y (mod 5). 1 ил.

СУММАТОР ПО МОДУЛЮ ПЯТЬ, содержащий три элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, три элемента ЗАПРЕТ, элемент ИЛИ и пять элементов И, первые входы первого и второго из которых соединены соответственно с входами первого и второго разрядов первого слагаемого, а вторые входы соединены соответственно с входами первого и второго разрядов второго слагаемого, отличающийся тем, что он содержит мажоритарный элемент с порогом три, причем вход первого разряда первого слагаемого соединен с первым входом первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, первыми входами запрета первого и второго элементов ЗАПРЕТ, первыми входами третьего и четвертого элементов И и первым входом мажоритарного элемента, вход первого разряда второго слагаемого соединен с вторым входом первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, вторым входом запрета первого элемента ЗАПРЕТ, первым входом запрета третьего элемента ЗАПРЕТ, первым входом пятого элемента И и вторыми входами четвертого элемента И и мажоритарного элемента, вход второго разряда первого слагаемого соединен с первым входом второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, первым прямым входом первого элемента ЗАПРЕТ, вторым входом запрета второго элемента ЗАПРЕТ и третьими входами четвертого элемента И и мажоритарного элемента, вход второго рязряда второго слагаемого соединен с вторым входом второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, вторым прямым входом первого элемента ЗАПРЕТ, вторым входом запрета третьего элемента ЗАПРЕТ и четвертыми входами четвертого элемента И и мажоритарного элемента, вход третьего разряда первого слагаемого соединен с первым прямым входом третьего элемента ЗАПРЕТ, вторым входом пятого элемента И и первым входом элемента ИЛИ, вход третьего разряда второго слагаемого соединен с первым прямым входом второго элемента ЗАПРЕТ, вторым входом третьего элемента И и вторым входом элемента ИЛИ, выход которого соединен с третьими входами первого и второго элементов СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, выходы первого, второго и третьего элементов ЗАПРЕТ соединены соответственно с четвертым, пятым и шестым входами первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, седьмой вход которого соединен с выходом второго элемента И и первым входом третьего элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, второй и третий входы которого соединены соответственно с выходами второго и третьего элементов ЗАПРЕТ, а четвертый вход соединен с выходом мажоритарного элемента, четвертый и пятый входы второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединены соответственно с выходами второго и третьего элементов ЗАПРЕТ, а шестой, седьмой, восьмой и девятый входы соединены соответственно с выходами первого, третьего, четвертого и пятого элементов И, выходы первого, второго и третьего элементов СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединены соответственно с первым, вторым и третьим разрядными выходами сумматора.

Авторы

Даты

1994-04-30—Публикация

1992-03-27—Подача