Изобретение относится к области аналоговой вычислительной техники и автоматики и может быть использовано в устройствах допускового контроля, для ранговой обработки аналоговых сигналов по признаку их принадлежности и не принадлежности к медианным сигналам, для идентификации и селекции субмедианных, медианных и супрамедианных значений информационного сигнала и др.

Известны реляторные коммутационно-логические преобразователи и устройства (см., например, а.с. СССР 1693614, кл. G 06 G 7/25; Л.И.Волгин. Синтез устройств для обработки и преобразования информации в элементном базисе реляторов. - Таллинн: Валгус, 1989) для выделения медианного (срединного) сигнала из множества трех сигналов.

Известные устройства обладают ограниченными функциональными возможностями, так как осуществляют выделение медианного сигнала только из трех сигналов.

Наиболее близким к предлагаемому схемному решению является "Многопороговый функциональный преобразователь", построенный на реляторах - аналоговых логических элементах, воспроизводящих элементарные операции предикатной алгебры выбора (а.с. СССР 1689972, фиг.7, кл. G 06 G 7/25). Устройство при снятии сигнала с трех соответствующих выходов воспроизводит функцию селекции субмедианного, медианного и супрамедианного значений информационной переменной при произвольном числе заданного множества сигналов.

Недостатком прототипа являются большие аппаратурные затраты (количество ключей в реляторах при увеличении числа сигналов возрастает по закону арифметической прогрессии).

Технический результат - уменьшение аппаратурных затрат за счет уменьшения количества ключей.

Результат достигается тем, что в ранговом процессоре, содержащем последовательно соединенные входной демультиплексор и выходной мультиплексор, построенные соответственно на 0,5 (n + 1) и 0,5 (n - 3) реляторах, каждый из которых состоит из компаратора, управляющего группой замыкающих и размыкающих ключей, инвертирующие входы компараторов объединены и образуют информационный вход процессора, а объединенные входные выводы ключей одноканального входного релятора образуют идентифицирующий переключательный вход процессора, каждая пара разнотипных ключей (замыкающий, размыкающий) образует переключательные каналы реляторов, в демультиплексоре первый (j =1) и последний (j = i) выходы i-го релятора соединены соответственно с первым и последним переключательными входами последующего (j+1)-го релятора. В срединных выходах каждого i-го релятора четные выходы предыдущего (j-1)-го переключательного канала соединены с нечетными выходами последующего j-го переключательного канала, первый замыкающий и последний размыкающий выходы выходного релятора демультиплексора соединены соответственно с первым размыкающим и последним замыкающим переключательными входами входного релятора мультиплексора. Объединенные (j-1)-й и j-й срединные выходы выходного релятора демультиплексора соединены соответственно с объединенными (j-1)-ым и j-ым входами входного релятора мультиплексора. В мультиплексоре первый и последний выходы предыдущего релятора соединены соответственно с первым и последним входами последующего релятора. В срединных входах каждого i-го релятора четные входы предыдущего (j-1)-го переключательного канала соединены с нечетными входами последующего j-го переключательного канала. А первый, второй и третий выходы последнего релятора мультиплексора являются соответственно субмедианным, медианным и супрамедианным выходами рангового процессора.

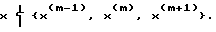

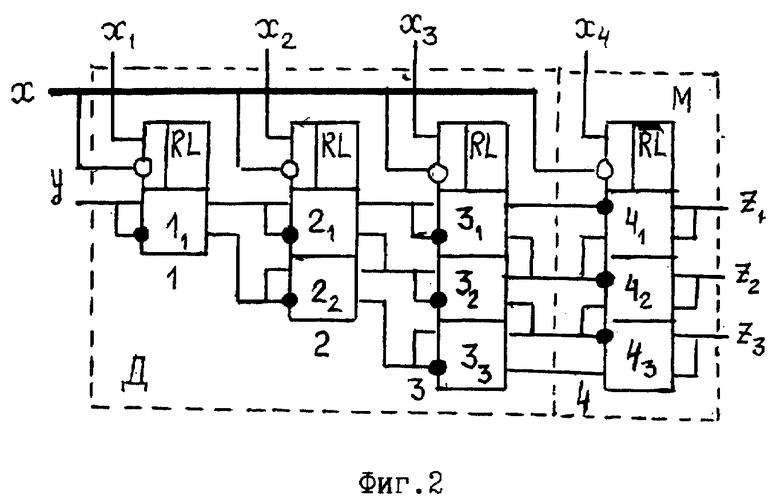

Функциональные схемы ранговых процессоров для нечетного числа n≥ 3 идентифицируемых аналоговых переменных x1, x2,...xi,..., xn изображены на фиг. 1 (n = 3), фиг.2 (n = 5) и фиг.3 (n = 7), которые построены на n-1 реляторах 1, 2, ..., ..., n-1 - логических элементах, воспроизводящих элементарные операции предикатной алгебры выбора.

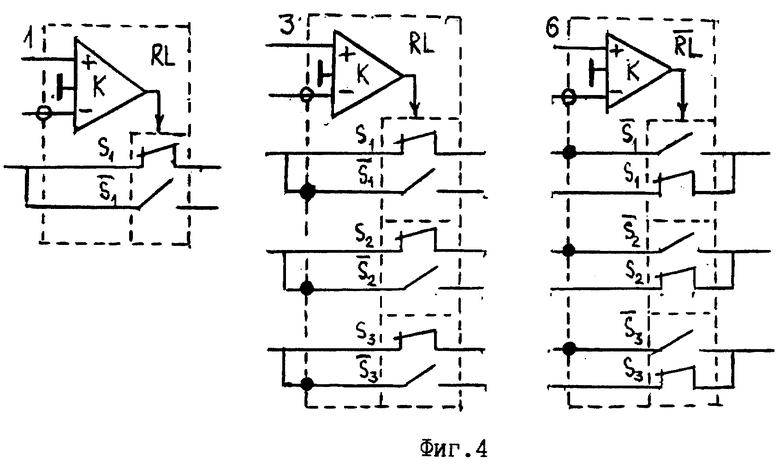

Каждый релятор (фиг.4) содержит дифференциальный компаратор K и группу переключательных каналов, каждый из которых содержит замыкающий Sj и размыкающий  аналоговые ключи, состояние которых (замкнут, разомкнут) управляется выходным напряжением компаратора (выход компаратора К соединен с управляющими входами ключей Sj и

аналоговые ключи, состояние которых (замкнут, разомкнут) управляется выходным напряжением компаратора (выход компаратора К соединен с управляющими входами ключей Sj и  ).

).

Зачерненными кружками на фиг.1-4 обозначены входные выводы размыкающих ключей. Незачерненными кружками на фиг.1-4 обозначены инвертирующие входы компараторов K реляторов RLi, которые являются инвертирующими компараторными входами реляторов. Неинвертируюшие входы компараторов являются неинвертируюшими входами реляторов.

Реляторный процессор содержит последовательно соединенные две группы: входной демултиплексор Д (реляторы 1, 2, ..., n1 = 0,5 (n +1)) и выходной мультиплексор М (реляторы n1+1, n2+2, ..., n-1, где n1 + n2 = n-1).

Реляторы RLi демультиплексора Д работают в обращенном (демультиплексорном) включении, реляторы  мультиплексора М работают в прямом (мультиплексорном) включении.

мультиплексора М работают в прямом (мультиплексорном) включении.

Каждая пара смежных разнотипных ключей Sj и  (замыкающих Sj и размыкающих

(замыкающих Sj и размыкающих  ) образует j-й переключательный канал ij i-го релятора RLi. Здесь i есть порядковая нумерация реляторов в соответствии с их цифровыми обозначениями 1, 2, ..., n - 1 от входа рангового процессора к его выходу, j - порядковая нумерация переключательных каналов в каждом реляторе в направлении сверху вниз. Входные и выходные выводы ключей Sj и

) образует j-й переключательный канал ij i-го релятора RLi. Здесь i есть порядковая нумерация реляторов в соответствии с их цифровыми обозначениями 1, 2, ..., n - 1 от входа рангового процессора к его выходу, j - порядковая нумерация переключательных каналов в каждом реляторе в направлении сверху вниз. Входные и выходные выводы ключей Sj и  переключательных каналов реляторов являются соответственно входами и выходами j-го переключательного канала реляторов.

переключательных каналов реляторов являются соответственно входами и выходами j-го переключательного канала реляторов.

Каждый i-й релятор в демультиплексоре содержит i переключательных каналов ij. В демультиплексоре Д входы каждого j-гo переключательного каналы (j = 1, 2, ...,i) i-го релятора RLi объединены и образуют переключательные входы i-го релятора. При этом выходные выводы ключей переключательных каналов являются соответственно замыкающими и размыкающими выходами реляторов RLi, общее число которых равно 2i.

В мультиплексоре М выходы каждого j-го переключательного канала  i-го релятора соединены и образуют выходы i-го релятора, общее число которых составляет n2, а входные выводы ключей переключательных каналов являются соответственно размыкающими и замыкающими входами реляторов

i-го релятора соединены и образуют выходы i-го релятора, общее число которых составляет n2, а входные выводы ключей переключательных каналов являются соответственно размыкающими и замыкающими входами реляторов  На фиг.4в изображен трехканальный релятор 6 мультиплексора М при прямом включении (объединены выходы переключательных каналов). Число 0,5 (n+1) переключательных каналов в выходном реляторе демультиплексора и во входном реляторе мультиплексора одинаково и в последующих реляторах мультиплексора уменьшается на один канал до достижения в выходном (n-1)-ом реляторе трех переключательных каналов. Объединенные входы переключательного канала первого одноканального релятора 1 (n=1) соединены и образуют идентифицирующий вход рангового процессора. Четные и нечетные выходы реляторов демультиплексора является соответственно замыкающими и размыкающими, а четные и нечетные входы реляторов мультиплексора являются соответственно размыкающими и замыкающими. В демультиплексоре первый (j=1) и последний (j = i) выходы i-го релятора соединены соответственно с первым и последним переключательными входами последующего (i+1)-го релятора. В срединных выходах каждого i-го релятора четные выходы предыдущего (j-1)-го переключательного канала соединены с нечетными выходами последующего j-го переключательного канала. Первый замыкающий и последний размыкающий выходы выходного релятора демультиплексора соединены соответственно с первым размыкающим и последним замыкающим переключательными входами входного релятора мультиплексора. Объединенные (j-1)-й и j-й срединные выходы выходного релятора демультиплексора соединены соответственно с объединенными (j-1)-ым и j-ым входами входного релятора мультиплексора. В мультиплексоре первый и последний выходы предыдущего релятора соединены соответственно с первым и последним входами последующего релятора. В срединных входах каждого i-го релятора четные входы предыдущего (j-1)-гo переключательного канала соединены с нечетными входами последующего j-го переключательного канала. А первый, второй и третий выходы последнего релятора мультиплексора являются соответственно субмедианным, медианным и супрамедианным выходами рангового процессора.

На фиг.4в изображен трехканальный релятор 6 мультиплексора М при прямом включении (объединены выходы переключательных каналов). Число 0,5 (n+1) переключательных каналов в выходном реляторе демультиплексора и во входном реляторе мультиплексора одинаково и в последующих реляторах мультиплексора уменьшается на один канал до достижения в выходном (n-1)-ом реляторе трех переключательных каналов. Объединенные входы переключательного канала первого одноканального релятора 1 (n=1) соединены и образуют идентифицирующий вход рангового процессора. Четные и нечетные выходы реляторов демультиплексора является соответственно замыкающими и размыкающими, а четные и нечетные входы реляторов мультиплексора являются соответственно размыкающими и замыкающими. В демультиплексоре первый (j=1) и последний (j = i) выходы i-го релятора соединены соответственно с первым и последним переключательными входами последующего (i+1)-го релятора. В срединных выходах каждого i-го релятора четные выходы предыдущего (j-1)-го переключательного канала соединены с нечетными выходами последующего j-го переключательного канала. Первый замыкающий и последний размыкающий выходы выходного релятора демультиплексора соединены соответственно с первым размыкающим и последним замыкающим переключательными входами входного релятора мультиплексора. Объединенные (j-1)-й и j-й срединные выходы выходного релятора демультиплексора соединены соответственно с объединенными (j-1)-ым и j-ым входами входного релятора мультиплексора. В мультиплексоре первый и последний выходы предыдущего релятора соединены соответственно с первым и последним входами последующего релятора. В срединных входах каждого i-го релятора четные входы предыдущего (j-1)-гo переключательного канала соединены с нечетными входами последующего j-го переключательного канала. А первый, второй и третий выходы последнего релятора мультиплексора являются соответственно субмедианным, медианным и супрамедианным выходами рангового процессора.

Работа рангового процессора осуществляется следующим образом. Из заданного множества аналоговых сигналов x1, x2, xi...,xn один из сигналов x = xi∈ {x1, x2,...,xn} выбирается в качестве информационной (идентифицируемой) переменной и подается на информационный вход рангового процессора. Остальные n-1 сигналов x1, xi-1, xi+1,..., xn в произвольном порядке подаются на неинвертирующие компараторные входы рангового процессора, а на его идентифицирующий вход подается идентифицирующий сигнал x.

По субмедианному z1, медианному z2 и супрамедианному z3 выходам ранговый процессор при n > 3 воспроизводит операции идентификации:

z1 = y, z2 = z3= 0 при x=x(m-1),

z2 = y, z1 = z3= 0 при x=x(m),

z3 = y, z1 = z2= 0 при x=x(m+1),

z1 = z2 = z3= 0 при  ,

,

Здесь надстрочный индекс (r) есть порядковый номер (ранг) информационной переменной x=x(r) в последовательности x(1), x(2), ... x(n), полученной ранжированием сигналов x1,..., xn в порядке их возрастания.

Таким образом, если информационная переменная x принимает субмедианное x(m-1) или медианное x(m) или супрамедианное x(m+1) значение, то возбуждается (zj= y) соответственно первый z1 или второй z2 или третий z3 выход рангового процессора, в противном случае сигнал на всех выходах рангового процессора отсутствует (z1 = z2 = z3 = 0).

При n = 3 (фиг.1) множество x1, x2, x3 содержит три сигнала, то для любой из шести ранговых ситуаций один из выходов z1, z2, z3 будет всегда возбужден и необходимость последовательного включения выходного мультиплексора отпадает.

При работе в режиме селекции необходимо соединить информационный и идентифицирующий входы рангового процессора. При этом вышеприведенные выражения остается в силе при замене в нем y на x. В этом случае информационный сигнал x проходит на один из выходов z1, z2, z3, если он принимает одно из ранговых значений x(m-1), x(m), x(m+1). При этом номер j канала zj, на который проходит сигнал x, совпадает с рангом сигнала x (j=r). Следовательно, при y = x (режим селекции) ранговый процессор является мультиплексорным коммутатором-распределителем.

В предложенном схемном решении количество используемых ключей при увеличении сигналов возрастает медленнее по сравнению с прототипом. При этом выигрыш в аппаратурных затратах увеличивается с возрастанием n. Например, при n = 3, 5, 7, 9 число ключей в прототипе и в предложенной схеме составляет соответственно 6, 20, 42, 72 и 6, 18, 34, 54.

Изобретение относится к области вычислительной техники и может быть использовано в системах допускового контроля. Техническим результатом является упрощение устройства. Процессор содержит последовательно соединенные входной демультиплексор и выходной мультиплексор, построенные на реляторах, каждый из которых состоит из компаратора и ключей. 4 ил.

Ранговый процессор для идентификации и селекции субмедианного, медианного и супрамедианного значений информационного сигнала, содержащий последовательно соединенные входной демультиплексор и выходной мультиплексор ранговой обработки нечетного числа n ≥ 5 аналоговых сигналов, которые состоят соответственно из 0,5 (n + 1) и 0,5 (n - 3) реляторов, каждый из которых содержит компаратор с инвертирующим и неинвертирующим входами, выход которого соединен с управляющими входами переключательных каналов релятора, все инвертирующие входы компараторов объединены и образуют информационный вход рангового процессора, на который подается один x из n аналоговых сигналов, являющийся идентифицируемым, а остальные n - 1 аналоговых сигналов в произвольном порядке подаются на неинвертирующие входы всех n - 1 компараторов, в демультиплексоре i-й от входа процессора релятор содержит i переключательных каналов, каждый из которых состоит из замыкающего и размыкающего аналоговых ключей, входные и выходные выводы которых являются входами и выходами этих каналов, входы переключательного канала первого релятора (i = 1) соединены и образуют переключательный вход рангового процессора, на который подается идентифицирующий сигнал, в демультиплексоре входы каждого переключательного канала реляторов соединены и образуют переключательные входы реляторов, а выходы переключательных каналов являются выходами реляторов, в мультиплексоре выходы каждого переключательного канала реляторов объединены и образуют выходы реляторов, а входы переключательных каналов являются переключательными входами реляторов мультиплексора, четные и нечетные входы реляторов демультиплексора являются соответственно замыкающими и размыкающими, а четные и нечетные переключательные входы реляторов мультиплексора являются соответственно размыкающими и замыкающими, отличающийся тем, что число 0,5 (n + 1) переключательных каналов в выходном реляторе демультиплексора и во входном реляторе мультиплексора одинаково и в последующих реляторах мультиплексора уменьшается на один канал до достижения в выходном реляторе мультиплексора (i = n - 1) трех переключательных каналов, в демультиплексоре первый и последний выходы предыдущего i-го релятора соединены соответственно с первым и последним переключательными входами последующего (i + 1)-го релятора, а в срединных выходах каждого i-го релятора демультиплексора четные выходы предыдущего (j - 1)-го переключательного канала соединены с нечетными выходами последующего j-го переключательного канала этого же релятора, первый замыкающий и последний размыкающий выходы выходного релятора демультиплексора соединены соответственно с первым размыкающим и последним замыкающим переключательными входами входного релятора мультиплексора, а соединенные попарно (j - 1)-й и j-й срединные выходы выходного релятора демультиплексора присоединены соответственно с соединенными попарно (j - 1)-ым и j-ым срединными переключательными входами релятора мультиплексора, а в мультиплексоре первый и последний выходы предыдущего релятора соединены соответственно с первым и последним переключательными входами последующего релятора, в срединных переключательных входах каждого i-го релятора мультиплексора четные входы предыдущего (j - 1)-го переключательного канала соединены с нечетными входами последующего j-го переключательного канала, а первый, второй и третий выходы последнего релятора мультиплексора являются соответственно субмедианным, медианным и супрамедианным выходами рангового процессора.

| Многопороговый функциональный преобразователь | 1989 |

|

SU1689972A2 |

| Медианный мультиплексор-демультиплексор | 1989 |

|

SU1693614A1 |

| ВОЛГИН Л.И | |||

| Синтез устройств для обработки и преобразования информации в элементах базиса реляторов | |||

| - Таллинн: Валгус, 1989, с.49 | |||

| Устройство для коммутации аналоговых сигналов | 1989 |

|

SU1679508A1 |

| Медианный идентификатор сигнала | 1989 |

|

SU1725235A1 |

| US 5642070 A, 24.06.1997. | |||

Авторы

Даты

2000-08-10—Публикация

1998-12-15—Подача