Изобретение относится к аналоговой вычислительной технике, электронным устройствам управления, автоматики и может быть использовано для построения аналоговых процессоров, для функциональных узлов аналоговых вычислительных машин, для расширения функциональных и логических возможностей приборов, устройств и систем.

Технический результат достигается тем, что в компараторно-реляторной матрице с n входами по числу входных напряжений, содержащей 0,5(n-)n реляторов, сгруппированных в n-1 вертикальных и n-1 горизонтальных групп, каждая ji-я вертикальная группа и ij-я горизонтальная группа содержит соответственно i=1, 2, ..., n-1 реляторов, в каждой ji-й (j=n+1-i) вертикальной группе инвертирующие компараторные входы реляторов объединены и присоединены соответственно к i-й входной шине, в каждой ij-й горизонтальной группе неинвертирующие компараторные входы реляторов объединены и присоединены соответственно к n-й, (n-1)-й, ..., 3-й и 2-й входным шинам.

Известны реляторные устройства частного применения для ранговой обработки аналоговых сигналов, аналоговые процессоры, коммутационно-логические преобразователи, реализующие процедуру попарного компараторного сравнения сигналов типа "один со всеми" (см., например, а.с. 1300507, кл. 4 G 06 G 7/25; а.с. 1689972, кл. 5 G 06 G 7/25).

Указанные реляторные устройства имеют ограниченные функциональные возможности, так как не позволяют воспроизводить обработку сигналов с реализацией процедуры типа "каждый со всеми".

Известны также реляторные устройства частного применения для обработки массивов аналоговых сигналов с реализацией процедуры типа "каждый со всеми" (см., например, а.с. 1541636, кл. 5 G 06 G 7/25).

Известные реляторные устройства с обработкой типа "каждый со всеми" также имеют ограниченные функциональные возможности, так как осуществляют обработку сигналов только для заданного конкретного числа n входных сигналов.

Наиболее близким к предлагаемому схемному решению является реляторная матрица в реляторном квантователе (патент РФ 2060550, кл. 6 G 06 G 7/25), которая воспроизводит попарное сравнение четырех входных аналоговых сигналов (n=4). Ограниченное (фиксированное) максимально допустимое число входных сигналов также ограничивает функциональные возможности прототипа.

Указанные ограничения устраняются в предложенном схемном решении, позволяющем проводить обработку массивов аналоговых сигналов типа "один со всеми" и "каждый со всеми" при произвольном заданном числе входных сигналов x1, x2, . . . , xn при сохранении структуры порождающей схемы меньшей размерности (свойство регулярности предлагаемого схемного решения).

Поставленная цель и технический результат достигаются тем, что в компараторно-реляторной матрице с n входами, содержащей 0,5(n-1)n реляторов, сгруппированных в n-1 вертикальных и n-1 горизонтальных групп, каждая ji-я вертикальная группа и ij-я горизонтальная группа содержит соответственно i= 1, 2, . .., n-1 реляторов, в каждой ji-й вертикальной группе инвертирующие компараторные входы реляторов объединены и присоединены соответственно к i-й входной шине, в каждой ij-й горизонтальной группе неинвертирующие компараторные входы реляторов объединены и присоединены соответственно к j-й (j=n, n-1, ..., 3, 2) входной шине.

При проведении заявителем поиска по патентным и научно-техническим источникам не было обнаружено аналогов с идентичными признаками, совпадающими с отличительными признаками заявленного схемного решения.

Схема компараторно-реляторной матрицы представлена на фиг.1.

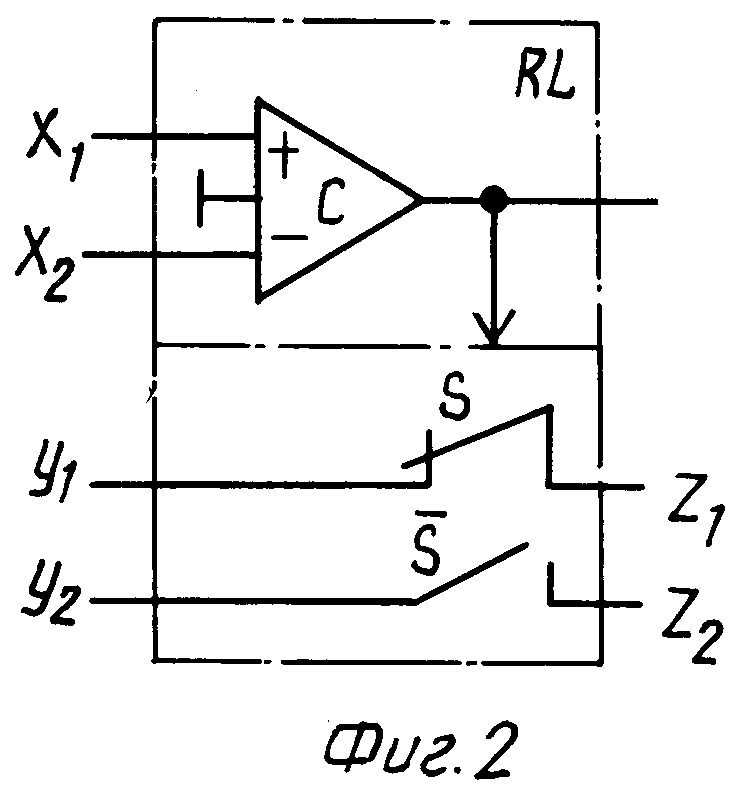

На фиг. 2 изображена схема одноканального коммутационного релятора, на которых построена компараторно-реляторная матрица.

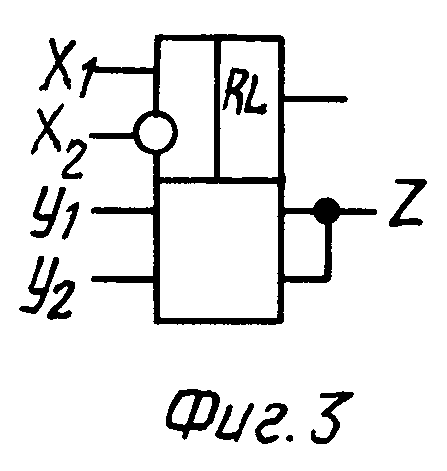

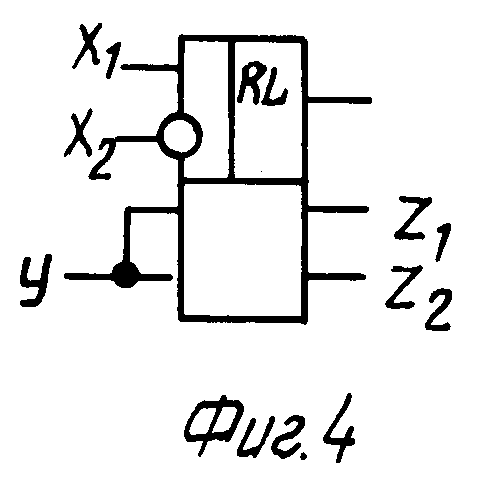

На фиг.3 и фиг.4 изображены схемы включения коммутационного релятора RL (фиг.2) в мультиплексорном (фиг.3) и демультиплексорном (фиг.4) включениях.

Каждый релятор RL, на которых построена компараторно-реляторная матрица (фиг. 1), состоит из компаратора С, выход которого соединен с управляющими входами замыкающего S и размыкающего  ключей, на которых построен коммутационный канал релятора RL. При x1>x2 (напряжение на неинвертирующем компараторном входе релятора превосходит напряжение на его инвертирующем входе) ключ S находится в замкнутом состоянии, а ключ

ключей, на которых построен коммутационный канал релятора RL. При x1>x2 (напряжение на неинвертирующем компараторном входе релятора превосходит напряжение на его инвертирующем входе) ключ S находится в замкнутом состоянии, а ключ  - разомкнутом состоянии. При x1<x2 имеем обратную картину.

- разомкнутом состоянии. При x1<x2 имеем обратную картину.

Компараторно-реляторная матрица содержит заданное число входных шин 1, 2, ..., i, ..., n (для фиг.1 n=5), на которые подаются соответственно входные аналоговые сигналы x1, x2, ..., xi, ..., xn, и содержит 0,5(n-1)n коммутационных (фиг.2), мультиплексорных (фиг.3), демультиплексорных (фиг.4) однокомпараторных одноканальных (фиг.2, 3, 4) или многоканальных реляторов RL.

Все реляторы RL компараторно-реляторной матрицы сгруппированы в n-1 вертикальных групп ji= n1, (n-1)2, ..., 3n-2, 2n-1 и n-1 горизонтальных групп ij= 1n, 2n-1, ..., (n-2)3, (n-1)2, где j=n+1-i. Каждая ji-я вертикальная и ij-я горизонтальная группы содержат соответственно i=1, 2, ..., n-1 реляторов RL. В каждой ji-й вертикальной группе инвертирующие компараторные входы реляторов объединены и присоединена соответственно к i-й входной шине, где i= 1, 2, ..., n-1. В каждой ij-й горизонтальной группе неинвертирующие компараторные входы реляторов объединены и присоединены соответственно к j-й входной шине (j=n, n-1, ..., 3, 2).

В нумерации ij каждого компараторного выхода релятора i∈{1,2,...,n} и j∈{1,2,...,n} обозначают номера входных шин, к которым присоединены соответственно инвертирующий и неинвертирующий компараторные входы данного релятора.

Работа компараторно-реляторной матрицы осуществляется следующим образом. На входные шины 1, 2, ..., n матрицы подается задающее множество аналоговых сигналов (напряжения) x1, x2, ..., xn, которые в соответствии со структурой матрицы распределяются попарно по входным компараторным входам всех 0,5(n-1)n реляторов RL.

Выходные вертикальная n1, (n-1)2, ..., 2n-1 и горизонтальная 1n, 2(n-1), . . ., (n-1)2 группы компараторно-реляторной матрицы воспроизводят процедуры сравнения сигналов типа "один со всеми".

Соответственно с компараторных выходов ij выходной вертикальной группы снимается параллельный (n-1)-разрядный код типа "продвижение единицы", идентифицирующий ранг r информационного сигнала x1=x(r) при ранжировании входных сигналов в порядке их возрастания.

При этом для выходной горизонтальной группы информационным сигналом является входной сигнал xn и на компараторных выходах реляторов горизонтальной группы снимается (n-1)-разрядный код типа "продвижение единицы", идентифицирующий ранг  информационного сигнала

информационного сигнала  при ранжировании входных сигналов x1, x2, ..., xn в порядке их убывания.

при ранжировании входных сигналов x1, x2, ..., xn в порядке их убывания.

По компараторным выходам всех реляторов RL формируется параллельно-групповой код, являющийся результатом процедуры обработки входных сигналов типа "каждый со всеми". При этом по компараторным выходам реляторов каждой вертикальной и горизонтальной подгруппам меньшей размерности воспроизводится процедура усеченной обработки типа "каждый со всеми" при числе сигналов n-1, n-2, ..., 3, 2.

Компараторно-реляторная матрица предназначена для использования в качестве встраиваемого узла для построения аналоговых процессоров, в аналоговых вычислительных машинах, для расширения функциональных и логических возможностей приборов, устройств, систем и пр.

Переключательные входы и выходы всех реляторов являются соответственно переключательными входами и выходами компараторно-реляторной матрицы. Поэтому переключательные входы и выходы реляторов оставлены открытыми, что дает возможность их внутренние и внешние межсоединения формировать в соответствии с конкретным использованием компараторно-реляторной матрицы.

Таким образом, компараторно-реляторная матрица совмещает в себе возможности обработки массивов аналоговых сигналов типа "один со всеми" и "каждый со всеми" при сохранении регулярности структуры при наращивании размерности матрицы.

Дополнительно функциональные и логические возможности расширяются за счет параллельного воспроизведения процедур типа "каждый со всеми" по каждой вертикальной и горизонтальной группам меньшей размерности n-1, n-2, ..., 3, 2. При этом появляется возможность ранжирования как в порядке возрастания (вертикальные группы), так и в порядке убывания (горизонтальные группы) сигналов, что также расширяет функциональные и логические возможности компараторно-реляторной матрицы.

Изобретение относится к аналоговой вычислительной технике, электронным устройствам управления, автоматике и может быть использовано для построения аналоговых процессоров, функциональных узлов аналоговых вычислительных машин. Техническим результатом является расширение функциональных возможностей. Устройство содержит реляторы, каждый из которых состоит из компаратора, замыкающего и размыкающего ключа. 4 ил.

Компараторно-реляторная матрица с регулярной структурой с n входами по числу входных шин, на которые подаются входные аналоговые сигнала x1, x2,... , xn, содержащая 0,5(n-1)n реляторов, сгруппированных в n-1 вертикальных и n-1 горизонтальных групп, каждый релятор состоит из компаратора, управляющего состоянием замыкающего и размыкающего ключей, входные и выходные выводы которых являются соответственно переключательными входами и выходами реляторов, отличающаяся тем, что каждая ji-я вертикальная и ij-я горизонтальная группа содержит соответственно i=1, 2, ..., n-1 реляторов, в каждой ji-й (j= n+1-i) вертикальной группе инвертирующие компараторные входы реляторов объединены и присоединены соответственно к i-й входной шине, в каждой ij-й горизонтальной группе неинвертирующие компараторные входы реляторов объединены и присоединены соответственно к j-й (j=n, n-1, ..., 3, 2) входной шине, при этом выходы всех компараторов являются компараторными выходами, а переключательные входы и выходы всех реляторов являются соответственно переключательными входами и выходами компараторно-реляторной матрицы.

| РАНГОВЫЙ КВАНТОВАТЕЛЬ | 1993 |

|

RU2060550C1 |

| Устройство для ранжирования аналоговых сигналов | 1988 |

|

SU1541636A1 |

| Амплитудный селектор | 1985 |

|

SU1251114A1 |

| Многопороговый функциональный преобразователь | 1988 |

|

SU1621054A2 |

| РАНГОВЫЙ РАСПОЗНАВАТЕЛЬ | 1999 |

|

RU2143736C1 |

| US 5642070 A, 24.06.1997. | |||

Авторы

Даты

2003-10-20—Публикация

2001-11-02—Подача