t

(21)4440419/24

(22)13.06.88

(46) 07.01.91. Бкш. f 1

(71)Уфимский авиационный институт им. Серго Орджоникидзе

(72)Ю.П.Киляев, А.П.Жиляев и А.Ф.Гимранов

(53)681.3(088.8)

(56)Авторское свидетельство СССР № 1120339,.кл. G 06 F 11/28, 1983.

Авторское свидетельство СССР № 1522216, ил. G 06 F 11/28, 1988.

(54)УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВ- ЛЯЮ1ЧЕЙ ЭВМ

(57)Изобретение относится к вычислительной технике и может быть использовано в системах автоматического

управления на базе ЭВМ для контроля выполнения программ на ЭВМ и восстановления вычислительного процесса при сбоях. Цель изобретения - уменьшение времени фиксации сбоя. Устройство содержит блоки постоянной памяти, сумматор,схему сравнения, регистры, элементы ИЛИ-НЕ, триггеры, элемент задержки, элемент И-НБ, дешифратор адреса, дешифратор команд перехода, формирователи импульсов, элемент ИЛИ, входы, выходы устройства. Устройство позволяет распознать сбой в аппаратуре контролируемой ЭВМ и восстановить вычислительный процесс путем фиксации факта сбоя и повторного выполнения команды, при которой произошел сбой. 6 ил.

а SS

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1522216A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1439605A1 |

| Устройство для контроля выполнения программ на эвм | 1986 |

|

SU1383371A1 |

| Микропрограммный процессор с контролем | 1986 |

|

SU1372328A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645960A1 |

| Микропрограммный процессор | 1984 |

|

SU1211746A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство для сопряжения ведущей и N ведомых цифровых вычислительных машин | 1988 |

|

SU1531104A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1992 |

|

RU2066877C1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах автоматического управления на базе ЭВМ для контроля выполнения программ на ЭВМ и восстановления вычислительного процесса при сбоях.

Цель изобретения - уменьшение времени фиксации сбоя.

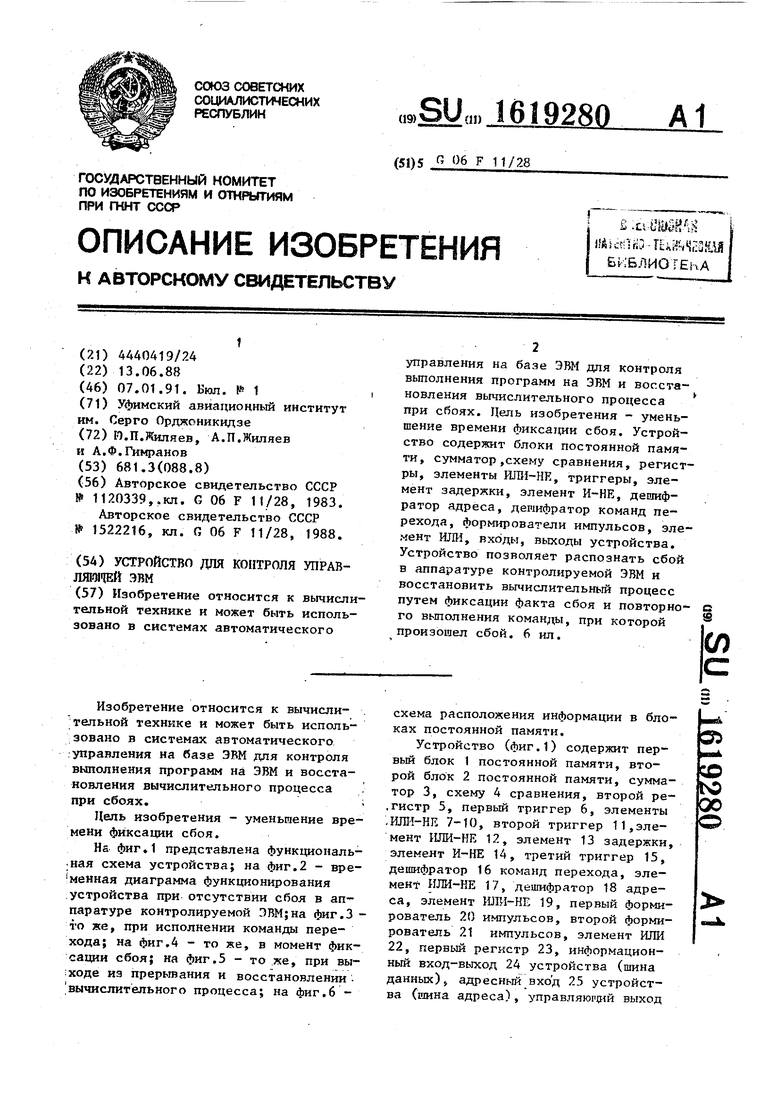

На фиг.1 представлена функциональная схема устройства; на фиг.2 - вре- менная диаграмма функционирования устройства при отсутствии сбоя в аппаратуре контролируемой Г)ВМ;на фиг.З - то же, при исполнении команды перехода; на фиг.4 - то же, в момент фиксации сбоя; на фиг.5 - то же, при выходе из прерывания и восстановлении . вычислительного процесса; на фиг.6 схема расположения информации в блоках постоянной памяти.

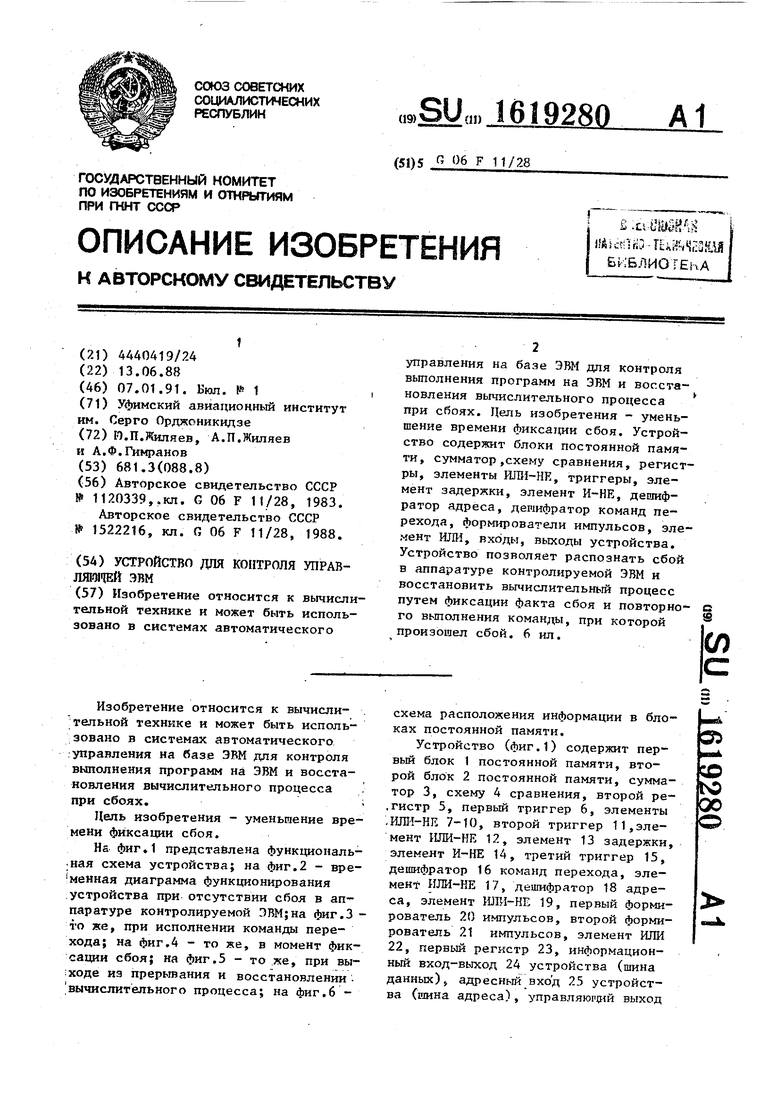

Устройство (фиг.1) содержит первый блок 1 постоянной памяти, второй блок 2 постоянной памяти, сумматор 3, схему 4 сравнения, второй ре- ,гистр 5, первый триггер 6, элементы -ИЛИ-НЕ 7-10, второй триггер 11,элемент ИЛИ-НЕ 12, элемент 13 задержки, элеме-нт И-НЕ 14, третий триггер 15, дешифратор 16 команд перехода, элемент ИЛИ-НЕ 17, дешифратор 18 адреса, элемент ИЛИ-НЕ 19, первый формирователь 20 импульсов, второй формирователь 21 импульсов, элемент ИЛИ 22, первый регистр 23, информационный вход-выход 24 устройства (шина данных), адресный вход 25 устройства (шина адреса), управляющей выход

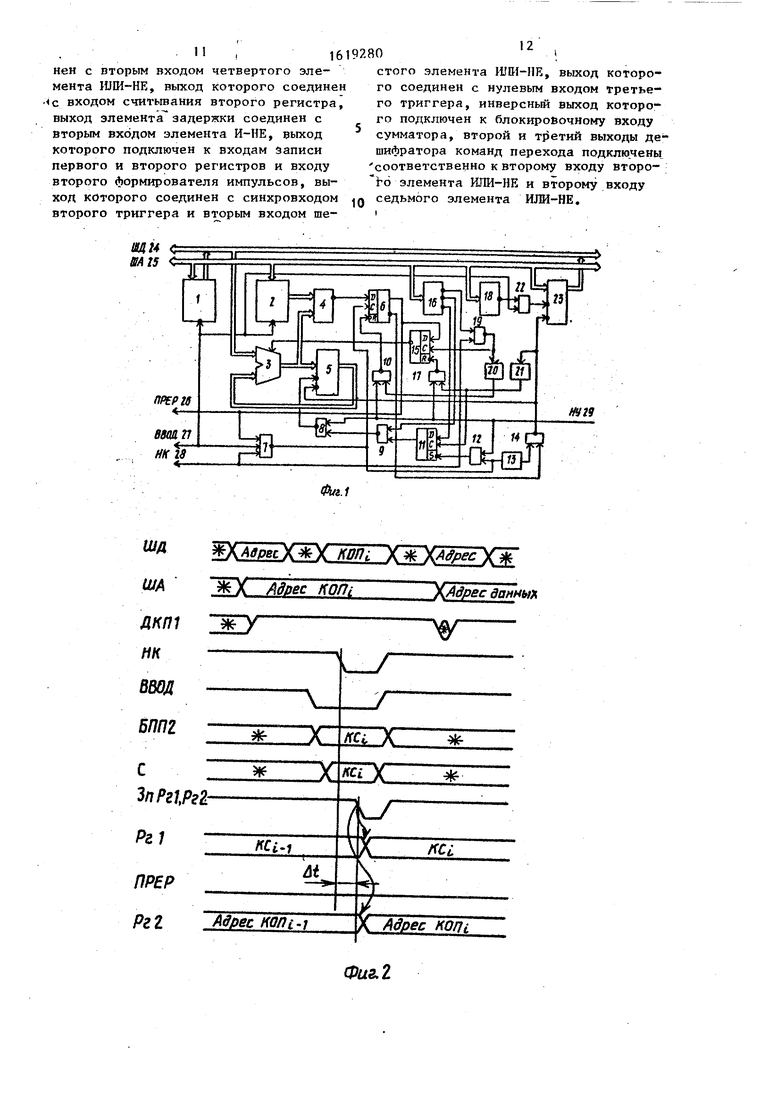

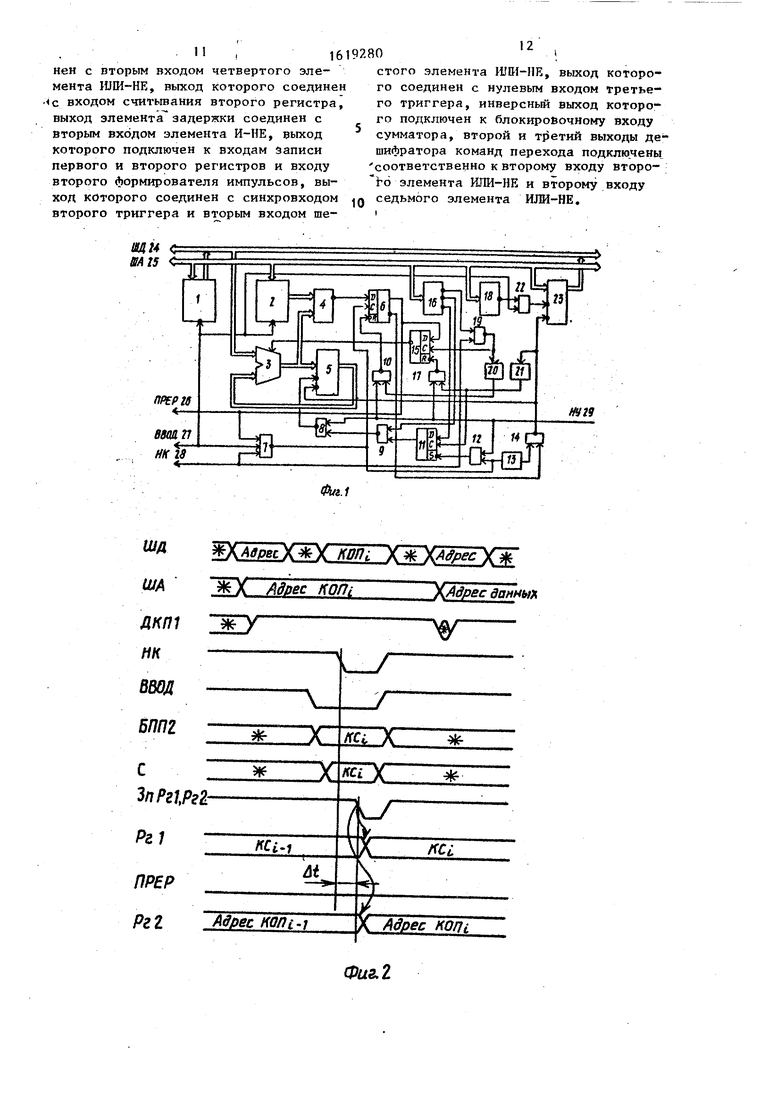

26 устройства (линия сигнала преры- вания), первый управляющий вход 27 устройства (линия сигнала ВВОД), вто-4- рой управляющий вход 28 устройства (линия сигнала начала команды), третий управляющий вход 29 устройства (линия сигнала начальной установки). На временной диаграмме функционирования устройства при отсутствии „ сбоя я аппаратуре контролируемой ЭВМ (фиг.2) обозначено: ШД - информация иа шине 24 данных, ПА - информация на шине 25 адреса, ДК11 1 - сигнал на первом выходе дешифратора 16, НК - сигнал начала команды на линии 28 сигнала, ВВОД - сигнал ввода информации в процессор контролируемой ЭВМ на линии 27 сигнат , БПП 2 - информация на информационном выходе бло- ка 2, С - информация на выходе сумматора 3; ЗпРг 1, Рг 2 - сигнал записи в регистры 5 и 23 с выхода элемента И-НЕ 14, Рг 1 - информация на выходе регистра 5, ПРЕР, - сигнал прё рывания на линии 26 сигнала, Рг 2 - содержимое регистра 23, КОП - код операции текущей команды контролируемой ЭВМ, КС - контрольная схема, ftt - время задержки элемента 13 за- держки (# - уровень сигнала не имеет значения).

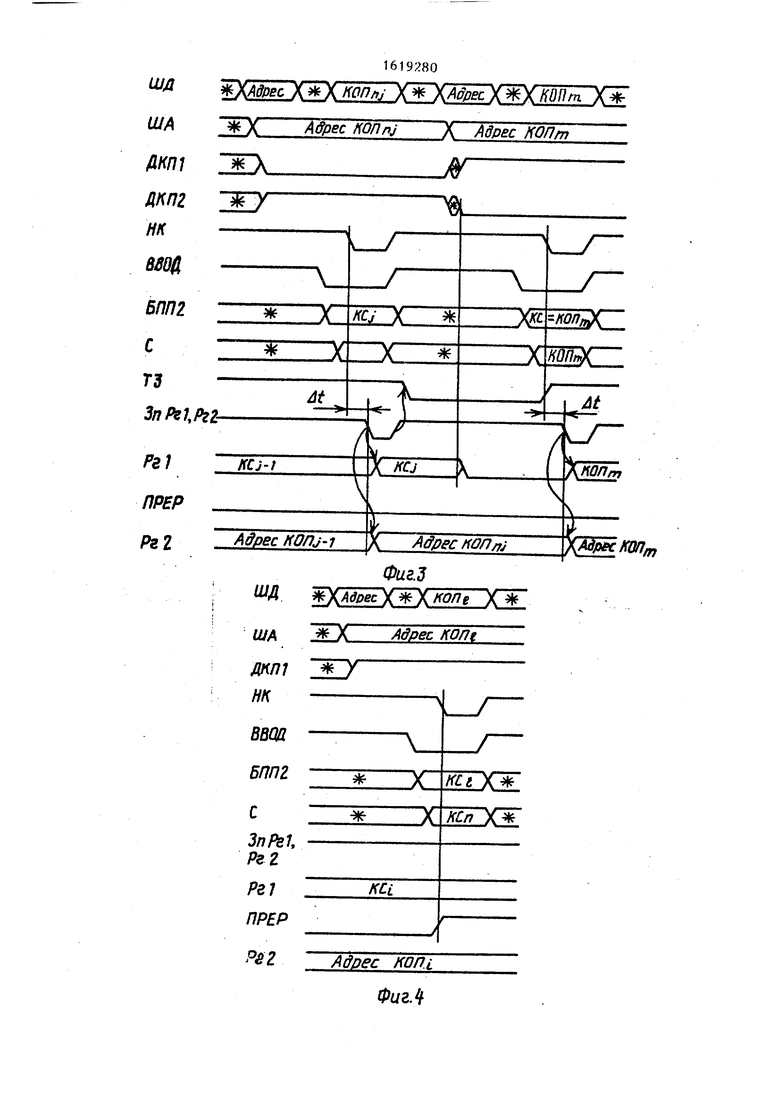

Иа временной диаграмме функционирования устройства при исполнении команды перехода (фиг.З) обозначено: ИД - информация на шине 24 данных, 1ЧА - информация на шине 25 адреса, ДКП 1 - сигнал на первом выходе де шифратора 16, ДКЛ 2 - сигнал на вто- ром выходе дешифратора 16, НК - сиг- нал на линии 28 сигнала, ВВОД - сигнал ввода информации в процессор ЭВМ| на линии 27 сигнала, БПП - информация на ичформационном выходе блока 2, С - информация на выходе сумматора 3, Т 3 - сигнал на прямом выходе триггера 11, ЗпРг 1, Рг 2 - сигнал запи- си в регистры 5 и 23 с выхода элемен-4 та И-НЕ 14, Рг 1 - информация на выходе регистра 5, ПРЕР - сигнал преры- вания на линии сигнала 26 прерывания, Рг 2 - содержимое регистра 23, КОГ1 - код операции, КС - контрольная сумма, b,t - время задержки элемента 13 задержки.

На временной диаграмме функционирования устройства при выходе из прерывания и восстановлении вычислительного процесса (фиг.З) обозначено:

g 5 0 5

о $

5

0

5

ШД - информация на шине 24 данных,ША - информация на шине 25 адреса, ДКПЗ - сигнал на третьем выходе дешифратора 16, ПК - сигнал начала команды на линии 28 сигнала начала команды, ВВОД - сигнал ввода информации в процессор ЭВМ на линии 27, БПП 2 - информация на информационном выходе блока 2, С - информация на выходе сумматора 3, ЗиРг 1, Рг 2 - сигнал i записи в регистры 5 и 23 с выхода элемента И-НЕ 14, Рг 1 - информация на выходе регистра 5, Сбр Т1 - сигнал сброса триггера 6 на выходе элемента ИЛИ-НЕ 10, ПРЕР - сигнал прерывания на линии 26 сигнала прерывания, Сбр Т2 - сигнал сброса триггера 15 на выходе элемента ИЛИ-НЕ 17, Т2 - сигнал на инверсном выходе триггера 15, Рг 2 - содержимое регистра 23, КОП - код операции, КС - контрольная сумма, ut - время задержки элемента 13 задержки.

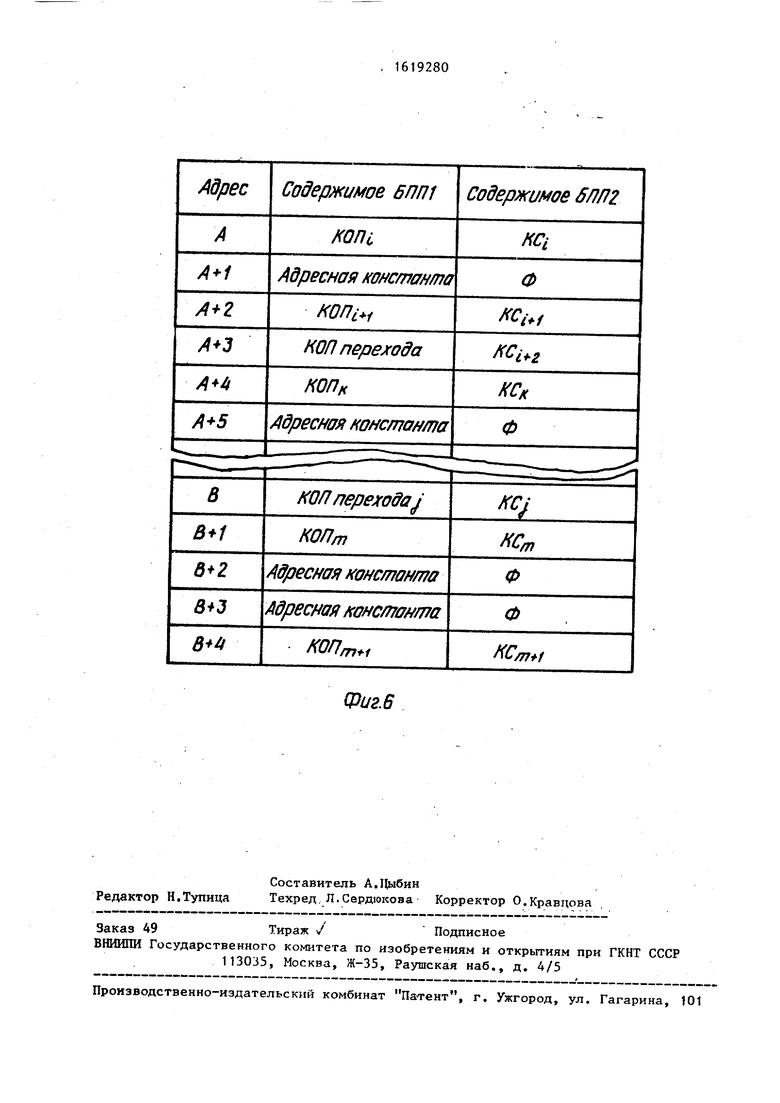

На схеме расположения информации в блоках 1 и 2 (фиг.6) А, В - относительные адреса ячеек блока 1 и бло- ка 2, КОП - код операции, КС - контрольная сумма.

Устройство функционирует следующим образом.

Рабочая программа контролируемой ЭВМ заносится в блок 1, а контрольные суммы - в блок 2.Адреса блоков 1 и 2 совпадают. Контроль вычислительного процесса осуществляется во время считывания из блока 1 кода очередной команды посредством срагнения суммы считываемого кода команды и содержимого регистра 5 с контрольной суммой, извлекаемой из блока 2. Адреса ячеек блока 1, содержащих коды операции (команд), и ячеек блока 2, содержащих соответствующие контрольные суммы, совпадают ().

Если сравниваемые суммы с выходов сумматора 3 и блока 2 совпадают, то производится запись соответствующей , |суммы с выхода сумматора 3 в регистр 5. При несовпадении сравниваемых ,сумм вырабатывается сигнал прерывания, затем производятся действия по восстановлению вычислительного процесса.

Рассмотрим выполнение i-й команды в отсутствии сбоев во время выпол нения предыдущей команды (фиг.2). Процессор ЭВМ передает по шине 24 адрес ячейки блока 1, содержащий

код операции г-й команды (), после выставления этого адреса на шине 25 процессор ЭВМ вырабатывает сигнал ВВОД, затем сигнал начала, передаваемые по линиям 27 и 28 соответственно, сигнализируя о том,что процессор готов принять информацию от блока 1. Сигнал ВВОД поступает на входы считывания блока 1, из которого считывается КОГГ на шине 24, и блока 2, из которого на первый информационный вход схемы 4 сравнения считывается контрольная сумма KCj1 . Одновременно на второй информационный вход сумматора 3 поступает КОП с шины ГД 24, а на первый информационный вход сумматора 3 с выхода регистра 5 поступает КС , с предыдущего шага сравнения (считывания из блока 1 КОП }., ) .

На выходе сумматора 3 формируется сумма, совпадающая с KC,j, которая поступает на второй информационный вход схемы 4 сравнения, на выходе которой формируется сигнал уровня О, поступающий на информационный вход триггера 6. Сигнал начала команды с линии 28 появляется с. некоторой задержкой относительно сигнала ВВОД для срабатывания блока 1, сумматора 3 и схемы 4 сравнения. Сиг- нал начала команды поступает на третий вход элемента ИЛИ-НЕ 7, с выхода которого сигнал поступает на синхровход триггера 6. По фронту этого сигнала триггер 6 устанавливается в состояние/ соответствующее уровню сигнала на его информационном входе, т.е. остается в нулевом состоянии. Затем этот же сигнал с выхода элемента ИЛИ-НЕ 7 через элемент 13 задержки и элемент И-НЕ. 1 поступает на входы записи регистра 23 и регистра 5. В регистр 5 заносится по этому сигналу КС с выхода сумматора 3 и в регистр 23 заносится адрес КОП. Элемент 13 задержки задерживает сигнал с выхода элемен- та ИЛИ-НЕ 7 на время Јt, необходимое для срабатывания триггера 6.

Дешифратор 16 представляет собой трехразрядное постоянное программируемое запоминающее устройство с полем адресов, соответствующим полю адресов блока 1 и блока 2. В трехразрядные ячейки дешифратора 16 по адресам, совпадающим с адресами ячеек блока 1, которые хранят коды операции перехода, заносятся кодгл 110 (младший разряд этого кода соответствует первому выходу дешифратора 16, а старший разряд - третьему выходу дешифратора 16). В ячейки дешифратора 16 по адресам, совпадающим с адресами ячеек блока 1, которые хранят первые коды операции линейных

участков (по адресам начала линейных участков программы), заносятся коды 101. В ячейку дешифратора 16 по адресу, совпадающему с адресом последней команды программы обработки пре5 рывания (команды выхода из прерывания), заносится код 011. В остальные ячейки дешифратора 16 заносятся коды 111.

Рассмотрим выполнение j-й команды

0 перехода к гч-му линейному участку программы (фиг.З). При появлении адреса кода операции перехода (КОПц.) на шину 25 на первом выходе дешифратора 16 появляется сигнал О, кото5 рый поступает на информационный вход триггера 11. Если при считывании K0nnj сбой не был зафиксирован,то вы рабатывается сигнал записи в регистре 5 и регистре 23 с выхода элемента

0 И-НЕ 14, который поступает одновременно на вход второго формирователя 21 импульсов,вырабатывающий по фронту входного сигнала импульс 1. По фронту импульса с выхода формирователя 21 импульсов в нулевое состояние устанавливается триг-1 гер 11, соответствующее уровню сигнала на его информационном входе. С прямого выхода триггера 11 на второй

0 вход элемента ИЛИ-НЕ 9 поступает сиг-4 нал О. После ввода в процессор кон- тренируемой ЭВМ КОПП/ в регистре 5 хранится КС., в регистре 23 - адрес КОП nj. После выполнения j-й команды

5 перехода процессора ЭВМ передает по шине 24 адрес начала m-го линейного участка (адрес КОП) в случае, если не произошел сбой при выполнении j-й команды перехода. При появлении

0 адреса КОП на шине 25 на втором

выходе дешифратора 16 появляется сигнал О, который поступает на первый вход элемента ИЛИ-НЕ 9, на выходе которого появляется сигнал 1, постуе пающий через элемент ИЛИ-НЕ 8 на нулевой вход регистра 5, и обнуляет его. Если при исполнении j-й команды перехода произошел сбой, в результате которого процессор контролируе-

мой ЭВМ выйдет не на начало линейного участка, то регистр 5 не обнулит- ся и при вводе п процессор информации из ячейки блока 1 по адресу,передаваемому по шине 24 в этот момент будет зафиксирован сбой.

При вводе в процессор ЭВМ КОП,т в случае, если сбоя при выполнении j-й команды перехода не произошло, осуществляется сравнение в схеме 4

сравнения КОПти выхода сумматора гистра 5) и т.д.

КСМ 0 + КОПтс 3 (0 - с выхода ре- , как в рассмотренном случае при отсутствии сбоев в аи- регистра 23, з котором находится КОП4 .

паратуре контролируемой ЭВМ. С появлением сигнала начала команды сигнал с выхода элемента ИЛИ-НЕ 7 через элемент ИЛИ- Г 12 в единичное состояние устанавливает триггер 11„

Допустим, что в аппаратуре контролируемой ЭВМ при исполнении i-й команды произошел сбой, который привел к искажению вычислительного про- |цесса, в результате чего процессор ЭВМ вместо ячейки блока 1, содержащей КОИ fa , обратился к ячейке, сс- держащей, например, КОП. После по- |явления на гоине 24 KOIIg (фиг.4) на выходе сумматора 3 появляется КСП КС j + КОЛ п, а из блока 2 считывается по выставленному на шине 25 адресу - КСр. На выходе схемы 4 сравнения при несовпадении информации на ее входах появляется сигнал 1 и по фронту сигнала с выхода элемента ИЛИ-ИЕ 7 в единичное состояние устанавливается триггер 6, с прямого выхода которого по линии 26 в процессор контролируемой ЭВМ поступает сигнал прерывания, вызывающий прерывание рабочей программы ЭВМ. Одновременно сигнал О с инверсного выхода триггера Ь поступает- на вто- , рой вход элемента И-НЕ 14 и запрещает прохождение через него сигнала 1 с выхода элемента 13 задержки,тем самым препятствуя формированию сигнала записи регистра 5 и регистра 23. Сигнал прерывания уровня 1 также поступает на первый вход элемента ИЛИ-НЕ 7, препятствуя прохождению через него сигналов с линии 27 и начала команды с линии 28.

Для организации прерывания в контролируемой ЭВМ процессор загружает в стек сначала содержимое счетчика команд процессора, затем слово состо я.шя процессора ЭВМ. В счетчик ко20

25

30

35

40

45

50

55

После появления этого адреса на шине 25 (фиг.5) он распознается дешифратором 18, на выходе которого появляется сигнал О, поступающий на первый вход элемента ИЛИ 22. При появлении сигнала ВВОД на линии 27, который поступает на второй вход элемента ИЛИ 22, на его выходе появляется О - сигнал считывания из регистра 23.

При появлении на шине 25 адреса команды выхода из прерывания (КОП8пр) на третьем выходе дешифратора 16 появляется сигнал О, который поступает на первый вход элемента ИЛИ-НЕ 19. Сигнал начала команды линии 28 поступает на второй вход элемента ИЛИ-НЕ 19. По фронту сигнала с выхода элемента ИЛИ-НЕ 19 в единичное состояние устанавливается триггер 15, так как на его информационный вход поступает сигнал прерывания уровня 1. На инверсном выходе триггера 15 в этот момент появляется сигнал О, который поступает на блокировочный вход сумматора 3. В этом случае блокируется второй информационный вход сумматора Зи на его информационный выход передается информация с первого информационного входа сумматора 3, т.е. информация из регистра 5.

По фронту сигнала с выхода элемента ИЛИ-НЕ 19 первый формирователь 20 импульсов вырабатывает сигнал 1, который через элемент ИЛИ-НЕ 10 обнуляет триггер 6 (сигнал прерывания снимается). Процессор ЭВМ вы- ходчт из прерывания и управление происходит по адресу КОП,1, т.е. повторно выполняется i-я команда, во время исполнения которой произошел сбой. , При появлении на шине 24 КОП J на выходе сумматора 3 остается КС,1, так как сумматор 3 блокирован по второму

манд после этого загружается адрес начапа программы обработки прерывания, которая состоит из команды пересылки КОП из регистра 23 в стек на место содержимого счетчика команд и команды выхода из прерывания:

MOV RG, +2(SP) RTI (RG - адрес регистра 23).

Для того, чтобы извлечь содержимое регистра 23, процессор ЭВМ по шине 24 программно передает адрес

0

5

0

5

0

5

0

5

После появления этого адреса на шине 25 (фиг.5) он распознается дешифратором 18, на выходе которого появляется сигнал О, поступающий на первый вход элемента ИЛИ 22. При появлении сигнала ВВОД на линии 27, который поступает на второй вход элемента ИЛИ 22, на его выходе появляется О - сигнал считывания из регистра 23.

При появлении на шине 25 адреса команды выхода из прерывания (КОП8пр) на третьем выходе дешифратора 16 появляется сигнал О, который поступает на первый вход элемента ИЛИ-НЕ 19. Сигнал начала команды линии 28 поступает на второй вход элемента ИЛИ-НЕ 19. По фронту сигнала с выхода элемента ИЛИ-НЕ 19 в единичное состояние устанавливается триггер 15, так как на его информационный вход поступает сигнал прерывания уровня 1. На инверсном выходе триггера 15 в этот момент появляется сигнал О, который поступает на блокировочный вход сумматора 3. В этом случае блокируется второй информационный вход сумматора Зи на его информационный выход передается информация с первого информационного входа сумматора 3, т.е. информация из регистра 5.

По фронту сигнала с выхода элемента ИЛИ-НЕ 19 первый формирователь 20 импульсов вырабатывает сигнал 1, который через элемент ИЛИ-НЕ 10 обнуляет триггер 6 (сигнал прерывания снимается). Процессор ЭВМ вы- ходчт из прерывания и управление происходит по адресу КОП,1, т.е. повторно выполняется i-я команда, во время исполнения которой произошел сбой. , При появлении на шине 24 КОП J на выходе сумматора 3 остается КС,1, так как сумматор 3 блокирован по второму

916

информационному входу, из блока 2 считывается по выставленному на шине 25 адресу - КС. В этом случае на выходе схемы 4 сравнения сигнал О и триггер 6 в единичное состояние не устанавливается, затем формируется сигнал записи в регистре 5 (заносится KCj с выхода сумматора 3) и в регистре 23 (заносится адрес КОП|). По фронту сигнала записи регистров 5 и 23 второй формирователь 21 импульсов вырабатывает импульс уровня 1, который через элемент ШШ-НЕ 17 обнуляет триггер 15, сигнал блокировки сумматора 3 снимается.

Если в результате сбоя на шине 24 появляется адрес не очередного КОП, а адрес каких-либо данных, то в этом случае из блока 2 будет считан нулевой код и при сравнении этого нулевого кода с информацией с выхода сумматора 3 будет также зафиксирован сбой.

Таким образом, предлагаемое устройство позволяет распознать сбой в аппаратуре контролируемой ЭВМ и восстановить вычислительный процесс путем фиксации факта сбоя и повторного выполнения команды, при исполнении которой произошел сбой.

Формула изобретения

Устройство для контроля управляющей ЭВМ, содержащее два блока постоянной памяти, сумматор, схему сравнения, два регистра, три триггера, элемент задержки, дешифратор команд перехода, дешифратор адреса, два формирователя импульсов, элемент ИЛИ, причем информационные входы дешифратора команд перехода, дешифратора адреса и первого регистра, адресные входы первого и второго блоков постоянной памяти подключены к адресному входу устройства для подключения к тине адреса контролируемой ЭВМ, выходы первого блока постоянной памяти и первого регистра, первый информационный вход сумматора подключены к информационному входу- выходу устройства для подклюения к шине данных контролируемой ЭВМ, информационный выход сумматора подключен к информационному входу второго регистра, выход которого соединен с вторым информационным входом сумматора,прямой выход первого триггера

10

Q280

является выходом прерывания для подключения к шине управления контролируемой ЭВМ, вход ввода устройства для подключения к шине управления контролируемой ЭВМ соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом дешифратора адреса, выход элемента ИЛИ подjQ ключей к входу считывания первого регистра,первый выход дешифратора команд перехода соединен с информационным входом второго триггера, выход схемы сравнения соединен с информациJ5 онным входом первого триггера, отличающееся тем, что, с целью уменьшения времени фиксации сбоя, в него дополнительно введены семь элементов ИЛИ-НЕ, элемент И-НЕ,

20 причем первый информационный вход схемы сравнения соединен с выходом второго блока постоянной памяти, а второй информационный вход схемы сравнения - с выходами сумматора, уп5 равняющие входы первого и второго

блоков постоянной памяти, первый вход первого элемента ИЛИ-НЕ подключен к входу ввода устройства для подключения к шине управления контролируемой

30 ЭВМ, к входу начальной команды устройства для подключения к шине управления контролируемой ЭВМ подключены второй вход первого элемента ИЛИ-НЕ и первый вход второго элемента ИЛИ-НЕ, выход которого соединен с синхровхо- дом третьего триггера и входом первого формирователя импульсов, выход которого соединен с первым входом третьего элемента ИЛИ-НЕ, второй вход

4« третьего элемента ИЛИ-НЕ и первые входы четвертого, пятого и шестого элементов ИЛИ-НЕ подключены к входу начальной установки устройства, прямой выход первого триггера соединен

5 информационным входом третьего

триггера и третьим входом первого элемента ИЛИ-НЕ, инверсный выход первого триггера соединен с первым входом элемента И-НЕ, выход первого элемен0 та ИЛИ-НЕ подключен к входу элемента задержки, второму входу пятого эле- . мента ИЛИ-НЕ, к синхровходу первого триггера, нулевой вход которого соединен с выходом третьего элемента g ИЛИ-НЕ, выход пятого элемента ИЛИ-НЕ соединен с единичным входом второго триггера, прямой выход которого подключен к первому входу седьмого элемента ИЛИ-НЕ, выход которого соеди5

ШИ С ША15

прЕрге

вшя

ПК18

Фиг. 2

Фиг4

J ICM

«о ь

CvS

«5

Фиг.6

Авторы

Даты

1991-01-07—Публикация

1988-06-13—Подача