Изобретение относится к криптографическим преобразованиям и может быть использовано в связных, вычислительных и информационных системах для криптографического закрытия двоичной информации.

Цель изобретения - упрощение аппаратной реализации устройства шифрования до возможности его размещения на микросхеме, содержащей не более 2 тысяч вентилей, а также использование ключа такой длины, которая обеспечивает невозможность его опробывания за разумное время.

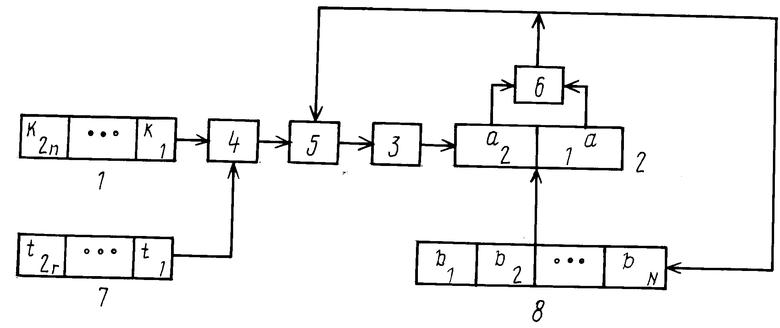

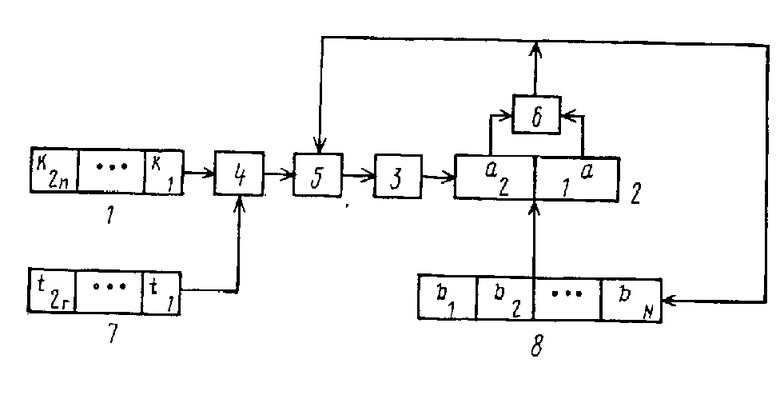

На чертеже представлена блок-схема предлагаемого устройства.

Устройство шифрования двоичной информации содержит 8-разрядный ключевой регистр 1, 8-разрядный информационный регистр 2, блок 3 четырехразрядный функционального преобразования f, первый, второй, третий четырехразрядные сумматоры 4-6 по модулю два, 8r-разрядный регистр и 7 и N-разрядный регистр 8.

Устройство шифрования двоичной информации работает следующим образом.

Выработка полубайта шифрограммы Ш осуществляется следующим образом.

1. В 8-разрядный информационный регистр 2 из N-разрядного регистра 8 записываются восемь бит, например, младших, bj1, . . . , bj8 (или два полубайта, а2 (1), а1 (1)) исходной информации. Здесь b1, . . . , bN - содержимое N-разрядного регистра 8, bj = 0,1, j = 1, N.

2. Устройство работает пять циклов, все циклы работы идентичны. В i-й, 1 <= i <= s цикл работы к сумме i-го (по модулю 2n) полубайта ключевого регистра 1 и i-го (по модулю 2r) полубайта ключевого регистра 7 прибавляется сумма первого и второго полубайтов 8-разрядного информационного регистра 2, полученная схема преобразуется блоком 3 и результат записывается в 8-разрядный информационный регистр 2 на освободившееся место после сдвига его содержимого на один полубайт в сторону младших разрядов (вправо). После i-го цикла содержимое 8-разрядного информационного регистра 2 следующее:

a2 ( i + 1 ) = f ( ki(mod2n) +

+ ti(mod2r) + ( a1 ( i ) + a2 ( i ) ),

a1 ( i + 1 ) = a2 ( i ), i = > 1, где а2(i), a1(i) - два полубайта 8-разрядного информационного регистра 2 перед началом i-го цикла, 1 <= i < = s;

a2(i), a1(i) - исходное состояние регистра 2;

а2(s+1), a1(s+1) - результирующее состояние регистра 2,

k1, . . . , k2n - 2n полубайт - n -байтного ключа,

t1, . . . , t2r - 2r полубайт содержимого регистра 2;

+ - сложение полубайтов по модулю 2 либо 24,

f - функция 24-значной логики (система 4-двоичных функций от 4-двоичных переменных);

a1 ( i ), a2 ( i ), ki, ti( - { 0,1, . . . , 1,5 } , i = > 1.

Если выбрать третий четырехразрядный сумматор 6 по модулю 24, а первый и второй четырехразрядные сумматоры 4 и 5 по модулю 2, к ключевому полубайту прибавлять сначала полубайт из регистра 7, а затем уже сумму полубайтов регистра 2, то после i-го цикла содержимое 8-разрядного информационного регистра 2 следующее:

a2(i+1)= f(ki(mod2n)⊕ ti(mod2r)⊕ (a1(i) a2(i)),

a2(i)),

a1( i + 1 ) = a2 ( i ), i = > 1

⊕ - поразрядное сложение полубайтов по модулю 2; - сложение полубайтов по модулю 24.

- сложение полубайтов по модулю 24.

3. Сумма полученных в 8-разрядном информационном регистре 2 после s-го цикла двух полубайт а1(s+1), a2(s+1) является полубайтом шифргаммы Ш, т. е. Ш= a1(s+1) a2(s+1).

a2(s+1).

В блоке 3 реализуется функция 24-значной логики, представленная в дизъюнктивной форме системой четырех двоичных функций y1, . . . , y4 от четырех двоичных переменных х1, . . . , х4, y1, x = 0,1, i = 1,4.

В качестве функционального преобразования f можно выбрать, например, следующее:

y1 = x1x4 v x1x2x4 v x1x2x3x4 v x1x2x3x4

y2 = x2x3 v x2x3x4 v x1x2x3x4 v x1x2x3x4

y3 = x1x2x3 v x1x3x4 v x1x2x3 v x1x3x4

y4 = x2x3x4 v x1x2x3 v x1x2x3 v x2x3x4

Увеличение числа циклов работы устройства шифрования повышает уверенность в криптографической надежности зашифрования информации, т. е. в том, что никому не удастся расшифровать сообщение за время, меньшее чем полное опробование всех возможных вариантов n-байтного ключа. Вместе с тем, чем больше циклов работает устройство для выработки одного полубайта шифргpаммы, тем меньше его производительность. Это дает возможность выбора между риском и производительностью. Рекомендуется выбирать число 5 циклов работы устройства шифрования в пределах от 4n до 16n, где n - длина ключа в байтах. Реальная длина ключа - от 8 до 16 байт.

Для выработки следующего полубайта шифргаммы используются 8 бит bj1, . . . , bj8 следующего состояния N-разрядного регистра 8.

В качестве N-разрядного регистра 8 можно выбрать 15-разрядный регистр сдвига со следующей линейной функцией максимального периода 2-151 в обратной связи: b16 = b1 ⊕ b2. Если текущее состояние регистра сдвига обозначить через b1, . . . , b15, где bi = 0, 1, 1 = 1,15, то следующее состояние регистра сдвига будет b2, . . . , b15, b1⊕ b2.

В 8r-разрядный регистр 7 записывается представленное в двоичном виде текущее время (месяц, число, час, минута, секунда) или случайное число, выработанное датчиком случайных чисел. Вместе с временем или случайным числом можно записывать также и номер передающего абонента. Реальная длина регистра 87 - 4-8 байт. Очередное состояние 8r-разрядного регистра 7 используется для выработки 2N-1 полубайт шифргаммы Ш, после чего в 8r-разрядный регистр 7 записывается новое время или новое случайное число.

При использовании единого времени оно не должно повторяться все время действия ключа. Например, если ключ действует один год, то время должно включать в себя месяц, если ключ действует несколько лет, то также и год.

После установки нового состояния в 8r-разрядный регистр 7 устройство шифрования формирует новое начальное состояние N-разрядного регистра 8. В случае 15-разрядного битного двоичного регистра сдвига можно предложить следующую процедуру формирования нового начального состояния.

Устройство шифрования прокручивается 5 циклов, как это было описано. Полученные после m-го, 3m-го, 5m-го, 7m-го циклов, где m это целая часть числа 8-1 s, 4 полубайта

а2 ( m + 1 ) + a1 ( m + 1 ),

a2 ( 3m + 1 ) + a1 ( 3m + 1 ),

a2 ( 5m + 1 ) + a1 ( 5m + 1 ),

a2 ( 7m + 1 ) + a1 ( 7m + 1 ) записываются в регистр 8. В старшие два бита полубайта а2 ( 7m + 1 ) + a1 ( 7m + 1) принудительно записываются знаки 1. Так как в выбранном регистре 8 всего 15 разрядов, то четвеpтый бит последнего полубайта не используется.

Очередное состояние 8r-разрядного регистра 7 и новое исходное состояние 15-разрядного двоичного регистра 8 сдвига используются для выработки 214-полубайт (-216 бит) шифргаммы, после чего требуется обновление состоянии регистров 7 и 8.

Шифргамма Ш складывается по модулю 2 с представленным в двоичном виде открытым сообщением А. Полученное зашифрованное сообщение В = А ⊕ Ш вместе с заполнением 8r-разрядного регистра 7 передается получателю.

Принимающий абонент устанавливает в 8r-разрядный регистр 7 своего устройства шифрования принятые r байт и вырабатывает описанным способом шифргамму Ш. Затем принимающий абонент складывает ее по модулю 2 с принятым зашифрованным сообщением В и получает открытое сообщение А = В ⊕ Ш. (56) Сяо Д. , Керр Д. и Мэдник С. Защита ЭВМ. М. : Мир, 1982, с. 137-162.

Использование: в технике криптографических преобразований в связных, вычислительных и информационных системах для криптографического закрытия двоичной информации. Сущность изобретения: устройство содержит n-байтный ключевой регистр 1, однобайтный информационный регистр 2, блок 3 функционального преобразования, первый, второй, третий четырехразрядные сумматоры 4 - 6 по модулю два, r-байтный регистр 7, N-битный регистр 8. Обеспечивается возможностью реализации устройства на микросхеме, содержащей всего лишь 2 тыс. вентилей, использования ключа такой длины, которая обеспечивает невозможность его опробования за разумное время. Устройство улучшает криптографические и эксплуатационные параметры устройства шифрования. 2 з. п. ф-лы, 1 ил.

Авторы

Даты

1994-02-15—Публикация

1991-11-22—Подача