Изобретение относится к области криптографических преобразований и может быть использовано в связных, вычислительных и информационных системах для криптографического закрытия двоичной информации.

Техническим результатом изобретения является шифрование информации блоками различной длины с использованием ключа такой длины, которая обеспечивает невозможность его опробования за разумное время.

Известен способ шифрования, предназначенный для криптографической защиты информации в вычислительных системах и заключающийся в многократном прибавлении ключа к преобразуемой информации с последующим применением подстановочных и перестановочных преобразований. С использованием этого способа построена система Lucifer фирмы IBM и стандарт шифрования данных национального бюро стандартов США.

В известном стандарте шифрования данных к содержимому двух 32-разрядных ячеек 64-разрядного информационного регистра 16 раз прибавляют по модулю 2 содержимое 64-разрядного ключевого регистра с последующим воздействием на 32-разрядную сумму 32-разрядным функциональным преобразованием.

Известный стандарт шифрования данных шифрует информацию блоками по 64 бита. При зашифровании блоков меньшей длины длина зашифрованного сообщения (64 бита) больше длины открытого сообщения. Кроме того, в известном стандарте используется слишком маленький ключ, что позволяет вскрыть его простым перебором за разумное время.

Технический результат достигается тем, что в способе шифрования двоичной информации, заключающемся в зависящем от 64-разрядного ключа преобразовании двух 32-разрядных ячеек 64-разрядного информационного регистра путем 16-кратного выполнения набора операций, включающего поразрядное сложение по модулю 2 содержимого 32-разрядных ячеек информационного регистра с содержимым 32-разрядных ячеек ключевого регистра и последующее функциональное преобразование полученной 32-разрядной суммы, преобразуют m≥1 p-разрядных (P≥2) ячеек mp-разрядного информационного регистра путем n-кратного выполнения следующих операций: к содержимому m-й p-разрядной ячейки информационного регистра (либо к 0, если m=1) прибавляют (например, по модулю 2, либо 2p) содержимое второй p-разрядной ячейки информационного регистра (либо 0, если m= 1,2) к полученной сумме прибавляют (например, по модулю 2, либо 2p) содержимое очередной p-разрядной ячейки ключевого регистра, результат преобразуют блоком p-разрядного функционального преобразования f, к полученному результату прибавляют (например, по модулю 2, либо 2p) содержимое r-й (3≅r≅m-1) ячейки информационного регистра (либо 0, если m=1, 2, 3) полученную сумму преобразуют блоком p-разрядного функционального преобразования q, к результату прибавляют (например, по модулю 2, либо 2p) содержимое первой p-разрядной ячейки информационного регистра, вновь полученную сумму преобразуют блоком p-разрядного функционального преобразования h и результат преобразования записывают в m-ю p-разрядную ячейку информационного регистра, содержимое которого предварительно сдвигают на p разрядов в сторону младших разрядов с потерей p младших разрядов.

Прибавление нуля к p-разрядному числу не изменяет это число и поэтому равносильно отсутствию операции прибавления.

Среди функциональных преобразований f, q, h могут быть тождественные, то есть, не изменяющие преобразуемое p-разрядное число. Использование тождественного функционального преобразования равносильно фактическому отсутствию данного преобразования.

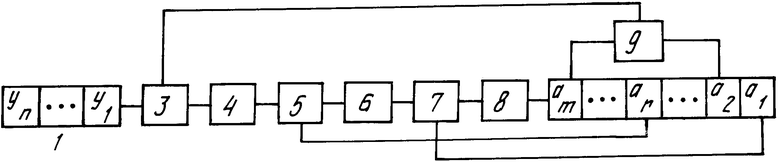

На чертеже представлена блок-схема устройства шифрования двоичной информации.

Устройство шифрования двоичной информации содержит np-разрядный ключевой регистр 1, mp-разрядный информационный регистр 2, первый p-разрядный сумматор 3, блок 4 p-разрядного функционального преобразования f, второй p-разрядный сумматор 5, блок 6 p-разрядного функционального преобразования q, третий p-разрядный сумматор 7, блок 8 p-разрядного преобразования h, четвертый p-разрядный сумматор 9.

Сумматор, в котором задействован только один вход не изменяет информацию, поступающую на этот вход. Это равносильно отсутствию данного сумматора. Поэтому при m=3 фактически отсутствуют третий сумматор 5, при m=2 отсутствуют два сумматора, третий сумматор 5 и первый сумматор 9, а при m=1 отсутствуют целых три сумматора 3, 5, 9.

Блоки 4, 6, 8 могут реализовать любые p-разрядные функциональные преобразования f, q, h в том числе, и тождественные, не изменяющие поступающие на их вход p-разрядные числа. Этот случай равносилен отсутствию данного блока функционального преобразования. Поэтому из трех блоков 4, 6 и 8 p-разрядных функциональных преобразований f, q, h фактически может присутствовать лишь два блока и даже один.

Содержимое np-разрядного ключевого регистра 1 можно формировать из tp-битного ключа при t<n, например, повторным использованием p-битных частей ключа.

Устройство шифрования двоичной информации работает следующим образом.

При m=1 p бит исходной информации записывают в p-разрядный информационный регистр 2. Устройство шифрования работает в n циклов, после которых содержимое p-разрядного информационного регистра 2 является результирующей информацией. Все циклы работы устройства шифрования идентичны. В i-й цикл, I≅i≅n содержимое i-й p-разрядной ячейки ключевого регистра 1 преобразуют блоками 4 и 6 функциональных преобразований f, q к результату прибавляют содержимое p-разрядного информационного регистра 2, полученную сумму преобразуют блоком 8 функционального преобразования h и результат записывают в p-разрядный информационный регистр 2.

Если содержимое p-разрядного информационного регистра 2 в i-й цикл обозначить через a(i), то в i+1 цикл содержимое p-разрядного информационного регистра 2 станет:

a(i+1)=h(q(f(y))+a(i))

где + сложение, например, по модулю 2, либо 2p

a(i)(-{0,1.2p-1)} i≥I.

При m=2 2p бит исходной информации записывают в 2p-разрядный информационный регистр 2. Устройство шифрования работает n циклов, после которых содержимое 2p-разрядного информационного регистра 2 является результирующей информацией. Все циклы работы устройства шифрования идентичны. В i-й цикл 1≅i≅n, к содержимому второй p-разрядной ячейки 2p-разрядного информационного регистра 2 прибавляют содержимое i-й p-разрядной ячейки ключевого регистра 1, сумму преобразуют блоками 4 и 6 функциональных преобразований f, g к результату прибавляют содержимое первой p-разрядной ячейки 2p-рязрядного информационного регистра 2, полученную сумму преобразуют блоком 8 функционального преобразования h и результат записывают на место второй p-разрядной ячейки информационного регистра 2, содержимое которого предварительно сдвигают на p двоичных разрядов в сторону младших разрядов (вправо).

Если содержимое 2p-разрядного информационного регистра 2 в i цикл обозначить через ((a2(i), a1(i)), то в i+1 цикл содержимое 2p-разрядного информационного регистра 2 станет:

a2(i+1)=h(q(f(a2(i)+yi))+a1(i)),

a1(i+1)=a2(i),

где + сложение например, по модулю 2, либо 2p

aj(i)(-{0,1,2p-1)} i, j≥1

При m=3 3p бит исходной информации записывают в 3p-разрядный информационный регистр 2. Устройство шифрования работает n циклов, после которых содержимое 3p-разрядного информационного регистра 2 является результирующей информацией. Все циклы работы устройства шифрования идентичны. В i-й цикл, 1≅i≅n к сумме содержимых второй и третьей p-разрядных ячеек 3p-разрядного информационного регистра 2 прибавляют содержимое i-й p-рязрядной ячейки ключевого регистра 1, сумму, преобразуемую блоками 4 и 8 функциональных преобразований f и g к результату прибавляют содержимое первой p-разрядной ячейки информационного регистра 2, полученную сумму преобразуют блоком 8 функционального преобразования h и результат записывают на место третьей p-разрядной ячейки информационного регистра 2, содержимое которого предварительно сдвигают на p разрядов в сторону младших разрядов (вправо).

Если содержимое 3p-разрядного информационного регистра 2 в i-й цикл обозначить через (a3(i), a2(i), a1(i) то в i+1 цикл содержимое информационного регистра 2 станет:

a3(i+1)=h(q(f(a3(i)+a2(i)+yi))+a1(i)),

a2(i+1)=a3(i),

a1(i+1)=a2(i),

При m≥4 mp бит исходной информации записывают в информационный регистр 2. Устройство шифрования работает в n циклов, после которых содержимое mp-разрядного информационного регистра 2 является результирующей информацией. Все циклы работы устройства шифрования идентичны. В i-й цикл, 1≅i≅n, к сумме содержимых второй и m-й p-разрядных ячеек информационного регистра 2 прибавляют содержимое i p-разрядной ячейки ключевого регистра 1, сумму преобразуют блоком 4 функционального преобразования f, к результату прибавляют содержимое 2-й (3≅r≅m-1) p-разрядной ячейки информационного регистра 2, полученную сумму преобразуют блоком 6 функционального преобразования g, к результату прибавляют содержимое первой p-разрядной ячейки информационного регистра 2, сумму преобразуют блоком 8 функционального преобразования h и результат записывают на место m-й p-разрядной ячейки информационного регистра 2, содержимое которого предварительно сдвигают на p разрядов в сторону младших разрядов (вправо).

В i+1 цикл содержимое mp-разрядного информационного регистра 2 станет:

am(i+1)=h(q(f(am(i) + a2(i) + yi + ar(i)) + a1(i)),

am-1(i+1)=am(i), a1(i+1)=a2(i),

При этом p≅8 функциональные преобразования f, g, h можно реализовать таблично с использованием памяти объема 2pp-разрядных ячеек для каждого преобразования.

При p>8 табличное задание функциональных преобразований f, g, h требует довольно большого, а возможно и непомерного объема памяти. В этом случае p-разрядное функциональное преобразование можно составить из нескольких p'-разрядных преобразований, где p=sp' например, так:

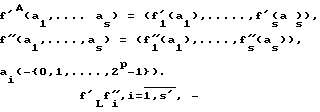

f=f•QATxQBf",

где Tx операция циклического сдвига p-разрядного числа на x=0 разрядов в сторону старших разрядов:

QA(a)=a+A, QB(a)=a+B, a=(a1,as) (-{0, 1,2p-1});

p'-разрядное функциональные преобразования.

То есть, преобразуемое p-разрядное число разбивают на s' p'-разрядных частей, каждую из которых преобразуют соответствующих p'-разрядным преобразованием  к p-разрядному результату преобразований прибавляют (например, по модулю 2p)- p-разрядную константу A, полученную сумму циклически сдвигают на X≥0 разрядов в сторону старших разрядов, снова прибавляют (например, по модулю 2p p-разрядную константу B, полученную p-разрядную сумму разбивают на s' p'-разрядных частей, каждую из которых преобразуют соответствующим p'-разрядных частей, каждую из которых преобразуют соответствующим p'-разрядным преобразованием

к p-разрядному результату преобразований прибавляют (например, по модулю 2p)- p-разрядную константу A, полученную сумму циклически сдвигают на X≥0 разрядов в сторону старших разрядов, снова прибавляют (например, по модулю 2p p-разрядную константу B, полученную p-разрядную сумму разбивают на s' p'-разрядных частей, каждую из которых преобразуют соответствующим p'-разрядных частей, каждую из которых преобразуют соответствующим p'-разрядным преобразованием

Значения s и p' выбираются с учетом доступного объема памяти (s•p'•2p'бит) для реализации результирующего функционального преобразования f.

Если x=0, то операция циклического сдвига фактически отсутствует.

Если A=0, либо B=0, то отсутствует операция прибавления соответствующей константы.

Функции  можно выбрать совпадающими. Выбор тождественных функций равносилен отсутствию этих функций.

можно выбрать совпадающими. Выбор тождественных функций равносилен отсутствию этих функций.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ "АЛБЕР" | 1991 |

|

RU2050697C1 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ "АЛБЕР" | 1991 |

|

RU2024209C1 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ "АЛБЕР" | 1991 |

|

RU2007884C1 |

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2097931C1 |

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2096918C1 |

| СИСТЕМА ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ, СИСТЕМА СИНХРОНИЗАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ШИФРАЦИИ ИЛИ ДЕШИФРАЦИИ ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ | 1996 |

|

RU2099885C1 |

| СПОСОБ ШИФРОВАНИЯ БЛОКОВ ДАННЫХ | 2001 |

|

RU2207736C2 |

| СПОСОБ И УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 1998 |

|

RU2130641C1 |

| СПОСОБ КРИПТОГРАФИЧЕСКОГО ПРЕОБРАЗОВАНИЯ ДВОИЧНЫХ ДАННЫХ | 2001 |

|

RU2226041C2 |

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2004 |

|

RU2262204C1 |

Изобретение относится к области криптографических преобразований и может быть использовано в связных, вычислительных и информационных системах для криптографического закрытия двоичной информации. Технический результат - шифрование информации блоками различной длины с использованием ключа такой длины, которая обеспечивает невозможность его опробования за разумное время. Устройство содержит np-разрядный ключевой регистр 1, mp-разрядный информационный регистр 2, первый, второй, третий и четвертый сумматоры 3, 5, 7, 9, блоки 4, 6, 8 p-разрядных преобразований f, q, h. 3 с.п. ф-лы, 1 ил.

где S, p' ≥ 2, 1 ≅ i ≅ S двух p-разрядных сумматоров, первый из которых прибавляют к поступающему на его вход p-разрядному числу p-разрядную константу A, а второй p-разрядную константу B, и p-разрядного регистра циклического сдвига, причем S p'-разрядных выходов первых S блоков p-разрядных функциональных преобразований

где S, p' ≥ 2, 1 ≅ i ≅ S двух p-разрядных сумматоров, первый из которых прибавляют к поступающему на его вход p-разрядному числу p-разрядную константу A, а второй p-разрядную константу B, и p-разрядного регистра циклического сдвига, причем S p'-разрядных выходов первых S блоков p-разрядных функциональных преобразований  где 1 ≅ i ≅ S подключены к входу первого p-разрядного сумматора, выход которого подключен к p-разрядному входу p-разрядного регистра циклического сдвига, p-разрядный выход которого подключен к входу второго p-разрядного сумматора, p разрядов выхода которого подключены к Sp'-разрядным входам оставшихся S блоков p-разрядных функциональных преобразований

где 1 ≅ i ≅ S подключены к входу первого p-разрядного сумматора, выход которого подключен к p-разрядному входу p-разрядного регистра циклического сдвига, p-разрядный выход которого подключен к входу второго p-разрядного сумматора, p разрядов выхода которого подключены к Sp'-разрядным входам оставшихся S блоков p-разрядных функциональных преобразований  где 1 ≅ i ≅ S.

где 1 ≅ i ≅ S.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сяо Д., Керр Д., Мэдник С | |||

| Защита ЭВМ | |||

| - М.: Мир, 1982, с | |||

| Способ приготовления строительного изолирующего материала | 1923 |

|

SU137A1 |

Авторы

Даты

1997-12-20—Публикация

1994-04-19—Подача