Изобретение относится к криптографическим преобразованиям и может быть использовано в связных, вычислительных и информационных системах для криптографического закрытия двоичной информации.

Известен способ шифрования, предназначенный для криптографической защиты информации в системах связи и вычислительных системах и заключающийся в многократном прибавлении ключа к преобразуемой информации с последующим применением подстановочных и перестановочных преобразований. С использованием этого способа построена система Lucifer фирмы IBM и стандарт шифрования данных Национального бюро стандартов США.

В известном стандарте шифрования данных к содержимому двух 32-разрядных ячеек 64-разрядного информационного регистра 16 раз прибавляют по модулю 2 содержимое 64-разрядного ключевого регистра с последующим воздействием на 32-разрядную сумму 32-разрядным функциональным преобразованием f.

Известный стандарт шифрования данных шифрует информацию блоками по 64 бита, а это при зашифровании требует предварительного накапливания 64 бит информации, а при расшифровании требует дополнительной синхронизации для выделения начала очередного блока зашифрованной информации. Кроме того, процесс зашифрования очередного блока состоит из 16-и циклов, что вносит определенную задержку при зашифровании очередных блоков информации. Перечисленные особенности известного стандарта шифрования данных делают его неудобным при использовании в системах радиосвязи.

Целью настоящего изобретения является обеспечение побитного шифрования информации с использованием ключа необходимого пользователю размера.

Поставленная цель достигается тем, что в способе шифрования двоичной информации, заключающемся в зависящем от 64-разрядного ключа преобразовании 64-разрядного блока шифруемой информации путем 16-кратного выполнения набора операций, включающего сложение 32-разрядных чисел из информационного и ключевого регистра и функциональное преобразование полученной 32-разрядной суммы, на передаче n-разрядные содержимые n-разрядного ключевого регистра и n-разрядного регистра сдвига складывают (например по модулю 2 либо 2n), сумму преобразуют блоком n-разрядного функционального преобразования f, в полученном n-разрядном результате преобразования мажоритарным элементом определяют преобладание нулей или единиц и в зависимости от результата прибавляют по модулю 2 к двоичному знаку шифруемой информации соответственно 0 или 1, полученный в результате зашифрованный двоичный знак направляют в канал связи и на вход n-разрядного регистра сдвига, а на приеме выполняют те же действия, что и на передаче, за исключением того, что на вход n-разрядного регистра сдвига направляют пришедший из канала связи зашифрованный двоичный знак, к которому одновременно прибавляют по модулю 2 выработанный мажоритарным элементом двоичный знак и получают знак открытой информации. Чтобы мажоритарный элемент однозначно реагировал на поступающее на его вход число, разрядность числа n выбирается нечетной.

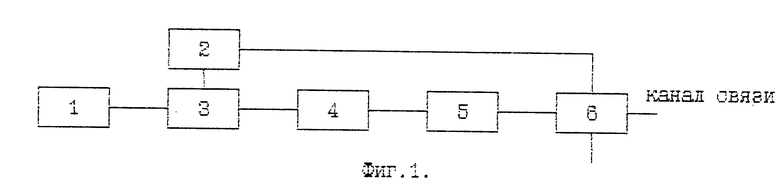

На фиг. 1 и 2 представлены соответственно блок-схемы устройств зашифрования и расшифрования для осуществления способа шифрования двоичной информации.

Устройства зашифования и расшифрования сдержат n-разрядный ключевой регистр 1, n-разрядный регистр сдвига 2, n-разрядный сумматор 3, блок n-разрядного функционального преобразования 4, мажоритарный элемент 5 и одноразрядный сумматор 6.

Процесс зашифрования бита открытой информации осуществляют следующим образом.

n-Разрядные содержимые n-разрядного ключевого регистра 1 и n-разрядного регистра сдвига 2 складывают (например по модулю 2 либо 2n) в n-разрядном сумматоре 3, полученную сумму преобразуют блоком 4 n-разрядного функционального преобразования f, мажоритарным элементом 5 определяют количество единиц в n-разрядном результате преобразования. Если единиц больше, чем нулей, то в одноразрядном сумматоре 6 к двоичному знаку открытой информации прибавляют 1, в противном случае 0. Полученный в результате суммирования двоичный знак зашифрованной информации направляют в канал связи и на вход n-разрядного регистра сдвига 2, содержимое которого предварительно сдвигают на один разряд в сторону младших разрядов с потерей выдвинутого самого младшего разряда.

Процесс расшифрования бита зашифрованной информации осуществляют следующим образом.

n-Разрядные содержимые n-разрядного ключевого регистра 1 и n-разрядного регистра сдвига 2 складывают в n-разрядном сумматоре 3, полученную сумму преобразуют блоком 4 n-разрядного функционального преобразования f, мажоритарным элементом 5 определяют количество единиц в n-разрядном результате преобразования. Если единиц больше, чем нулей, то в одноразрядном сумматоре 6 к пришедшему из канала связи знаку зашифрованной информации прибавляют 1, в противном случае 0. В результате суммирования получают двоичный знак открытой информации. Пришедший из канала связи знак зашифрованной информации одновременно направляют на вход n-разрядного регистра сдвига 2, содержимое которого предварительно сдвигают на один разряд в сторону младших разрядов с потерей выдвинутого самого младшего разряда.

Если в i-й момент n-разрядный ключевой регистр 1 содержит n-разрядное число k(i) (k1(i),kn(i)), kj(i) 0,1, 1≅j≅n, i≥1, то в i-й момент мажоритарный элемент выработает двоичный знак γ(i) = M(f(a(i)+k(i)) где M(a)=0, если  1, если

1, если  }

}  количество единиц в n-разрядном двоичном числе а.

количество единиц в n-разрядном двоичном числе а.

Если o(i) i-й двоичный знак открытой информации, ш (i) i-й двоичный знак зашифрованной информации, то ш(i) = o(i)⊕γ(i) на передаче и o(i) = ш(i)⊕γ(i) на приеме.

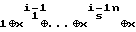

Содержимое n-разрядного регистра сдвига 2 в (i+1)-й момент станет c(i + 1)(c1(i + 1)=c2(i),cn-1(i + 1)=cn(i + 1)=ш(i)).

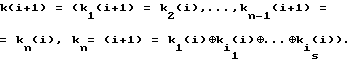

Содержимое n-разрядного ключевого регистра 1 от такта к такту можно обновлять, например, при помощи регистра сдвига с линейной функцией в обратной связи. Если характеристический многочлен регистра имеет вид  то в (i + 1)-й момент содержимое n-разрядного ключевого регистра 1 станет

то в (i + 1)-й момент содержимое n-разрядного ключевого регистра 1 станет

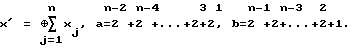

В качестве n-разрядного функционального преобразования f можно выбрать, например, прибавление по модулю 2n к преобразуемому n-разрядному числу x (x1,xn) n-разрядной константы a или n-разрядной константы b в зависимости от четности количества единиц в преобразуемом n-разрядном числе. Тогда f(x) = x+x′a+(x′⊕1)b,

где  р

р

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2096918C1 |

| СИСТЕМА ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ, СИСТЕМА СИНХРОНИЗАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ШИФРАЦИИ ИЛИ ДЕШИФРАЦИИ ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ | 1996 |

|

RU2099885C1 |

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2004 |

|

RU2262204C1 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ "АЛБЕР" | 1991 |

|

RU2024209C1 |

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА - "АЛБЕР" | 1994 |

|

RU2099890C1 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ "АЛБЕР" | 1991 |

|

RU2007884C1 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ "АЛБЕР" | 1991 |

|

RU2050697C1 |

| СПОСОБ ШИФРОВАНИЯ БЛОКОВ ДАННЫХ | 2001 |

|

RU2207736C2 |

| СПОСОБ КРИПТОГРАФИЧЕСКОГО ПРЕОБРАЗОВАНИЯ БЛОКОВ ЦИФРОВЫХ ДАННЫХ | 2007 |

|

RU2359415C2 |

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ | 1992 |

|

RU2032990C1 |

Изобретение относится к криптографическим преобразованиям и может быть использовано в связных, вычислительных и информационных системах для криптографического закрытия двоичной информации. Технический результат - обеспечение побитного шифрования информации с использованием ключа необходимого пользователю размера. Сущность изобретения заключается в многократном прибавлении ключа к преобразуемой информации с последующим применением подстановочных и перестановочных преобразований. Устройство содержит на передаче и приеме п-разрядный ключевой регистр 1, п-разрядный регистр сдвига 2, п-разрядный сумматор 3, блок 4 разрядного функционального преобразования f, мажоритарный элемент 5, однородный сумматор. 2 с. и 2 з.п. ф-лы, 2 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сяо Д., Керр Д., Мэдник С | |||

| Защита ЭВМ | |||

| - М.: Мир, 1982, с.137 - 162. | |||

Авторы

Даты

1997-11-27—Публикация

1995-01-12—Подача