1. Область изобретения

Изобретение касается энергонезависимого полупроводникового запоминающего устройства и, более конкретно, самопрограммирующейся схемы в энергонезависимом полупроводниковом запоминающем устройстве.

Уровень техники

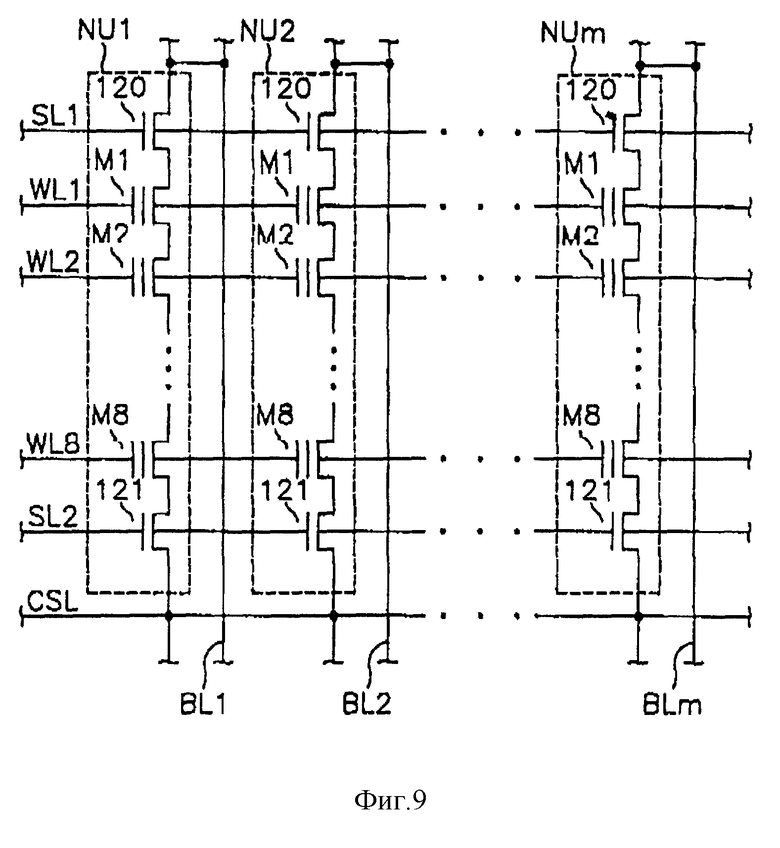

Матрица элементов памяти с логическими NAND (И-НЕ) структурированными элементами имеет множество NAND блоков элементов, организованных в матрицу со столбцами и строками. Фиг. 9 является эквивалентной принципиальной схемой, показывающей часть матрицы элементов памяти со стандартными логическими И-НЕ структурированными элементами. Согласно фигуре каждый из логических элементов И-НЕ множества логических элементов NU1-NUm имеет транзистор первого выделения 120 с его стоком, соединенным с соответствующей битовой шиной, и транзистор второго выделения 121 с его источником, соединенным с шиной общего истока CsL. Стоково-истоковые каналы транзисторов M1 и M2 элементов памяти (далее называемых "элементами памяти") последовательно соединены между истоком транзистора 120 первого выделения и стоком транзистора 121 второго выделения. Затворы транзисторов 120 первого выделения, управляющие затворы элементов памяти M1-M8 и затворы транзисторов 121 второго выделения соединены с шиной первого выделения SL1, числовыми шинами WL1-WL8 и шиной SL2 второго выделения, соответственно. Транзисторы первого и второго выделения 120 и 121 и элементы памяти M1-M8 сформированы в потенциальной яме P-типа, образованной на основной поверхности полупроводниковой подложки. Истоково-стоковая общая область между истоком транзистора 120 первого выделения и стоком элемента памяти M1, истоково-стоковые общие области элементов памяти M1-M8, и стоково-истоковая общая область между стоком транзистора первого выделения 121 и истоком элемента памяти M8 сформированы в потенциальной яме P-типа. Плавающий затвор, сделанный из поликристаллического кремния, образован на каждом канале элементов памяти M1-M8 через туннельный оксидный слой, и плавающий затвор, сделанный из поликремния или из силицида металла с высокой точкой плавления, сформирован через промежуточный изолирующий слой. Стоковые области транзисторов 120 первого выделения, образованные в потенциальной яме P-типа, соответственно соединены с соответствующими разрядными шинами, сделанными из силицида металла с высокой точкой плавления, или сквозными окнами в металле, источковые области транзисторов второго выделения 121, сформированные в потенциальной яме P-типа, соединены с шиной CSL общего источника, сделанной из силицида металла с высокой точкой плавления или из металла. Операцию очистки элементов памяти производят перед программированием, т.е. записью данных.

Операцию очистки элементов памяти производят путем приложения напряжения очистки около 20 В к области потенциальной ямы P-типа, т.е. напряжения заземления к числовым шинам WL1-WL8. С испусканием электронов, имеющихся в плавающих затворах, в область потенциальной ямы P-типа через туннельный оксидный слой элементы памяти преобразуются в транзисторы режима обогащения. Можно предполагать, что очищенные элементы памяти хранят данные "1".

Операция программирования элементов памяти, соединенных с выбранной числовой шиной, т.е. операция записи данных "0", производится путем приложения программирующего напряжения около 18 В к выбранной числовой шине и опорного напряжения, т.е. напряжения заземления Vss к истокам и стокам элементов памяти, в которых записаны данные "0". Затем плавающие затворы элементов памяти, которые будут запрограммированы, аккумулируют электроны через туннельные оксидные слои, и эти элементы памяти преобразуются в транзисторы режима обеднения.

После программирования производится операция верификации программы для проверки того, успешно ли запрограммированы выбранные элементы памяти для того, чтобы иметь заданное постоянное значение порогового напряжения. Эти способы очистки, программирования и верификации программы раскрыты в Корейской патентной заявке N 94 - 18870, опубликованной 19 августа 1994 года и принадлежащей настоящему заявителю.

Поскольку емкость ЭППЗУ стала высоко интегрируемой, размеры элемента памяти, такие как ширина и толщина оксидного слоя затвора и ширина и длина области канала, уменьшились. Однако изменчивость процесса изготовления не может гарантировать однородность ширины и толщины оксидного слоя затвора, промежуточного изолирующего слоя и области канала. Это делает величины порогового напряжения запрограммированных элементов памяти неравными. Если по меньшей мере один из запрограммированных элементов памяти не достигает желаемого порогового напряжения, то выводятся данные об ошибке. Чтобы решить эту проблему, было предложено устройство верификации программы для проверки того, успешно ли запрограммированы выбранные элементы памяти. Например, такой способ верификации программы раскрыт в вышеупомянутой Корейской патентной заявке N 94 - 18870. Однако, так как операция перепрограммирования производится после операции верификации программы с программирующим напряжением постоянного уровня, пороговые напряжения запрограммированных элементов памяти все еще не равны. Изменчивость окружающих условий, таких как напряжение источника питания или рабочая температура, может ухудшить надежность ЭППЗУ.

Краткое изложение существа изобретения

Таким образом, целью данного изобретения является обеспечение энергонезависимого полупроводникового запоминающего устройства, способного поддерживать однородное пороговое напряжение программируемых элементов памяти независимо от изменчивости рабочей температуры и напряжения источника питания.

Другой целью данного изобретения является обеспечение энергонезависимого полупроводникового запоминающего устройства, способного повысить свою надежность независимо от изменчивости процесса.

Для достижения вышеупомянутых целей данного изобретения самопрограммирующийся генератор напряжения энергонезависимого полупроводникового запоминающего устройства, имеющего множество элементов памяти с плавающим затвором, программную схему для программирования выбранных элементов памяти и схему верификации программы для проверки того, успешно запрограммированы выбранные элементы памяти или нет, содержит генератор высокого напряжение для генерации программирующего напряжения, схему подстройки для детектирования уровня программирующего напряжения таким образом, чтобы последовательно увеличивать программирующее напряжение в пределах заданного диапазона напряжений каждый раз, когда выбранные элементы памяти не запрограммированы успешно, сравнивающую схему для сравнения обнаруживаемого уровня напряжения с опорным напряжением и последующей генерации сравнивающего сигнала и схему управления генерацией высокого напряжения для активации генератора высокого напряжения в ответ на опорный сигнал.

Краткое описание чертежей

Сущность изобретения иллюстрируется ссылкой на сопроводительные чертежи, в которых:

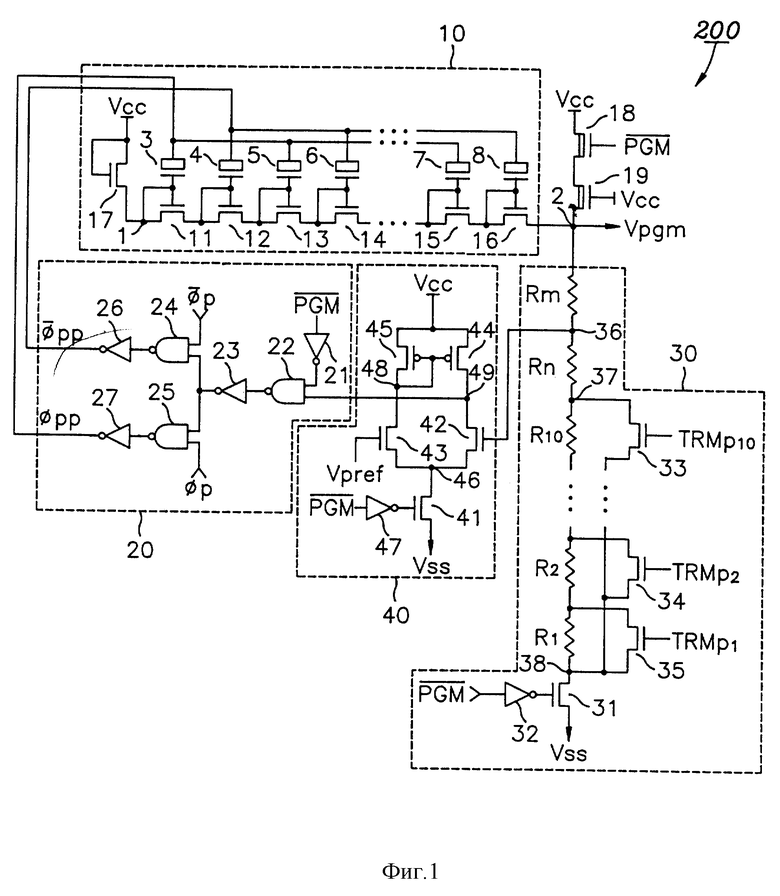

фиг. 1 является схемой, иллюстрирующей генератор программирующего напряжения согласно предпочтительному варианту данного изобретения;

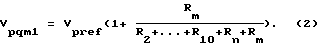

фиг. 2 является схемой, иллюстрирующей генератор сигнала подстройки согласно предпочтительному варианту данного изобретения;

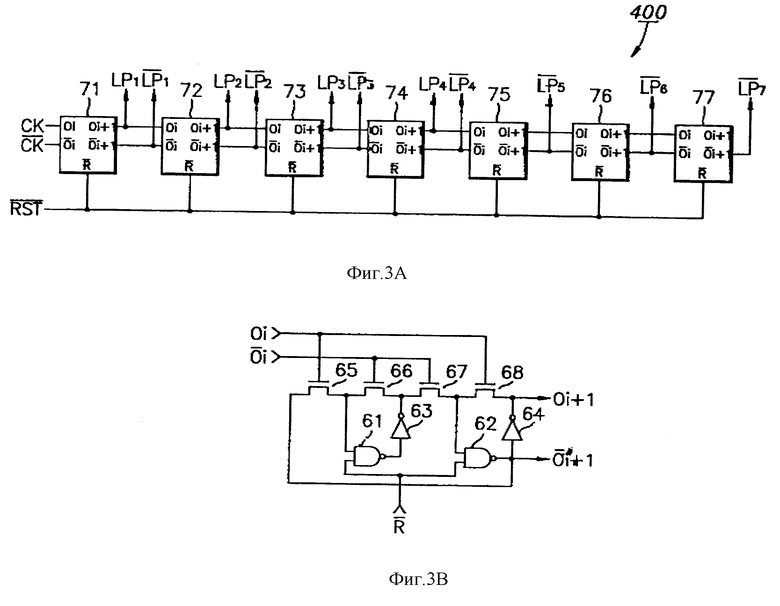

фиг. 3A является схемой, иллюстрирующей двоичный счетчик согласно предпочтительному варианту данного изобретения;

фиг. 3B является схемой, иллюстрирующей каждую стадию в двоичном счетчике фиг. 3A;

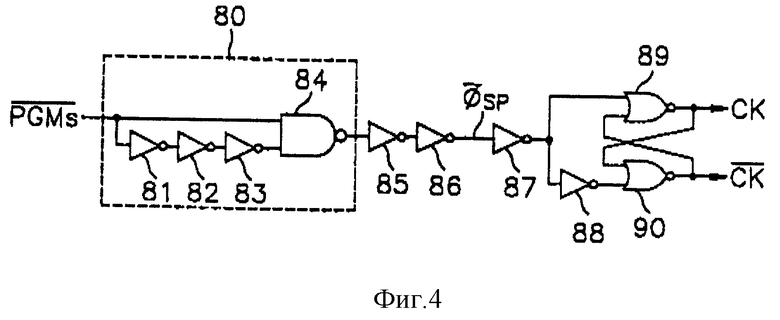

фиг. 4 иллюстрирует генератор синхросигнала для генерации синхросигнала для запуска двоичного счетчика фиг. 3A;

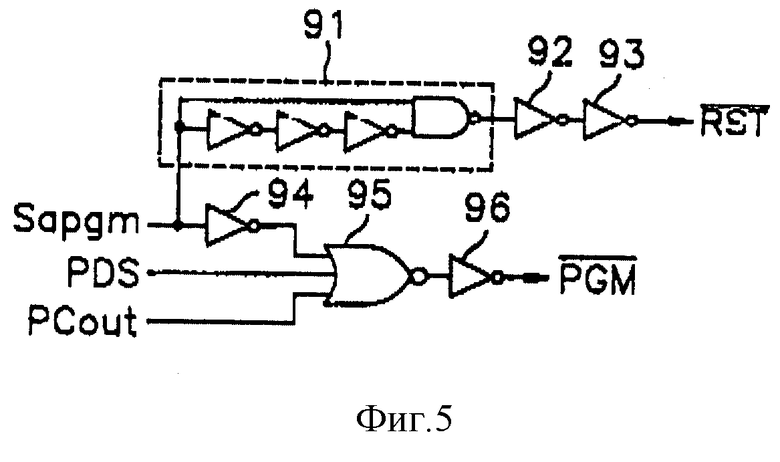

фиг. 5 является схемой, иллюстрирующей генератор сигнала управления согласно предпочтительному варианту данного изобретения;

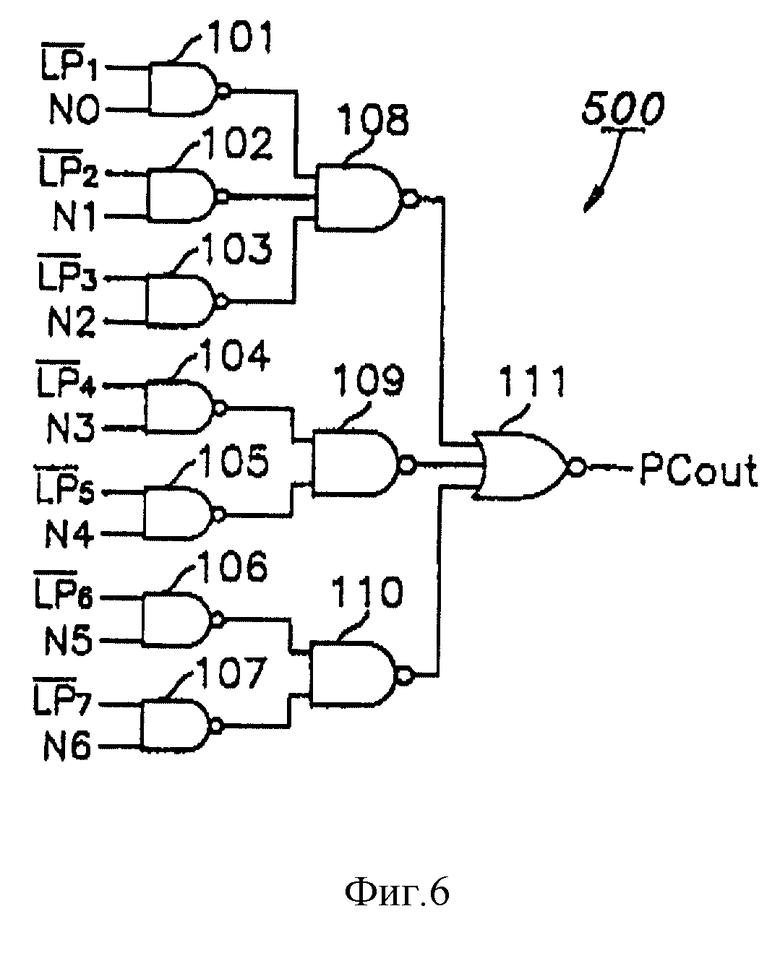

фиг. 6 является схемой, иллюстрирующей счетчик циклов согласно предпочтительному варианту данного изобретения;

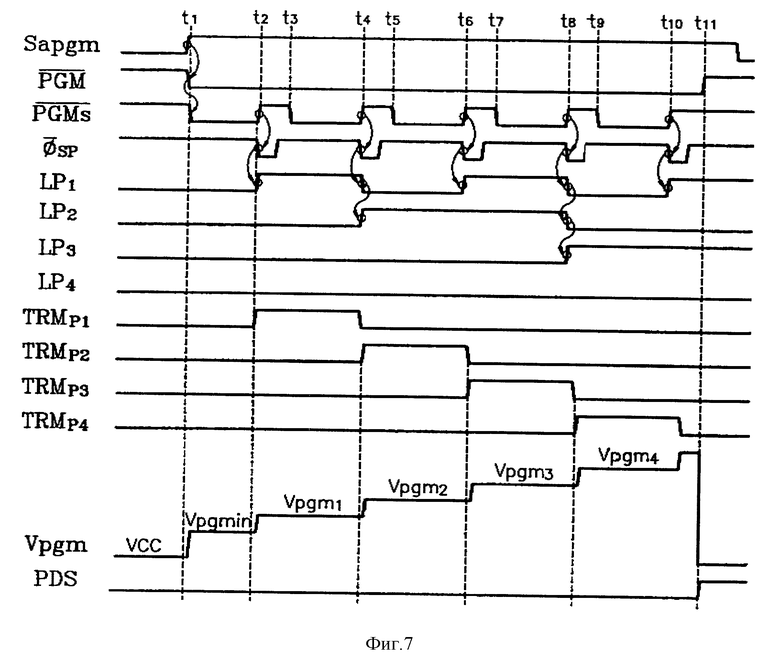

фиг. 7 является временной диаграммой, показывающей работу каждой части схем, связанных с генератором программирующего напряжения, согласно предпочтительному варианту данного изобретения;

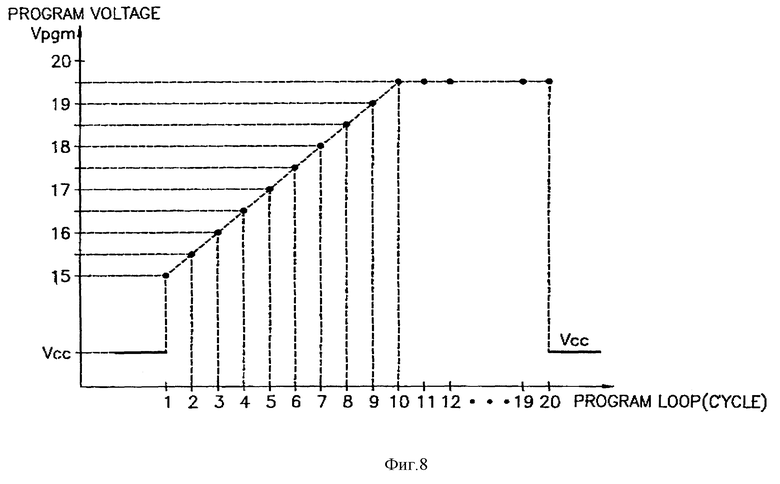

фиг. 8 является схемой, показывающей связь между циклом программы и программирующим напряжением согласно предпочтительному варианту данного изобретения;

фиг. 9 является эквивалентной схемой цепи, показывающей часть матрицы элементов памяти со стандартными NAND структурированными элементами памяти;

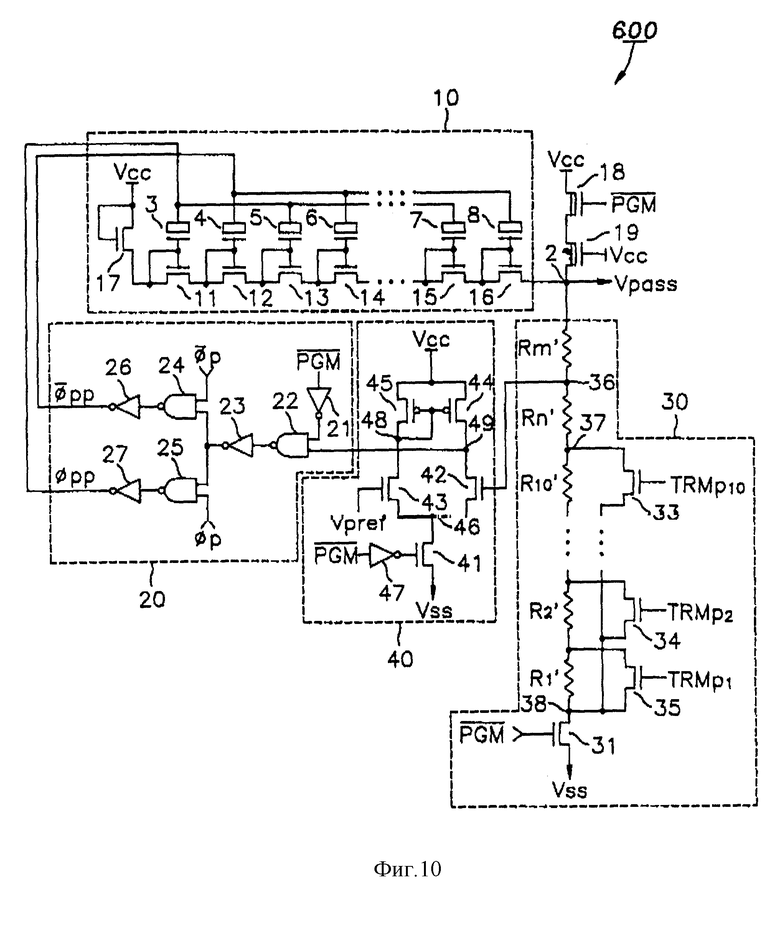

фиг. 10 является схематической диаграммой цепи, показывающей генератор проходного напряжения согласно предпочтительному варианту данного изобретения;

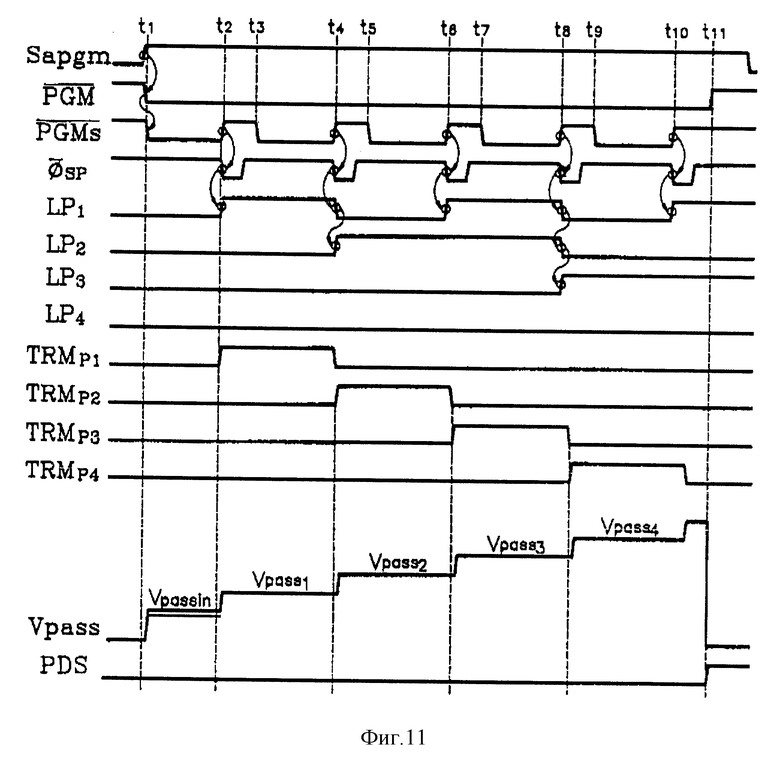

фиг. 11 является временной диаграммой, показывающей работу каждой части схем, связанных с генератором проходного напряжения, согласно предпочтительному варианту данного изобретения, и

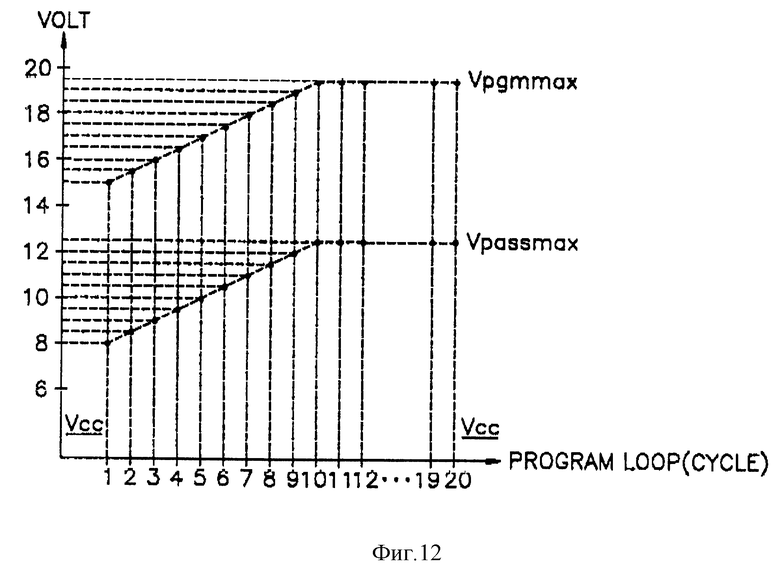

фиг. 12 является схемой, показывающей связь между циклом программы и программирующим напряжением и проходным напряжением, согласно предпочтительному варианту данного изобретения.

Подробное описание предпочтительного варианта

В данном изобретении применяются N- канальные транзисторы с режимом обеднения /далее называемые "транзисторами D-типа"/ имеющие пороговое напряжение - 1,8 В, N-канальные МОП-транзисторы с режимом обогащения/ далее называемые "транзисторами N-типа"/, имеющие пороговое напряжение 0,7 В и F - канальные МОП - транзисторы /далее называемые "транзисторами P-типа"/, имеющие пороговое напряжение - 0,9 В.

Фиг. 1 показывает генератор программирующего напряжения 200. На этой фигуре генератор высокого напряжения 10 генерирует программирующее напряжение Vpgm в ответ на сигнал перекачки заряда Фpр и его дополняющий сигнал  полученный от схемы управления генерацией высокого напряжения 20. Генератор высокого напряжения 10 является хорошо известной схемой для генерации программирующего напряжения Vpgm более высокого, чем напряжение источника питания Vcc, полученного путем использования способа перекачки заряда. Генератор высокого напряжения 10 содержит транзистор 17 N-типа для получения первоначального напряжения Vcc-Vth к узлу 1, транзисторы N-типа 11-16, имеющие свои собственные каналы, последовательно соединенные между общим выводом 1 и общим выводом 2, и МОП-конденсаторы - 3-8, соответственно соединенные с затворами транзисторов N-типа 11-16. Затворы транзисторов N-типа 11-16 соответственно соединены с их стоками, и стоково-истоковые общие узлы нечетных МОП-конденсаторов 3, 5 и 7 и стоково-истоковые общие узлы четных МОП-конденсаторов 4, 6 и 8 соединены с сигналом перекачки заряда Фрр и его дополняющим сигналом

полученный от схемы управления генерацией высокого напряжения 20. Генератор высокого напряжения 10 является хорошо известной схемой для генерации программирующего напряжения Vpgm более высокого, чем напряжение источника питания Vcc, полученного путем использования способа перекачки заряда. Генератор высокого напряжения 10 содержит транзистор 17 N-типа для получения первоначального напряжения Vcc-Vth к узлу 1, транзисторы N-типа 11-16, имеющие свои собственные каналы, последовательно соединенные между общим выводом 1 и общим выводом 2, и МОП-конденсаторы - 3-8, соответственно соединенные с затворами транзисторов N-типа 11-16. Затворы транзисторов N-типа 11-16 соответственно соединены с их стоками, и стоково-истоковые общие узлы нечетных МОП-конденсаторов 3, 5 и 7 и стоково-истоковые общие узлы четных МОП-конденсаторов 4, 6 и 8 соединены с сигналом перекачки заряда Фрр и его дополняющим сигналом  соответственно.

соответственно.

Каналы транзисторов D-типа 18 и 19 последовательно соединены между узлом выхода 2 генератора высокого напряжения 10 и напряжения источника питания Vcc, и их затворы соответственно соединены с программным сигналом управления  и напряжением источника питания Vcc. При завершении работы программы транзистора D-типа 18 и 19 разрежают программирующее напряжение Vpgm до напряжения источника питания Vcc.

и напряжением источника питания Vcc. При завершении работы программы транзистора D-типа 18 и 19 разрежают программирующее напряжение Vpgm до напряжения источника питания Vcc.

Схема подстройки 30 для последовательного увеличения программирующего напряжения Vpgm во время работы программы соединена с выводом выхода 2. Между напряжением заземления Vss и узлом выхода 2 подсоединена схема подстройки 30, в которой канал транзистора N-типа 31 и резисторы R1-R10, Rn-Rm соединены последовательно один с другим, и затвор транзистора N-типа 31 соединен с программным сигналом управления  через инвертор 32. Узел соединения 37 между резисторами Rn и R10 соединен с выводом соединения 38 между резистором R1 и стоком транзистора N-типа 31 через канал транзистора N-типа 33. Выводы соединения между резисторами R10-R1 соответственно соединены с выводом соединения 38 через каналы транзисторов 34 и 35. Затворы транзисторов 33-35 соответственно соединены с сигналом подстройки TRMp10-TRMp1. Транзисторы 33-35 являются шунтирующим средством для обхода последовательно резисторов R1-R10.

через инвертор 32. Узел соединения 37 между резисторами Rn и R10 соединен с выводом соединения 38 между резистором R1 и стоком транзистора N-типа 31 через канал транзистора N-типа 33. Выводы соединения между резисторами R10-R1 соответственно соединены с выводом соединения 38 через каналы транзисторов 34 и 35. Затворы транзисторов 33-35 соответственно соединены с сигналом подстройки TRMp10-TRMp1. Транзисторы 33-35 являются шунтирующим средством для обхода последовательно резисторов R1-R10.

Схема сравнения 40 сравнивает опорное напряжение Vpref с напряжением V36 узла соединения 36 между резисторами Rm и Rn. В схеме сравнения 40 канал транзистора 41 соединен между напряжением заземления Vss и общим выводом 46, а его затвор соединен с программным сигналом управления  через инвертор 47. Первая ветвь, в которой каналы транзистора P-типа 44 и транзистора N-типа 42 соединены последовательно, и вторая ветвь, в которой каналы транзистора P-типа 45 и транзистора N-типа 43 соединены последовательно, соединены параллельно между напряжением источника питания Vcc и общим узлом 46. Затворы транзисторов P-типа 44 и 45 соединены вместе друг с другом и также соединены с выводом соединения 48 между транзистором P-типа 45 и транзистором N-типа 43. Опорное напряжение Vpref, т.е. около 1,67 В, приложено к затвору транзистора N-типа 43. Затвор транзистора N-типа 42 соединен с общим узлом 36. Узел соединения 49 между транзистором P-типа 44 и транзистором N-типа 42 служит выходным выводом схемы сравнения 40. Схема сравнения 40 выводит логическое состояние "низкий", если напряжение V36 больше опорного напряжения Vpref, и выводит логическое состояние "высокий", если V36 < Vpref.

через инвертор 47. Первая ветвь, в которой каналы транзистора P-типа 44 и транзистора N-типа 42 соединены последовательно, и вторая ветвь, в которой каналы транзистора P-типа 45 и транзистора N-типа 43 соединены последовательно, соединены параллельно между напряжением источника питания Vcc и общим узлом 46. Затворы транзисторов P-типа 44 и 45 соединены вместе друг с другом и также соединены с выводом соединения 48 между транзистором P-типа 45 и транзистором N-типа 43. Опорное напряжение Vpref, т.е. около 1,67 В, приложено к затвору транзистора N-типа 43. Затвор транзистора N-типа 42 соединен с общим узлом 36. Узел соединения 49 между транзистором P-типа 44 и транзистором N-типа 42 служит выходным выводом схемы сравнения 40. Схема сравнения 40 выводит логическое состояние "низкий", если напряжение V36 больше опорного напряжения Vpref, и выводит логическое состояние "высокий", если V36 < Vpref.

Схема управления генерацией высокого напряжения 20 соединена между схемой сравнения 40 и генератором высокого напряжения 10 и управляет программирующим напряжением Vpgm для поддержания заданного постоянного уровня напряжения. Схема управления генерацией высокого напряжения 20 содержит логический элемент И-НЕ 22, имеющий один вход, соединенный с узлом соединения 46, и другой, соединенный с программным сигналом управления  через инвертор 21. Первые входы логических элементов И-НЕ 24 и 25 получают выход логического элемента И-НЕ 22 через инвертор 23, а вторые входы соответственно получают синхроимпульсы

через инвертор 21. Первые входы логических элементов И-НЕ 24 и 25 получают выход логического элемента И-НЕ 22 через инвертор 23, а вторые входы соответственно получают синхроимпульсы  и Фp от кольцевого генератора (не показано). В это время синхроимпульсы

и Фp от кольцевого генератора (не показано). В это время синхроимпульсы  и Фр имеют частоту около 8 МГц. Логические элементы И-НЕ 24 и 25 выдают сигналы перекачки заряда

и Фр имеют частоту около 8 МГц. Логические элементы И-НЕ 24 и 25 выдают сигналы перекачки заряда  и Фрр через инверторы 26 и 27.

и Фрр через инверторы 26 и 27.

Если V36 > Vpref, то схема управления генерацией высокого напряжения 20 инактивирована, а если V36 < Vpref, то она становится активированной. Таким образом, если программирующее напряжение Vpgm возрастает, то напряжение V36 также возрастает. Поэтому схема управления генерацией высокого напряжения 20 не активируется, и, таким образом, генератор высокого напряжения 10 уменьшает программирующее напряжение Vpgm. С другой стороны, если программирующее напряжение Vpgm уменьшается, то генератор высокого напряжения 10 увеличивает программирующее напряжение Vpgm. Следовательно, программирующее напряжение Vpgm поддерживает постоянный уровень напряжения путем управления схемой управления генерацией высокого напряжения 20.

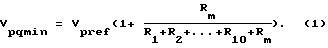

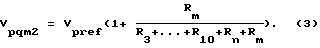

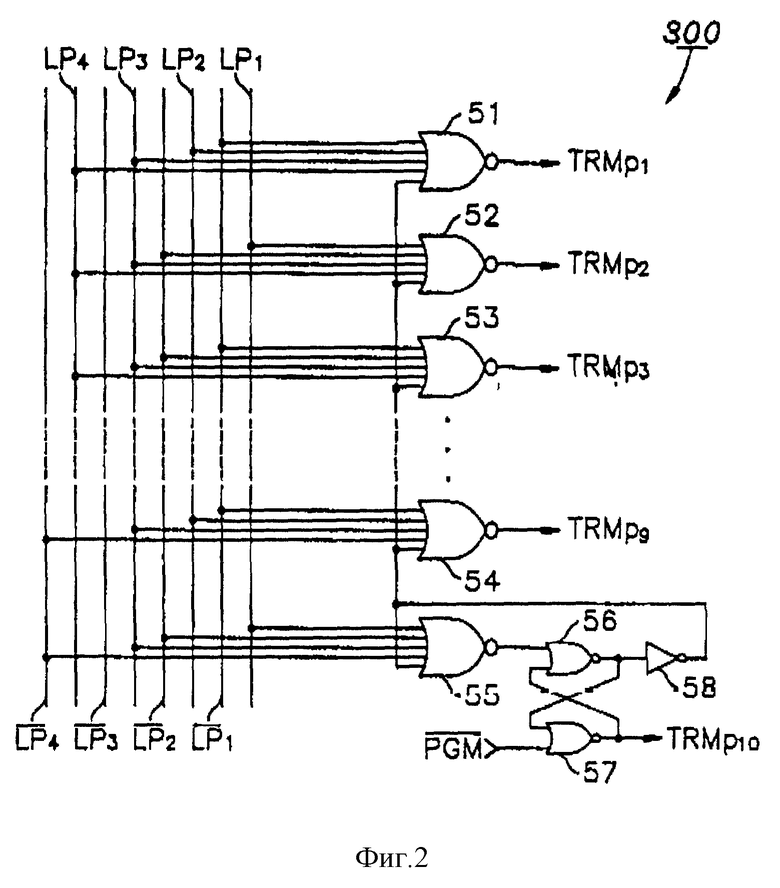

В выключенном состоянии транзисторов 33-35 первоначальное программирующее напряжение Vpgmin на узле выхода 2 может быть представлено следующим образом:

Во включенном состоянии транзистора 35 программирующее напряжение Vpgm1 на узле выхода можно представить следующим образом:

Во включенном состоянии транзистора 34 программирующее напряжение Vpgm1 на узле выхода 2 можно представить следующим образом:

Как можно видеть из вышеприведенных уравнений, при последовательном включении транзисторов 35-33 программирующее напряжение на выводе выхода 2 последовательно возрастает. Таким образом, путем последовательного выполнения программы и операций верификации программы с увеличением программирующего напряжения последовательно в пределах заданного диапазона напряжения, т.е. от 15 до 19,5 B, могут быть обеспечены элементами памяти, имеющими постоянные пороговые напряжения, независимо от различных изменений, таких как изменение процесса и изменение окружающих условий.

Фиг. 2 показывает генератор сигналов подстройки 300 для генерации сигналов подстройки, которые последовательно увеличивают программирующее напряжение pgm с последовательным включением транзисторов 35 - 33 в фиг. 1. Генератор сигналов подстройки 300 имеет множество логических элементов ИЛИ-НЕ 51-55, которые получают комбинации выходных сигналов LP1-LP4, двоичного счетчика и их дополняющих сигналов

Выход логического элемента ИЛИ-НЕ 55 связан с одним входом элемента ИЛИ-НЕ 56 в триггере. Выход логического элемента 56 приложен к логическим элементам ИЛИ-НЕ 51-55 через инвертор 58, а также к одному входу логического элемента 57. Другой выход логического элемента ИЛИ-НЕ 57 в триггере связан с программным сигналом управления  и его вход соединен с сигналом подстройки IRMp10, а также с другим входом логического элемента ИЛИ-НЕ 56. Во время операции программирования триггер, составленный из логических элементов 56 и 57, фиксирует сигнал подстройки IRMp10 в логическое состояние "высокий", если выбран элемент ИЛИ-НЕ 55, т.е. элемент ИЛИ-НЕ выдает логическое состояние "высокий". Инвертор 58 обеспечивает выход элемента ИЛИ-НЕ 56 как сигнал обратной связи. Таким образом, логические элементы 56 и 57 и инвертор 58 являются фиксирующим средством для фиксации сигналов подстройки TRMp1+TRMp10 в логическом состоянии "низкий". Поэтому, если выбранный элемент памяти не является успешно запрограммированным даже после завершения десятой операции верификации программы, то операции программирования поддерживают повышенный уровень максимума программирующего напряжения Vpgmmax, т.е. 19,5 В, согласно предпочтительному варианту данного изобретения. Поскольку максимальное программирующее напряжение Vppgmmax выбирают как величину, способную помешать разрыву соединения и разрыву оксидного слоя затвора элемента памяти, следует отметить, что данное изобретение не ограничивается максимальным уровнем программирующего напряжения 19,5 В. Кроме того, данное изобретение использует 10 сигналов подстройки, однако оно также не ограничено этим. Однако желательно, чтобы программирующее напряжение V, увеличиваемое в каждой операции программирования, было ниже 1 В, предпочтительно, ниже 0,5 В.

и его вход соединен с сигналом подстройки IRMp10, а также с другим входом логического элемента ИЛИ-НЕ 56. Во время операции программирования триггер, составленный из логических элементов 56 и 57, фиксирует сигнал подстройки IRMp10 в логическое состояние "высокий", если выбран элемент ИЛИ-НЕ 55, т.е. элемент ИЛИ-НЕ выдает логическое состояние "высокий". Инвертор 58 обеспечивает выход элемента ИЛИ-НЕ 56 как сигнал обратной связи. Таким образом, логические элементы 56 и 57 и инвертор 58 являются фиксирующим средством для фиксации сигналов подстройки TRMp1+TRMp10 в логическом состоянии "низкий". Поэтому, если выбранный элемент памяти не является успешно запрограммированным даже после завершения десятой операции верификации программы, то операции программирования поддерживают повышенный уровень максимума программирующего напряжения Vpgmmax, т.е. 19,5 В, согласно предпочтительному варианту данного изобретения. Поскольку максимальное программирующее напряжение Vppgmmax выбирают как величину, способную помешать разрыву соединения и разрыву оксидного слоя затвора элемента памяти, следует отметить, что данное изобретение не ограничивается максимальным уровнем программирующего напряжения 19,5 В. Кроме того, данное изобретение использует 10 сигналов подстройки, однако оно также не ограничено этим. Однако желательно, чтобы программирующее напряжение V, увеличиваемое в каждой операции программирования, было ниже 1 В, предпочтительно, ниже 0,5 В.

Фиг. 3A показывает двоичный счетчик, а фиг. 3B показывает схематическую диаграмму цепи в каждой стадии двоичного счетчика фиг. 3A.

Как показано на фиг. 3B, каналы транзисторов N-типа 65-68 последовательно соединены между выходными выводом 0; +1 и его дополняющим выходным выводом  +1, затворы транзисторов 66 и 67 совместно соединены с дополняющим выводом входа синхронизации

+1, затворы транзисторов 66 и 67 совместно соединены с дополняющим выводом входа синхронизации  а затворы транзисторов 65 и 68 - с выводом входа синхронизации 0. Инвертор 64 соединен между выходным выводом 0; +1 и его дополняющим выходным выводом

а затворы транзисторов 65 и 68 - с выводом входа синхронизации 0. Инвертор 64 соединен между выходным выводом 0; +1 и его дополняющим выходным выводом  +1, второй вход логического элемента И-НЕ 61 соединен с общим выводом между транзисторами 66 и 67 через инвертор 63. Второй вход логического элемента И-НЕ 62 соединен с общим выводом между транзисторами 67 и 68, а его выход - с дополняющим выходным выводом

+1, второй вход логического элемента И-НЕ 61 соединен с общим выводом между транзисторами 66 и 67 через инвертор 63. Второй вход логического элемента И-НЕ 62 соединен с общим выводом между транзисторами 67 и 68, а его выход - с дополняющим выходным выводом  +1. Таким образом, если сигнал очистки логического состояния "низкий" приложен к выводу очистки

+1. Таким образом, если сигнал очистки логического состояния "низкий" приложен к выводу очистки  то выходной вывод 0; +1 принимает логическое состояние "низкий", а его дополняющий выходной вывод

то выходной вывод 0; +1 принимает логическое состояние "низкий", а его дополняющий выходной вывод  +1 принимает логическое состояние "высокий". Кроме того, каждый раз, когда вход вывода 0 переходит из логического состояния "высокий" в логическое состояние "низкий", выходное состояние выходного вывода 0; +1 изменяется.

+1 принимает логическое состояние "высокий". Кроме того, каждый раз, когда вход вывода 0 переходит из логического состояния "высокий" в логическое состояние "низкий", выходное состояние выходного вывода 0; +1 изменяется.

Двоичный счетчик 400 фиг. 3A составлен из 7 каскадов, последовательно соединенных друг с другом. Вывод очистки R связан с сигналом очистки  и вывод входа синхронизации 0; и его дополняющий вывод входа синхронизации

и вывод входа синхронизации 0; и его дополняющий вывод входа синхронизации  в первом каскаде соответственно соединен с синхросигналом СК и его дополняющим синхросигналом

в первом каскаде соответственно соединен с синхросигналом СК и его дополняющим синхросигналом  7 каскадов 71 - 77 выдают дополняющие сигналы под счета

7 каскадов 71 - 77 выдают дополняющие сигналы под счета  а 4 каскада 71-74 выдают сигналы подсчета LP1-LP4. Каждый раз, когда синхросигнал СК переходит в логическое состояние "низкий", сигналы подсчета LP1-LP4 подсчитываются, и дополняющие сигналы подсчета LP1-LP7 пересчитываются.

а 4 каскада 71-74 выдают сигналы подсчета LP1-LP4. Каждый раз, когда синхросигнал СК переходит в логическое состояние "низкий", сигналы подсчета LP1-LP4 подсчитываются, и дополняющие сигналы подсчета LP1-LP7 пересчитываются.

Фиг. 4 является схемой цепи, показывающей генератор синхросигналов для генерации синхросигнала, который должен быть обеспечен для двоичного счетчика 400 фиг. 3A. На фигуре сигнал программирования и верификации  генерируется от таймера (не показан) в ответ на сигнал управления программы

генерируется от таймера (не показан) в ответ на сигнал управления программы  Генератор синхросигналов содержит генератор коротких импульсов 80, состоящий из инверторов 81-83 и элемента И-НЕ 84, инверторов 85-88 и элементов ИЛИ-НЕ 89 и 90. Логические элементы 89 и 90 заключены в триггере. Генератор коротких импульсов 80 генерирует короткий импульс логического состояния "низкий", когда сигнал программирования и верификации

Генератор синхросигналов содержит генератор коротких импульсов 80, состоящий из инверторов 81-83 и элемента И-НЕ 84, инверторов 85-88 и элементов ИЛИ-НЕ 89 и 90. Логические элементы 89 и 90 заключены в триггере. Генератор коротких импульсов 80 генерирует короткий импульс логического состояния "низкий", когда сигнал программирования и верификации  переходит в логическое состояние "высокий".

переходит в логическое состояние "высокий".

Фиг. 5 является схематической диаграммой цепи генератора сигнала управления для генерации сигнала очистки  и сигнала управления программы

и сигнала управления программы  Генератор сигналов управления фиг. 5 генерирует сигнал очистки

Генератор сигналов управления фиг. 5 генерирует сигнал очистки  через генератор коротких импульсов 91 и инверторы 92 и 93 в ответ на самопрограммирующийся флаг-сигнал Sapgm, выведенный из регистра команд (не показан). Самопрограммирующийся флаг-сигнал Sapgm прикладывают к первому входу логического элемента ИЛИ-НЕ 95 через инвертор 94, сигнал обнаружения программы PDS - к второму его входу и сигнал подсчета циклов PCOut - к его третьему входу.

через генератор коротких импульсов 91 и инверторы 92 и 93 в ответ на самопрограммирующийся флаг-сигнал Sapgm, выведенный из регистра команд (не показан). Самопрограммирующийся флаг-сигнал Sapgm прикладывают к первому входу логического элемента ИЛИ-НЕ 95 через инвертор 94, сигнал обнаружения программы PDS - к второму его входу и сигнал подсчета циклов PCOut - к его третьему входу.

Логический элемент ИЛИ-НЕ 95 выдает сигнал управления программой  через инвертор 96. Сигнал обнаружения программы PDS генерируется согласно операции верификации программы. Если все выбранные элементы памяти были успешно запрограммированы, то сигнал обнаружения программы переходит в логическое состояние "высокий". Напротив, если, по меньшей мере, один из выбранных элементов памяти не был успешно запрограммирован, то сигнал обнаружения программы переходит в логическое состояние "низкий". Такая техника верификации программы раскрыта в вышеупомянутой Корейской патентной заявке N 94-18870.

через инвертор 96. Сигнал обнаружения программы PDS генерируется согласно операции верификации программы. Если все выбранные элементы памяти были успешно запрограммированы, то сигнал обнаружения программы переходит в логическое состояние "высокий". Напротив, если, по меньшей мере, один из выбранных элементов памяти не был успешно запрограммирован, то сигнал обнаружения программы переходит в логическое состояние "низкий". Такая техника верификации программы раскрыта в вышеупомянутой Корейской патентной заявке N 94-18870.

Фиг. 6 показывает схему подсчета циклов 500 для генерации сигнала подсчета циклов PCout. Схема подсчета циклов 500 является логической схемой, составленной из логических элементов И-НЕ 101-110 и логического элемента ИЛИ-НЕ 111. Дополняющие сигналы подсчета  подают из двоичного счетчика 400 к логическим элементам 101-107, соответственно. Выводы NO-N6 соединяются с напряжением заземления Vss или с напряжением источника питания Vcc согласно частоте подсчета циклов. Так как частота подсчета циклов установлена на 20 согласно предпочтительному варианту данного изобретения, выводы N 2 и N 5 соединяются с напряжением источника питания Vcc, а остающиеся выводы N 0, N 1, N 3, N 4 и N 6 соединяются с напряжением заземления Vss.

подают из двоичного счетчика 400 к логическим элементам 101-107, соответственно. Выводы NO-N6 соединяются с напряжением заземления Vss или с напряжением источника питания Vcc согласно частоте подсчета циклов. Так как частота подсчета циклов установлена на 20 согласно предпочтительному варианту данного изобретения, выводы N 2 и N 5 соединяются с напряжением источника питания Vcc, а остающиеся выводы N 0, N 1, N 3, N 4 и N 6 соединяются с напряжением заземления Vss.

Самопрограммирующаяся схема согласно предпочтительному варианту будет описана со ссылкой на временную диаграмму фиг. 7.

Как показано на фиг. 7, операция самопрограммирования начинается в ответ на переход самопрограммирующегося флаг-сигнала Sapgm из логического состояния "низкий" в логическое состояние "высокий". Так как сигнал обнаружения программы PDS и сигнал подсчета циклов PCout находится в логическом состоянии "низкий" в начале операции самопрограммирования, генератор сигнала управления генерирует сигнал управления программой  логического состояния "низкий" в ответ на переход самопрограммирующегося флаг-сигнала Sapgm из логического состояния "низкий" в логическое состояние "высокий".

логического состояния "низкий" в ответ на переход самопрограммирующегося флаг-сигнала Sapgm из логического состояния "низкий" в логическое состояние "высокий".

В дополнение к этому, в ответ на самопрограммирующийся флаг-сигнал Sapgm, который переходит в логическое состояние "высокий", генератор коротких импульсов 91 генерирует короткий импульс логического состояния "низкий", и тем самым двоичный счетчик 400 фиг. 3А очищается. Как показано на фиг. 7, таймер (не показан) генерирует сигнал программирования и верификации  в ответ на переход сигнала управления программой из логического состояния "высокий" в логическое состояние "низкий". Сигнал программирования и верификации

в ответ на переход сигнала управления программой из логического состояния "высокий" в логическое состояние "низкий". Сигнал программирования и верификации  является синхроимпульсом, который имеет логическое состояние "низкий" 30 мксек, и логическое состояние "высокий" 10 мксек, когда сигнал управления программой

является синхроимпульсом, который имеет логическое состояние "низкий" 30 мксек, и логическое состояние "высокий" 10 мксек, когда сигнал управления программой  находится в логическом состоянии "низкий". Длительность, когда сигнал управления программой оставляет логическое состояние "низкий", равна времени операции программирования, а длительность, когда сигнал управления программой оставляет логическое состояние "высокий", равна времени операций верификации программы.

находится в логическом состоянии "низкий". Длительность, когда сигнал управления программой оставляет логическое состояние "низкий", равна времени операции программирования, а длительность, когда сигнал управления программой оставляет логическое состояние "высокий", равна времени операций верификации программы.

В момент времени t1 фиг. 7 в ответ на переход сигнала управления программой  из логического состояния "высокий" в логическое состояние "низкий", генератор программирующего напряжения 200 фиг. 1 задействован. А именно транзистор 41 включен, тем самым активируя схему сравнения 40, и включен транзистор 31, что активирует схему подстройки 30. В начале операции, поскольку Vpref > V36, схема сравнения 40 выводит логическое состояние "высокий". Следовательно, инвертор 23 выводит логическое состояние "высокий", и поэтому схема управления генерацией высокого напряжения 20 генерирует сигнал перекачки заряда Фрр и его дополняющий сигнал

из логического состояния "высокий" в логическое состояние "низкий", генератор программирующего напряжения 200 фиг. 1 задействован. А именно транзистор 41 включен, тем самым активируя схему сравнения 40, и включен транзистор 31, что активирует схему подстройки 30. В начале операции, поскольку Vpref > V36, схема сравнения 40 выводит логическое состояние "высокий". Следовательно, инвертор 23 выводит логическое состояние "высокий", и поэтому схема управления генерацией высокого напряжения 20 генерирует сигнал перекачки заряда Фрр и его дополняющий сигнал  Таким образом, генератор высокого напряжения 10 генерирует постепенно возрастающее высокое напряжение сигналами Фрр и

Таким образом, генератор высокого напряжения 10 генерирует постепенно возрастающее высокое напряжение сигналами Фрр и  Программирующее напряжение Vpgm возрастает, пока напряжение V36 в узле соединения 36 не достигнет опорного напряжения Vpref. Следовательно, программирующее напряжение Vpgm поддерживает первоначальное программирующее напряжение Vpgmin, показанное в вышеприведенном уравнении (1). Технология программирования выбранных элементов памяти программирующим напряжением Vpgm раскрыта в Корейской патентной заявке N 18870.

Программирующее напряжение Vpgm возрастает, пока напряжение V36 в узле соединения 36 не достигнет опорного напряжения Vpref. Следовательно, программирующее напряжение Vpgm поддерживает первоначальное программирующее напряжение Vpgmin, показанное в вышеприведенном уравнении (1). Технология программирования выбранных элементов памяти программирующим напряжением Vpgm раскрыта в Корейской патентной заявке N 18870.

В момент времени t2 сигнал программирования и верификации  переходит в логическое состояние "высокий", и в период между t1 и t2 производится операция верификации программы для запрограммированных элементов памяти. В ответ на сигнал программирования и верификации

переходит в логическое состояние "высокий", и в период между t1 и t2 производится операция верификации программы для запрограммированных элементов памяти. В ответ на сигнал программирования и верификации  который переходит в логическое состояние "высокий" в момент времени t2, генератор коротким импульсом 80 фиг. 4 генерирует короткий импульс, а инвертор 86 генерирует сигнал короткого импульса фsp логического состояния "низкий". Синхросигнал СК - генерируется как сигнал, подобный сигналу короткого импульса фsp. Затем двоичный счетчик 400 фиг. 3А создает сигнал подсчета LP1, равный логическому состоянию "высокий", как показано на фиг. 7. Тем самым NOR затвор 51 фиг. 2 генерирует сигнал подстройки TRMp1, равный логическому состоянию "высокий". Таким образом, с включенным состоянием транзистора 35 фиг. 1 резистор R1 шунтируется, и напряжение V36 в узле соединения 36 становится меньшим, чем опорное напряжение Vpref.

который переходит в логическое состояние "высокий" в момент времени t2, генератор коротким импульсом 80 фиг. 4 генерирует короткий импульс, а инвертор 86 генерирует сигнал короткого импульса фsp логического состояния "низкий". Синхросигнал СК - генерируется как сигнал, подобный сигналу короткого импульса фsp. Затем двоичный счетчик 400 фиг. 3А создает сигнал подсчета LP1, равный логическому состоянию "высокий", как показано на фиг. 7. Тем самым NOR затвор 51 фиг. 2 генерирует сигнал подстройки TRMp1, равный логическому состоянию "высокий". Таким образом, с включенным состоянием транзистора 35 фиг. 1 резистор R1 шунтируется, и напряжение V36 в узле соединения 36 становится меньшим, чем опорное напряжение Vpref.

В результате активируется схема управления генерацией высокого напряжения 20, и генератор высокого напряжения 10 генерирует повышенное программирующее напряжение Vpgm1, как показано в вышеприведенном уравнении (2).

Если выбранные элементы памяти не запрограммированы успешно во время операции верификации программы между моментами времени t2 и t3, т.е. в течение 10 мксек, то автоматически выполняется операция перепрограммирования с повышенным программирующим напряжением Vpgm1 в период времени между t3 и t4.

В момент времени t4 сигнал программирования и верификации  переходит в логическое состояние "высокий", генератор коротких импульсов 80 фиг. 4 генерирует короткий импульс логического состояния "низкий" и инвертор 86 выводит короткий импульс

переходит в логическое состояние "высокий", генератор коротких импульсов 80 фиг. 4 генерирует короткий импульс логического состояния "низкий" и инвертор 86 выводит короткий импульс  логического состояния "низкий", как показано на фиг. 7. Синхросигнал СК становится коротким импульсом логического состояния "низкий", и сигналы подсчета LP1 и LP2 двоичного счетчика 400 становятся логическими состояниями "низкий" и "высокий", соответственно. Таким образом, элемент ИЛИ-НЕ 52 фиг. 2 генерирует сигнал подстройки TRMp2, который переходит в логическое состояние "высокий". В ответ на сигнал подстройки TRMp2 логического состояния "высокий", резисторы R1 и R2 фиг. 1 шунтируются, и напряжение V36 в узле соединения 36 становится меньше, чем опорное напряжение Vpref. Следовательно, активируется схема управления генерацией высокого напряжения 20, и поэтому генератор высокого напряжения 10 генерирует программирующее напряжение Vpgm2, как показано в вышеприведенном уравнении (3).

логического состояния "низкий", как показано на фиг. 7. Синхросигнал СК становится коротким импульсом логического состояния "низкий", и сигналы подсчета LP1 и LP2 двоичного счетчика 400 становятся логическими состояниями "низкий" и "высокий", соответственно. Таким образом, элемент ИЛИ-НЕ 52 фиг. 2 генерирует сигнал подстройки TRMp2, который переходит в логическое состояние "высокий". В ответ на сигнал подстройки TRMp2 логического состояния "высокий", резисторы R1 и R2 фиг. 1 шунтируются, и напряжение V36 в узле соединения 36 становится меньше, чем опорное напряжение Vpref. Следовательно, активируется схема управления генерацией высокого напряжения 20, и поэтому генератор высокого напряжения 10 генерирует программирующее напряжение Vpgm2, как показано в вышеприведенном уравнении (3).

Если выбранные элементы памяти не запрограммированы успешно несмотря на операцию перепрограммирования, то операция программирования производится повторно в период времени между t5 и t6. Подобным образом с последовательным увеличением программирующего напряжения, операция программирования и верификации производится автоматически, пока все выбранные элементы памяти не будут успешно запрограммированы.

Временная диаграмма фиг. 7 показывает случай, когда выбранные элементы памяти успешно запрограммированы при пятой операции программирования. После завершения пятой операции программирования сигнал обнаружения программы PDS, показывающий, что выбранные элементы памяти успешно запрограммированы, переходит в логическое состояние "высокий" при операции верификации программы в период между моментами времени t10 и t11. Тем самым генератор сигнала управления фиг. 5 делает сигнал программирования равным логическому состоянию "высокий", и связанные с программой схемы, подобные кольцевому счетчику /не показано/, не задействованы. После примерно 2,5 мксек после того, как сигнал управления программой  переходит в логическое состояние "высокий", самопрограммирующийся флаг-сигнал Sapgm переходит в логическое состояние "низкий".

переходит в логическое состояние "высокий", самопрограммирующийся флаг-сигнал Sapgm переходит в логическое состояние "низкий".

Можно определить, сколько программных циклов уложилось в 2,5 мксек с дополняющими сигналами подсчета  выведенными из двоичного счетчика 400.

выведенными из двоичного счетчика 400.

Фиг. 8 является схемой, показывающей связь между программным циклом и программирующим напряжением согласно предпочтительному варианту данного изобретения. Согласно фиг. 8, операции программирования для выбранных элементов памяти могут быть выполнены 20 раз. Программирующее напряжение Vpgm последовательно возрастает от 15 В до 19,5 В с шагом 0,5 В до десятой операции программирования. Во время 11-20-й операций программирования программирующее напряжение Vpgm поддерживает максимальный уровень постоянного напряжения Vpgmmax 19,5 В путем операции фиксирования триггера, составленного из логических элементов ИЛИ-НЕ 56 и 57. Если выбранные элементы памяти не являются успешно запрограммированными после 20-й операции программирования, то схема подсчета циклов 500 фиг. 6 генерирует сигнал подсчета циклов PCout, который переходит в логическое состояние "высокий", и поэтому генератор сигналов управления фиг. 5 генерирует сигнал управления программой  который переходит в логическое состояние "высокий", тем самым останавливая генерацию программирующего напряжения Vpgm.

который переходит в логическое состояние "высокий", тем самым останавливая генерацию программирующего напряжения Vpgm.

Как описано выше, самопрограммирующийся генератор напряжения генерирует программирующее напряжение, которое последовательно возрастает в пределах заданного диапазона напряжений в зависимости от программного цикла согласно данному изобретению. Программирующее напряжение подается к выбранной числовой шине. Однако следует предотвратить изменение порогового напряжения и воздействие элементов памяти, которые не следует программировать среди элементов памяти, соединенных с выбранной числовой шиной.

При операции программирования стандартной технологии к невыбранным числовым шинам прикладывается проходное напряжение Vpass, т.е. постоянное напряжение 10 В. Например, предположим, что выбрана числовая шина WL2, тогда максимальное программирующее напряжение Vpqmmax, повышенное согласно циклу программы, т. е. 19,5 В, приложено к выбранной числовой шине WL2, элемент памяти M2 внутри логического элемента И-НЕ множества логических элементов NU2 должен быть запрограммирован как данные "0", и элемент памяти M2 внутри элемента И-НЕ множества логических элементов NV1 должен удерживаться как состояние очистки, т.е. данные "1", напряжение источника питания Vcc5 приложено к шине первого выделения SLI, постоянное проходное напряжение Vpass 10 В приложено к невыбранным числовым шинам WL1 и WL3 -WL8, и напряжение заземления Vss приложено к шине второго выделения SL2 во время операции программирования. В то же время напряжение заземления Vss приложено к разрядной шине BL2, связанной с элементом памяти M2, который должен быть запрограммирован как данные "0" внутри логического элемента И-НЕ множества логических элементов NV2 и напряжение источника питания Vcc 5 В приложено к разрядной шине BL1, связанной с элементом памяти M2, который должен поддерживаться как состояние очистки, т.е. данные "I" внутри логического элемента И-НЕ множества логических элементов NV1. Затем включается транзистор первого выделения 120 внутри логического элемента И-НЕ множества логических элементов NV2, и тем самым элемент памяти M2 внутри логического элемента И-НЕ множества логических элементов NV2 программируется как данные "0". Однако, так как напряжение источника питания Vcc 5 В приложено к разрядной шине BL1, связанной с логическим элементом И-НЕ, блоком элементов NU1 и с затвором транзистора первого выделения 120 внутри И-НЕ множества логических элементов NV1, и проходное напряжение Vpass 10 В приложено к затвору управления элемента памяти M1 внутри И-НЕ множества логических элементов NV1. Исток транзистора первого выделения 120 заряжается проходным напряжением Vpass, и тем самым транзистор первого выделения 120 выключается. Таким образом, исток и сток элемента памяти M2 внутри логического элемента И-НЕ множества логических элементов NV1 заряжаются проходным напряжением Vpass/=10 В/, и повышенное программирующее напряжение 19,5 В резко прилагается к затвору управления элемента памяти M2. Следовательно, элемент памяти M2 внутри логического элемента И-НЕ множества логических элементов NV1 получает воздействие напряжения 9,5 В, и тем самым разрывается тонкий туннельный оксидный слой, обусловленный изменением процесса изготовления, или промежуточный изолирующий слой. Тем временем изменяется пороговое напряжение элемента памяти M2 внутри логического элемента И-НЕ множества логических элементов NV2. Следовательно, приложение постоянного проходного напряжения Vpass к невыбранным числовым шинам ухудшает надежность ЭППЗУ. Чтобы решить эту проблему, предпочтительный вариант данного изобретения будет описан со ссылкой на фиг. 10-12.

Фиг. 10 показывает генератор проходного напряжения для генерирования проходного напряжения, которое должно быть приложено к невыбранным числовым шинам. Согласно фигуре, генератор проходного напряжения 600 имеет такую же структуру, что и генератор программирующего напряжения 200 фиг. 1, за исключением того, что значения резисторов R'1-R10, R'4 и R'm в генераторе проходного напряжения 600 отличаются от значений резисторов R1-R10, Rn и Rm в генераторе программирующего напряжения 200, и что с узла выхода 2 выводится проходное напряжение Vpass вместо программирующего напряжения Vpgm. Для управления генератором проходного напряжения 600 также применяются генераторы сигналов управления, показанные в фиг. 2-6. Генератор проходного напряжения 600 генерирует проходное напряжение Vpass, которое последовательно возрастает от первоначального напряжения Vpassin 8 В до максимального проходного напряжения Vpassmax 12,5 В согласно программному циклу. Генерацию возрастающего проходного напряжения Vpass можно осуществить путем использования правильных значений резисторов R'1-R'10, Rn и Rm. Операции генератора проходного напряжения 600 идентичны операциям генератора программирующего напряжения 200 за исключением значения проходного напряжения Vpass, и они не будут описываться. Генераторы сигналов управления, показанные на фиг. 2-6, используются в генераторе проходного напряжения 600 фиг. 10 и также не будут описываться.

Фиг. 11 является временной диаграммой для описания операций генератора проходного напряжения фиг. 10. Фиг. 11 идентична фиг. 7, за исключением того, что вместо программирующего напряжения Vpgm генерируется проходное напряжение Vpass.

Фиг. 12 является схемой, показывающей связь между программирующим напряжением Vpgm и проходным напряжением Vpass согласно циклу программы. Как можно видеть на фигуре, разность напряжений между программирующим напряжением Vpgm и проходным напряжением Vpass поддерживается равной 5 В до десятой операции программирования. Такая разность напряжений может быть правильно установлена согласно структуре или свойствам элементов памяти для того, чтобы помешать разрыву изоляции или изменению порогового напряжения элементов памяти, которые не должны быть запрограммированы.

Как описано выше, так как самопрограммирующийся генератор напряжений и генератор проходного напряжения согласно данному изобретению генерируют программирующее напряжение и проходное напряжение, которое последовательно возрастает в заданном диапазоне напряжений, надежность микросхемы можно повысить без разрыва изолирующего слоя или изменения порогового напряжения элементов памяти, которые не должны быть запрограммированы. К тому же можно достичь однородных пороговых напряжений и повысить характеристику микросхемы независимо от изменчивости процесса и окружающих условий.

Изобретение относится к энергонезависимым полупроводниковым запоминающим устройствам. Самопрограммирующийся генератор напряжения в энергонезависимом полупроводниковом запоминающем устройстве имеет множество элементов памяти типа плавающего затвора, генератор проходного напряжения, предназначенный для программирования выбранных элементов памяти, и генератор программирующего напряжения. Последний предназначен для проверки того, успешно ли запрограммированы выбранные элементы памяти или нет. Генератор высокого напряжения предназначен для генерации программирующего напряжения. Схема подстройки предназначена для детектирования уровня программирующего напряжения с целью последовательного повышения программирующего напряжения в пределах заданного диапазона напряжений каждый раз, когда выбранные элементы памяти не запрограммированы успешно. Схема сравнения предназначена для сравнения определенного уровня напряжения с опорным напряжением с последующей генерацией сигнала сравнения. Схема управления генерацией высокого напряжения предназначена для активации генератора высокого напряжения в ответ на сигнал сравнения. Технический результат изобретения заключается в возможности обеспечения энергонезависимого полупроводникового запоминающего устройства способностью поддерживать однородное пороговое напряжение программируемых элементов памяти. 2 с. и 6 з.п.ф-лы, 12 ил.

| УСТРОЙСТВО ДЛЯ МАРКИРОВКИ ПЛОСКИХ ИЗДЕЛИЙ | 1971 |

|

SU432050A1 |

| МНОГООТСЧЕТНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГОЛ-КОД | 0 |

|

SU377840A1 |

| US 5291446 A, 01.03.94 | |||

| Электронно-лучевой прибор | 1982 |

|

SU1078494A1 |

| JP 05250889 A, 23.09.89 | |||

| Устройство для передачи и приема информации | 1975 |

|

SU543974A1 |

| US 5291447 A, 01.03.94. | |||

Авторы

Даты

2000-03-10—Публикация

1995-09-08—Подача