Область техники, к которой относится изобретение

Настоящее изобретение относится к режиму стирания в матрице флэш-памяти. Более конкретно, настоящее изобретение относится к режиму стирания страницы и к режиму стирания множественных страниц в матрице флэш-памяти.

Уровень техники

В традиционной матрице флэш-памяти матрица флэш-памяти обычно компонуется как матрица линий слов и разрядных линий для образования пересечений с элементами флэш-памяти, расположенными в пересечениях, способом, хорошо известным специалистам в данной области техники. Операциями, которые могут выполняться на ячейках памяти в матрице флэш-памяти, являются считывание, программирование и стирание.

Операция программирования часто выполняется возбуждением выбранных разрядных линий, соединенных с областью стока в ячейках флэш-памяти, до первого напряжения и возбуждения затворов ячеек флэш-памяти, соединенных с выбранными линиями слов, до более высокого напряжения для выполнения инжекции горячих электронов способом, хорошо известным специалистам в данной области техники.

Операция стирания выполняется возбуждением затвора ячейки флэш-памяти до напряжения, которое существенно меньше, чем напряжение, устанавливаемое на разрядной линии. При выполнении этого электроны туннелируются из свободного затвора ячеек флэш-памяти способом, хорошо известным специалистам в данной области техники. Для традиционных матриц флэш-памяти известно, что либо вся матрица флэш-памяти может быть стерта за один раз при так называемом тотальном стирании, либо сектор в матрице флэш-памяти может быть стерт за один раз при так называемом стирании сектора. Пример тотального стирания матрицы флэш-памяти приведен в статье "A 90ns 100K Erase-Program Cycle Megabit Flash Memory", 1989, Международная конференция по твердотельным схемам института инженеров по электротехнике и электронике, стр. 140 и 141, февраль 1989 г. Пример стирания сектора приведен в статье "A 55ns 0,35 m 5V Only 16M Flash Memory with Deep-Power-Down", 1996, Международная конференция по твердотельным схемам института инженеров по электротехнике и электронике, стр. 44 и 45, февраль 1996 г.

Ограничение операции стирания либо для стирания сектора, либо тотального стирания выполняется при рассмотрении того факта, что, когда отдельные линии ряда выбираются для стирания, имеется вероятность, что величина, хранимая в плавающем затворе ячеек флэш-памяти для невыбранных рядов, будет подвержена воздействию из-за присутствия непреднамеренного туннелирования. Таким образом, целью настоящего изобретения является обеспечение режима стирания, в котором только один ряд в секторе или множественные ряды в секторе могут быть стерты одновременно, уменьшая явление возбуждения для ячеек флэш-памяти в секторе, которые не выбираются.

Сущность изобретения

В соответствии с первым аспектом настоящего изобретения режим операции стирания страницы обеспечивается для сектора в матрице флэш-памяти. В режиме операции стирания страницы предпочтительное напряжение туннелирования приблизительно -10 В подается на затворы ячеек флэш-памяти в ряду, выбираемому для стирания страницы, а разрядные линии, соединенные со стоками ячеек флэш-памяти, возбуждаются до предпочтительного напряжения приблизительно 6,5 вольт (В). Для уменьшения непреднамеренного стирания ячеек памяти в рядах, отличных от выбранного ряда, предпочтительное напряжение смещения приблизительно от 1 В до 2 В подается на затворы всех ячеек флэш-памяти в рядах, отличных от выбранного ряда.

В соответствии со вторым аспектом настоящего изобретения обеспечивается режим стирания множественных страниц. В режиме стирания множественных страниц ряды в секторе разделяются на группы, и более чем один ряд в группе выбирается для стирания или соответствующие ряды в различных группах выбираются для стирания. В режиме стирания множественных страниц предпочтительное напряжение туннелирования приблизительно -10 В подается на затворы ячеек флэш-памяти в рядах, выбранных для стирания, а разрядные линии, соединенные со стоками ячеек флэш-памяти, возбуждаются до предпочтительного напряжения приблизительно 6,5 В. Для уменьшения наличия непреднамеренного стирания ячеек флэш-памяти в рядах, которые не выбираются, предпочтительное напряжение смещения приблизительно от 1 В до 2 В подается на затворы ячеек флэш-памяти в рядах, которые не выбраны для стирания.

Краткое описание сопроводительных чертежей

Фиг. 1 иллюстрирует блок-схему матрицы флэш-памяти в соответствии с настоящим изобретением.

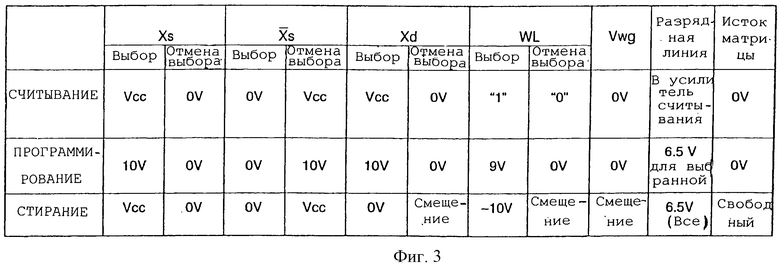

Фиг. 2 иллюстрирует принципиальную схему части сектора в матрице флэш-памяти фиг. 1 в соответствии с настоящим изобретением.

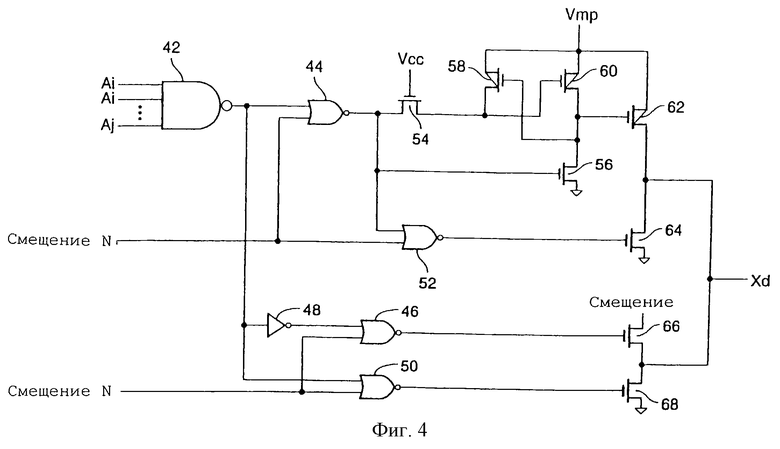

Фиг. 3 иллюстрирует таблицу сигналов, подаваемых в элементы в секторе, иллюстрируемом на фиг. 2, для режимов считывания, программирования и стирания страницы матрицы флэш-памяти, в соответствии с настоящим изобретением.

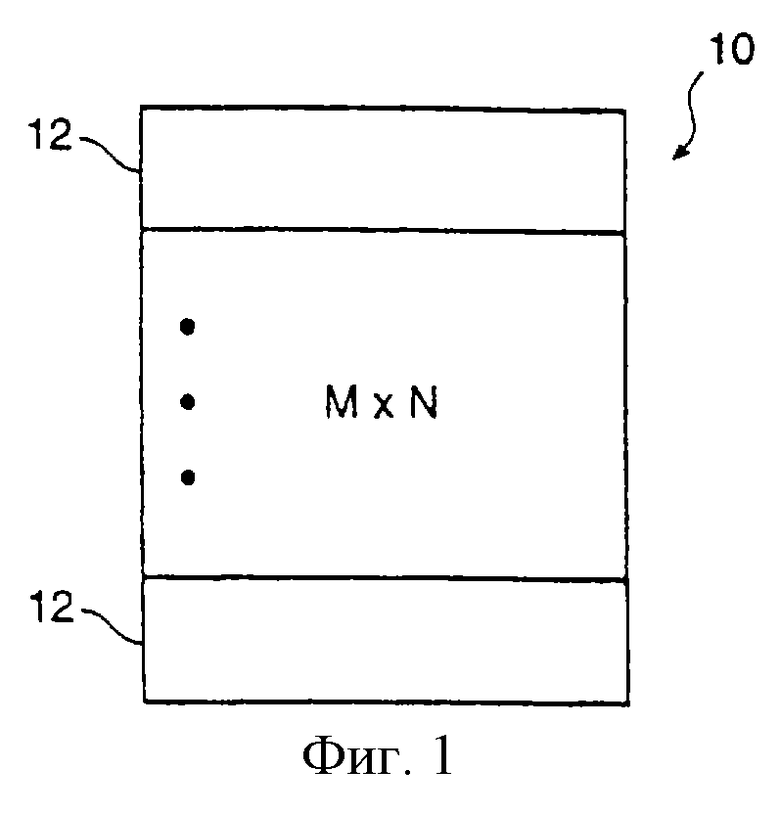

Фиг. 4 иллюстрирует принципиальную схему генератора переменного опорного сигнала, подходящего для использования в соответствии с настоящим изобретением.

Подробное описание предпочтительного варианта воплощения изобретения

Специалисты в данной области техники поймут, что последующее описание настоящего изобретения является только иллюстративным и никоим образом не ограничивающим объема патентной защиты. Другие варианты воплощения изобретения будут легко понятны специалистам.

На фиг. 1 иллюстрируется матрица 10 флэш-памяти в соответствии с настоящим изобретением. Матрица 10 флэш-памяти имеет М рядов, где каждый ряд имеет N байтов. Каждый из М рядов в матрице 10 флэш-памяти обычно называется страницей памяти. В матрице 10 флэш-памяти данные М рядов группируются в секторы или блоки способом, хорошо известным специалистам в данной области техники. Будет понятно, что число рядов, включаемых в сектор матрицы 10 флэш-памяти, обычно является вопросом выбора структуры, кроме того, что вся матрица 10 флэш-памяти может рассматриваться как один сектор. В предпочтительном варианте воплощения матрицы флэш-памяти объемом 4 мегабайта 2048 рядов (или страниц) из 264 байтов каждый группируются в 4 сектора, каждый из которых содержит 512 рядов.

Как обсуждалось выше, обычно имеются три операции, которые могут быть выполнены в ячейках памяти в матрице флэш-памяти. Этими тремя операциями являются считывание, программирования и стирание. В данной области техники известно выполнение стирания сразу всей матрицы флэш-памяти, т.е. тотальное стирание, и выполнение стирания всего сектора, называемое стиранием сектора. В соответствии с настоящим изобретением стирание может быть выполнено в одном ряду в секторе, известное как стирание страницы, либо в множественных страницах в секторе, известное как стирание множественных страниц.

На фиг. 2 иллюстрируется часть 14 сектора 12 в соответствии с настоящим изобретением. В части 14 сектора 12 ряды 20 разделяются на К групп, где каждая из К групп имеет J рядов. В предпочтительном варианте воплощения матрицы флэш-памяти объемом 4 мегабайта, описанной выше, 512 рядов в секторе разделяются на 64 группы, где каждая из 64 групп включает 8 рядов. В части 14 сектора 12 первая группа рядов 20-1 по 20-J изображена как группа 1, а последняя группа рядов 20-1 по 20-J изображена как группа К.

Каждый из рядов 20-1 по 20-J в матрице 10 флэш-памяти является линией слов, как хорошо известно специалистам в данной области техники. Каждая из линий слов рядов 20-1 по 20-J образует пересечения с разрядными линиями. Обычно число разрядных линий в матрице флэш-памяти равно числу слов в ряду 20, умноженному на число битов в каждом слове. Например, в предпочтительном варианте воплощения матрицы флэш-памяти 4 М, описанной выше, имеется 264 слова в каждом ряду и 8 битов в каждом слове. В результате будет 2112 разрядных линий в матрице флэш-памяти. В части 14 сектора 12 одна разрядная линия 22 изображена для иллюстративной цели.

В пересечениях между линиями 20 слов и разрядными линиями 22 находятся ячейки 24 флэш-памяти. Специфическое воплощение матрицы флэш-памяти не будет описываться здесь для исключения усложнения описания сущности настоящего изобретения. Ячейка флэш-памяти, подходящая для использования в соответствии с настоящим изобретением, описывается в патенте США 4783766, выданном на соответствующую заявку, поданную 30 мая 1986 г., права на который принадлежат настоящему заявителю.

К одному концу каждой линии 20 слов подключается пара N-канальных МОП-транзисторов 26-1 и 26-2. В каждой паре N-канальных МОП-транзисторов 26-1 и 26-2 сток первого N-канального МОП-транзистора 26-1 подключается к напряжению выбора ряда Xd, исток второго N-канального МОП-транзистора 26-2 подключается к напряжению смещения вентиля Vwg, a исток и сток первого N-канального МОП-транзистора 26-1 и второго N-канального МОП-транзистора 28-2 соответственно подключаются к линиям 20 слов.

Затвор каждого N-канального МОП-транзистора 26-1 подключается к сигналу выбора группы Xs, а затвор каждого N-канального МОП-транзистора 26-2 подключается к дополнению  сигнала выбора группы Xs, обеспечиваемому инвертором 28. Следует понимать, что инвертор 28 обеспечивает потенциал напряжения на

сигнала выбора группы Xs, обеспечиваемому инвертором 28. Следует понимать, что инвертор 28 обеспечивает потенциал напряжения на  , который либо выше на требуемую величину либо ниже, чем напряжение на Xs. Сигнал выбора группы Xs и его дополнение

, который либо выше на требуемую величину либо ниже, чем напряжение на Xs. Сигнал выбора группы Xs и его дополнение  обеспечиваются декодировщиком, реализация которого находится в компетенции специалистов в данной области техники, которая не раскрыта здесь для исключения чрезмерного усложнения описания сущности настоящего изобретения.

обеспечиваются декодировщиком, реализация которого находится в компетенции специалистов в данной области техники, которая не раскрыта здесь для исключения чрезмерного усложнения описания сущности настоящего изобретения.

Для каждого из элементов флэш-памяти, расположенных на пересечении линии 20 слов и разрядной линии 22, сток элемента флэш-памяти соединяется с разрядной линией 22, исток элемента 24 флэш-памяти подключается к напряжению истока матрицы линией 30 истока матрицы, а затвор элемента 24 флэш-памяти соединяется с линией 20 слов. Для каждой из линий 20 слов Р-канальный МОП-развязочный переходный транзистор 32 соединяется последовательно между каждой парой N-канальных транзисторов 26-1 и 26-2 и первым элементом 24 флэш-памяти, расположенным на пересечении линии 20 слов и разрядной линии 22. Соединенным с частью каждой линии 20 слов, расположенной между Р-канальным МОП-развязочным переходным транзистором 32 и затвором первого элемента 24 флэш-памяти, расположенным на пересечении линии 20 слов и разрядной линии 22, является генератор 34 накачки линии слов, соединенный с источником отрицательного напряжения приблизительно от -15 В до приблизительно -4 В, предпочтительно -10 В, линией 36 генератора накачки линии слов.

На фиг. 3 изображена таблица, указывающая сигналы, подаваемые в различные элементы в схеме, иллюстрируемой на фиг. 2, для реализации режимов считывания, программирования и стирания матрицы флэш-памяти, в соответствии с настоящим изобретением. В соответствии с настоящим изобретением только подача сигналов, выполняемая во время операции стирания, будет описана здесь.

Для выбора конкретного ряда для стирания страницы напряжение Vcc подается по линии сигнала выбора группы Xs на затворы N-канальных МОП-транзисторов 26-1 в группе, содержащей ряд 20-1 по 20-J, выбираемой для стирания страницы, а напряжение заземления (0 В) подается по линии дополнения сигнала выбора группы Xs на затворы N-канальных МОП-транзисторов 26-2 в группе, содержащей ряд 20-1 по 20-J, выбираемой для стирания страницы. Для рядов 20-1 по 20-J в группах, отличных от группы, имеющей ряд 20-1 по 20-J, выбираемой для стирания страницы, напряжение заземления (0 В) подается по линии сигнала выбора группы Xs на затворы N-канальных МОП транзисторов 26-1, а напряжение Vcc подается по линии дополнения сигнала выбора группы Хs на затворы N-канальных МОП-транзисторов 26-2.

Когда напряжения по линиям сигнала выбора группы Хs и  подаются, напряжение заземления (0 В) будет подаваться на затвор N-каналыюго МОП-транзистора 26-1 ряда 20-1 по 20-J, который выбирается для стирания страницы, а напряжение смещения в диапазоне приблизительно от 1 В до приблизительно 5 В и предпочтительно приблизительно от 1 В до приблизительно 2 В будет подаваться на стоки рядов 20-1 по 20-J, которые не выбираются для стирания страницы сигналом выбора ряда Xd и которые не находятся в той же самой группе, как ряд 20-1 по 20-J, выбираемые для стирания страницы.

подаются, напряжение заземления (0 В) будет подаваться на затвор N-каналыюго МОП-транзистора 26-1 ряда 20-1 по 20-J, который выбирается для стирания страницы, а напряжение смещения в диапазоне приблизительно от 1 В до приблизительно 5 В и предпочтительно приблизительно от 1 В до приблизительно 2 В будет подаваться на стоки рядов 20-1 по 20-J, которые не выбираются для стирания страницы сигналом выбора ряда Xd и которые не находятся в той же самой группе, как ряд 20-1 по 20-J, выбираемые для стирания страницы.

Напряжение заземления (0 В) будет также подаваться на стоки N-канальных МОП-транзисторов 26-1 ряда 20-1 по 20-J в невыбираемых группах, которые соответствуют выбранному ряду 20-1 по 20-J, и напряжение смещения в диапазоне приблизительно от 1 В до приблизительно 5 В и предпочтительно приблизительно от 1 В до приблизительно 2 В будет также подаваться на стоки N-канальных МОП-транзисторов 26-1 для рядов 20-1 по 20-J в невыбираемых группах, которые соответствуют не выбранным рядам 20-1 по 20-J в выбранной группе.

Например, когда выбираемым рядом 20-1 по 20-J является ряд 20-2 в группе 1, напряжение заземления (0 В) будет подаваться на сток N-канального МОП-транзистора 26-1 ряда 20-2, а также на стоки N-канальных МОП-транзисторов 26-1 ряда 20-2 в группах 2 по К. Кроме того, напряжение смещения будет подаваться на стоки N-канальных МОП-транзисторов 26-1 всех рядов 20-1 и 20-3 по 20-J в группе 1, а также на стоки N-канальных МОП-транзисторов 26-1 всех рядов 20-1 и 20-3 по 20-J в группах 2 по К включительно.

Дополнительно к подаче сигналов на стоки N-канальных МОП-транзисторов 26-1, когда подаются напряжения по линиям сигнала выбора группы Xs и  , напряжение смещения в диапазоне приблизительно от 1 В до приблизительно 5 В и предпочтительно от приблизительно 1 В до приблизительно 2 В подается на истоки N-канальных МОП-транзисторов 26-2 по линии сигнала Vwg.

, напряжение смещения в диапазоне приблизительно от 1 В до приблизительно 5 В и предпочтительно от приблизительно 1 В до приблизительно 2 В подается на истоки N-канальных МОП-транзисторов 26-2 по линии сигнала Vwg.

Когда эти напряжения подаются на затворы N-канальных МОП-транзисторов 26-1 и 26-2, включаются сток N-канального МОП-транзистора 26-1 и исток N-канального МОП-транзистора 26-2, Р-канальные развязочные переходные транзисторы 32-1 по 32-J.

В результате напряжение заземления (0 В) будет подаваться на затворы элементов 24 флэш-памяти в выбранном ряду 20-1 по 20-J, а напряжение смещения будет подаваться на элементы флэш-памяти во всех остальных рядах 20-1 по 20-J. Следует понимать из вышеприведенного обсуждения, что для выбранной группы 1 по К, содержащей выбранный ряд 20-1 по 20-J, напряжение смещения, подаваемое на затворы элементов 24 флэш-памяти в не выбранных рядах 20-1 по 20-J в выбранной группе, подается по линии сигнала Xd, соединенной со стоками N-канальных МОП-транзисторов 26-1, и что для всех остальных рядов 20-1 по 20-J в невыбранных группах 1 по К напряжение смещения, подаваемое на затворы элементов 24 флэш-памяти, обеспечивается напряжением, подаваемым по линии сигнала Vwg на истоки N-канальных МОП-транзисторов 26-2.

Когда напряжение заземления (0 В) подано на затворы ячеек 24 флэш-памяти в выбранном ряду 20-1 по 20-J и напряжение смещения в диапазоне приблизительно от 1 В до приблизительно 5 В и предпочтительно приблизительно от 1 В до приблизительно 2 В подано на затворы всех остальных ячеек 24 флэш-памяти, напряжение подается на затворы Р-канальных МОП-развязочных переходных транзисторов 32-1 по 32-J так, что Р-канальный МОП-развязочный переходный транзистор 32-1 по 32-J, соединенный с выбранным рядом 20-1 по 20-J, выключается благодаря напряжению затвор-исток. Отрицательное напряжение в диапазоне приблизительно от -15 В до приблизительно -4 В и предпочтительно приблизительно -10 В подается в выбранный ряд 20-1 по 20-J в выбранной группе 1 по К генератором 34 накачки линии слов, соединенным с выбранным рядом 20-1 по 20-J.

Чтобы избежать чрезмерного усложнения описания сущности настоящего изобретения, реализация генератора 34 накачки линии слов или другого средства для подачи отрицательного напряжения в выбранную линию ряда 20-1 по 20-J, хорошо известная специалистам в данной области техники, не будет описана здесь. Реализация генератора 34 накачки линии слов, подходящего для использования в соответствии с настоящим изобретением, раскрыта в патентах США 4511811, выданном на соответствующую заявку, поданную 8 февраля 1982 г., и 4673829, выданном на заявку, поданную 8 февраля 1985 г., права на которые принадлежат настоящему заявителю.

Так как Р-канальный МОП-развязочный переходный транзистор 32-1 по 32-J, соединенный с выбранным рядом 20-1 по 20-J, выключен, отрицательное напряжение, подаваемое на затворы ячеек 24 флэш-памяти в выбранном ряду 20-1 по 20-J, не будет воздействовать на пару N-канальных МОП-транзисторов 26-1 и 26-2 для отрицательного напряжения. Кроме того, при первой подаче напряжения заземления на затворы ячеек 24 флэш-памяти в выбранном ряду 20-1 по 20-J, а не напряжения смещения меньше энергии и времени тратится генератором 34 накачки при подаче отрицательного напряжения на затворы ячеек 24 флэш-памяти в выбранном ряду 20-1 по 20-J.

Для завершения выполнения операции стирания страницы все разрядные линии 22 возбуждаются до положительного напряжения приблизительно от 5 В до приблизительно 10 В и предпочтительно приблизительно 6,5 В. В результате туннелирование будет происходить между плавающим затвором и истоком ячейки 24 флэш-памяти по выбранному ряду 20-1 по 20-J способом, хорошо известным специалистам в данной области техники, для стирания ячеек 24 флэш-памяти по выбранному ряду 20-1 по 20-J, так как разность потенциалов приблизительно от 12 В до приблизительно 20 В и предпочтительно приблизительно 16,5 В установилась между стоком и свободным затвором ячеек 24 флэш-памяти по выбранному ряду 20-1 по 20-J.

В соответствии с настоящим изобретением, когда положительное напряжение приблизительно от 5 В до приблизительно 10 В и предпочтительно приблизительно 6,5 В подается на разрядные линии 22, ячейки 24 флэш-памяти по всем не выбранным рядам 20-1 по 20-J будут менее чувствительны к туннелированию, так как напряжение смещения приблизительно от 1 В до приблизительно 5 В и предпочтительно приблизительно от 1 В до приблизительно 2 В подано на затворы ячеек 24 флэш-памяти по всем из не выбранных рядов 20-1 по 20-J.

Следует понимать из вышеприведенного обсуждения, что стирание множественных страниц может быть выполнено на множественных страницах в выбранной группе подачей напряжения заземления (0 В) на стоки каждого из N-канальных МОП-транзисторов 26-1 каждого из множественных выбранных рядов 20-1 по 20-J для установления напряжения заземления (0 В) на затворах ячеек 24 флэш-памяти по всем из множественных выбранных рядов 20-1 по 20-J. Генераторы 34 накачки линии слов, соединенные с множественными выбранными рядами 20-1 по 20-J, затем выбираются для установления отрицательного напряжения приблизительно от -15 В до приблизительно -4 В и предпочтительно приблизительно -10 В на затворах ячеек 24 флэш-памяти по всем из множественных выбранных рядов 20-1 по 20-J включительно.

Когда положительное напряжение приблизительно от 5 В до приблизительно 10 В и предпочтительно приблизительно 6,5 В подается в разрядные линии 22, туннелирование будет происходить между плавающими затворами и стоками ячеек 24 флэш-памяти по множественным выбранным рядам 20-1 по 20-J способом, хорошо известным специалистам в данной области техники, для стирания ячеек 24 флэш-памяти по множественным выбранным рядам 20-1 по 20-J, так как разность потенциалов приблизительно от 12 В до приблизительно 20 В и предпочтительно приблизительно 16,5 В установлена между стоком и плавающим затвором ячеек 24 флэш-памяти по множественным выбранным рядам 20-1 по 20-J включительно.

На фиг. 4 иллюстрируется схема 40 переменного опорного генератора для обеспечения опорного напряжения выбора ряда Xd для режимов считывания, программирования и стирания. В схеме 40 генератора переменного опорного напряжения логический элемент НЕ-И имеет множество входов, которые расшифровывают, будет ли выбираться конкретный ряд 20-1 по 20-J в группе. Выход логического элемента 42 НЕ-И соединяется с первым входом логического элемента 44 ИЛИ-НЕ, первым входом логического элемента 46 ИЛИ-НЕ чрез инвертор 48 и первым входом логического элемента 50 ИЛИ-НЕ.

Второй вход логического элемента 44 ИЛИ-НЕ соединяется с разрешающей линией смещения, которая становится высокой, когда матрица флэш-памяти находится в режиме стирания. Вторые входы логических элементов 46 и 50 ИЛИ-НЕ соединяются с дополнением разрешающего сигнала смещения. Выход логического элемента 44 ИЛИ-НЕ соединяется с первым входом логического элемента 52 ИЛИ-НЕ, а второй вход логического элемента 53 ИЛИ-НЕ соединяется с разрешающим сигналом смещения. Выход логического элемента 44 ИЛИ-НЕ также соединяется с истоком N-канального МОП-переходного транзистора 54 и с затвором N-канального ослабляющего транзистора 56.

Затвор N-канального МОП-развязочного переходного транзистора 54 соединяется с развязочным управляющим сигналом, который является предпочтительно Vcc. Опорный потенциал переменного напряжения Vmp подключается к истокам Р-канальных МОП-транзисторов 58, 60 и 62. Исток N-канального МОП-транзистора 56 соединяется с землей. Затворы Р-канальных МОП-транзисторов 58 и 62 соединяются со стоком N-канального МОП-транзистора 56, а затвор Р-канального МОП-транзистора 60 соединяется со стоком N-канального МОП-развязочного переходного транзистора 54 вместе со стоком Р-канального МОП-транзистора 58. Сток Р-канального МОП-транзистора 60 также соединяется со стоком N-канального МОП-транзистора 56. N-канальный МОП-транзистор 64 имеет свой затвор, соединенный с выходом логического элемента 52 ИЛИ-НЕ, исток, соединенный с землей, и сток, соединенный со стоком Р-канального МОП-транзистора 62 для образования выхода Xd схемы 40 генератора опорного напряжения.

Выходы логических элементов 46 и 50 ИЛИ-НЕ соединяются с затворами N-канальных МОП-транзисторов 66 и 68. Сток N-канального МОП-транзистора 66 соединяется с напряжением смещения, а исток N-канального МОП-транзистора 68 соединяется с землей. Исток N-канального МОП-транзистора 66 соединяется со стоком N-канального МОП-транзистора 68 для образования узла, который соединяется с выходом Xd схемы 40 генератора опорного напряжения.

При работе схемы 40 генератора переменного опорного сигнала, когда выполняется режим стирания страницы, разрешающий сигнал смещения устанавливается высоким так, что выход логических элементов 44 и 52 ИЛИ-НЕ будет низким. Низкий сигнал, проходящий через N-канальный МОП-транзистор 54 на затвор Р-канального МОП-транзистора 60, установит переменное напряжение Vmp на затворе Р-канального МОП-транзистора 62. Напряжения Vmp в режимах считывания, программирования и стирания страницы предпочтительно равны Vcc, 10 В и Vcc соответственно. В результате, Р-канальный МОП-транзистор 62 выключится. Низкий сигнал, подаваемый логическим элементом 52 ИЛИ-НЕ в затвор N-канального МОП-транзистора 64, также выключит N-канальный МОП-транзистор 64.

В режиме стирания страницы, когда разрешающий сигнал смещения устанавливается высоким, дополнение разрешающего сигнала смещения, соединенного с логическими элементами 46 и 50 ИЛИ-НЕ, является низким. Также с логическими элементами 46 и 50 ИЛИ-НЕ является инвертированный выход логического элемента 42 НЕ-И и выход логического элемента 42 НЕ-И соответственно. Низкий выходной сигнал из логического элемента 42 НЕ-И указывает, что выбирается конкретный ряд 20-1 по 20-J. Таким образом, когда низкий выходной сигнал логического элемента 42 НЕ-И подается в логический элемент 50 ИЛИ-НЕ, Xd заземлится через N-канальный МОП-транзистор 68, который включается выходным сигналом логического элемента 50 ИЛИ-НЕ, а когда высокий выходной сигнал логического элемента 42 НЕ-И подается как низкий сигнал в логический элемент 46 ИЛИ-НЕ через инвертор 48, выходной сигнал Xd подтянется до напряжения смещения через N-канальный МОП-транзистор 66, который включается выходным сигналом логического элемента 46 ИЛИ-НЕ.

Во время либо режима считывания, либо режима программирования разрешающий сигнал смещения будет низким, а низкий сигнал из логического элемента 42 НЕ-И сделает выходной сигнал логического элемента 44 ИЛИ-НЕ высоким, а высокий сигнал из логического элемента 42 НЕ-И сделает выходной сигнал логического элемента 44 ИЛИ-НЕ низким. Когда выходной сигнал логического элемента 44 является высоким, напряжение Vmp установится на выходе Xd через Р-канальный МОП-транзистор 62, который включается, когда его затвор заземляется через N-канальный МОП-транзистор 56, который включается высоким сигналом из логического элемента 44 ИЛИ-НЕ. Когда выходной сигнал логического элемента 44 ИЛИ-НЕ является низким, напряжение заземления будет установлено на выходе Xd через N-канальный МОП-транзистор 64, который включается высоким сигналом из логического элемента 52 ИЛИ-НЕ.

Несмотря на то, что были изображены и описаны варианты воплощения настоящего изобретения, специалистам в данной области техники будет понятно значительно большее число модификаций, чем упомянутые выше, не выходящие из описанной здесь изобретательской концепции. Таким образом, настоящее изобретение не ограничивается приведенными здесь вариантами его воплощения, а объем его патентной защиты определяется формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| МАТРИЦА ФЛЭШ-ПАМЯТИ С ВНУТРЕННИМ ОБНОВЛЕНИЕМ | 1999 |

|

RU2224303C2 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО НЕРАЗРУШАЕМОЙ ПАМЯТИ | 1992 |

|

RU2097842C1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1999 |

|

RU2249262C2 |

| ЭЛЕКТРИЧЕСКИ СТИРАЕМАЯ И ПРОГРАММИРУЕМАЯ ЭНЕРГОНЕЗАВИСИМАЯ НАКОПИТЕЛЬНАЯ ЯЧЕЙКА | 1996 |

|

RU2168242C2 |

| УСТРОЙСТВО ПАМЯТИ И СПОСОБ ИЗГОТОВЛЕНИЯ | 2001 |

|

RU2247441C2 |

| СХЕМА УПРАВЛЕНИЯ ДЛЯ ЭНЕРГОНЕЗАВИСИМОГО ПОЛУПРОВОДНИКОВОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1998 |

|

RU2221286C2 |

| ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2089943C1 |

| Ячейка оперативной памяти | 2024 |

|

RU2826859C1 |

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 1996 |

|

RU2111556C1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ИНТЕГРАЦИИ И СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1996 |

|

RU2153210C2 |

Изобретение относится к режиму стирания в матрице флэш-памяти. Техническим результатом является значительное уменьшение возбуждения не выбранных для стирания ячеек памяти при стирании выбранных ячеек памяти. Устройство матрицы флэш-памяти содержит множество транзисторов ячеек памяти, средство для подачи первого напряжения на управляющий затвор, по меньшей мере, одного транзистора стираемой ячейки упомянутой памяти, средство для подачи второго напряжения, более положительного, чем первое напряжение, на управляющие затворы всех транзисторов ячеек упомянутой памяти, отличных от упомянутого, по меньшей мере, одного транзистора стираемой ячейки упомянутой памяти, средство для подачи третьего напряжения, более положительного, чем упомянутое второе напряжение, на сток упомянутого, по меньшей мере, одного транзистора стираемой ячейки упомянутой памяти и на стоки упомянутых транзисторов не стираемых ячеек памяти. Способы описывают работу указанного устройства. 3 с. и 11 з.п.ф-лы, 4 ил.

| US 5278785 А, 11.01.1994 | |||

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1981 |

|

SU1012704A1 |

| US 5365484 А, 15.11.1994 | |||

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1982 |

|

SU1108915A1 |

Авторы

Даты

2004-01-20—Публикация

1999-03-12—Подача