Изобретение относится к способу программирования запоминающего устройства, в частности к способу программирования энергонезависимой полупроводниковой памяти.

Стоимость энергонезависимых полупроводниковых запоминающих устройств, таких как электрически стираемое программируемое постоянное запоминающее устройство (ЭСППЗУ) и флэш-ЭСППЗУ, используемые в качестве запоминающей среды сверхбольшой емкости, слишком велика из расчета на один бит. В качестве метода решения этой проблемы в настоящее время произведено исследование ячейки памяти емкостью в несколько битов.

Плотность записи энергонезависимой памяти соответствует числу ячеек памяти в пропорции один к одному. Ячейка памяти в несколько битов хранит по меньшей мере два бита данных в одной ячейке памяти, тем самым значительно увеличивая плотность размещения информации в одной и той же области кристалла, не уменьшая при этом размер ячейки памяти.

Для осуществления ячейки памяти емкостью в несколько битов для каждой ячейки памяти нужно программировать более трех уровней порогового напряжения. Например, для хранения двух битов данных в одной ячейке соответствующие ячейки становятся программируемыми четырьмя этапами порогового уровня, т.е. 22 = 4. В результате этого четыре этапа порогового уровня логически относятся к соответствующим логическим состояниям 00, 01, 10 и 11.

В упомянутом выше многоуровневом программировании особо важно, чтобы соответствующие уровни порогового напряжения имели статистическое распределение около 0,5 В.

Следовательно, по мере уменьшения распределения путем точного регулирования соответствующих пороговых уровней можно программировать большее число уровней, тем самым создавая возможность увеличения числа битов в одной ячейке.

Для уменьшения вышеупомянутого распределения напряжения в программировании пользуются общепринятым способом повторяющегося программирования и контроля. Согласно этому способу, последовательность импульсов напряжения прикладывается к ячейке для программирования ячейки энергонезависимой памяти на нужном пороговом уровне. Считывание, происходящее между соответствующими импульсами напряжения, контролирует, достигла ли ячейка нужного порогового уровня. Во время этого контроля, когда величина проверяемого порогового уровня достигает нужной величины порогового уровня, процесс программирования останавливается.

В системе повторяющегося программирования и контроля трудно уменьшить распределение погрешностей пороговых уровней по причине длительности импульса напряжения программирования. Кроме этого, реализация алгоритма повторяющегося программирования и контроля требует использования дополнительной схемы, вследствие чего область периферийной схемы кристалла увеличивается. К тому же данный способ приводит к увеличению времени программирования.

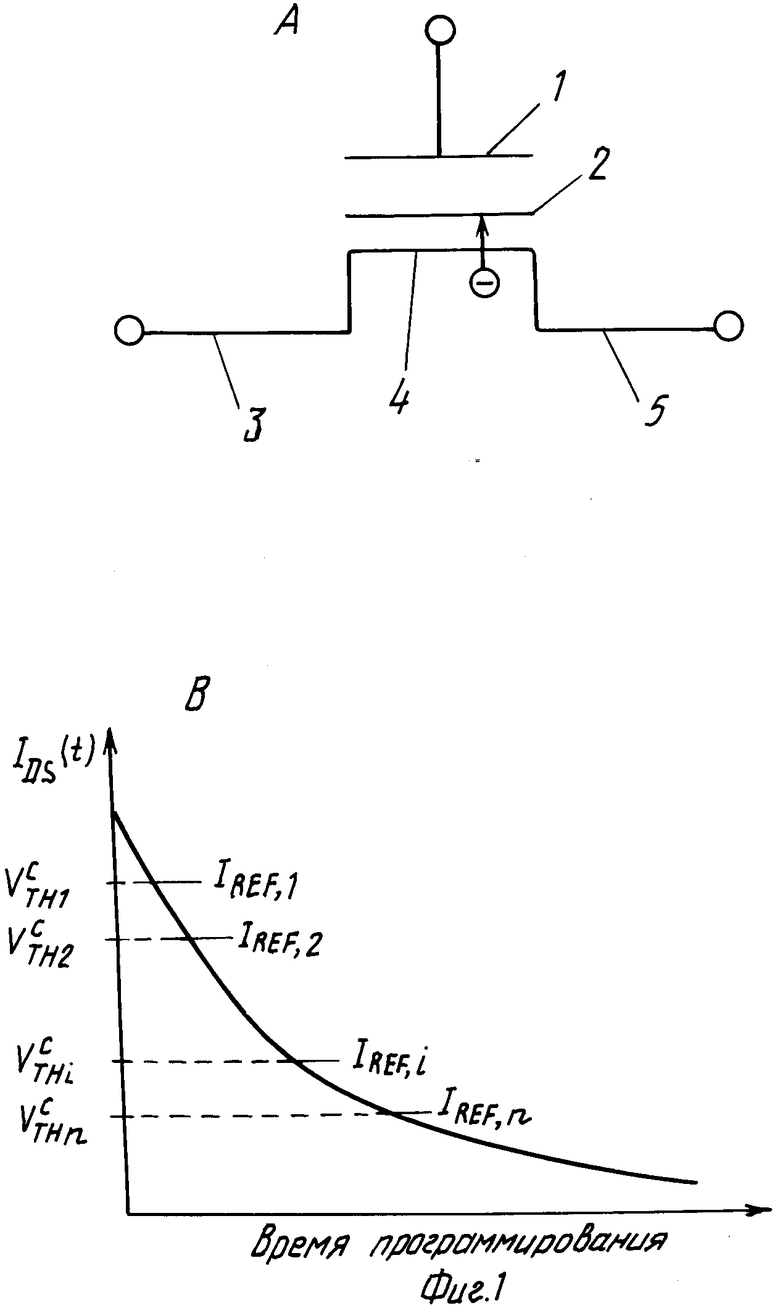

Для устранения перечисленных выше недостатков Р. Сернеа из компании "СанДиск" предложил способ одновременного программирования и контроля (патент США N 5422842). На фиг. 1A изображена условная электрическая схема ЭСППЗУ, предложенного Р. Сернеа. Ячейка ЭСППЗУ состоит из управляющего затвора 1, плавающего затвора 2, истока 3, канальной области 4 и стока 5.

Когда достаточное для осуществления программирования напряжение прилагается к управляющему затвору 1 и стоку 5, ток протекает между 5 и истоком 3. Этот ток сравнивается с заданным эталонным током, чтобы генерировать сигнал завершения программирования, когда этот ток равен эталонному току или меньше его.

При этом способе состояние программирования автоматически контролируется одновременно с программированием для устранения недостатков способа повторяющегося программирования и контроля. Однако уровень порогового напряжения, прикладываемого к управляющему затвору 1 ячейки памяти, не регулируется.

Патент США N 5043940 на имя Харари выполняет многоуровневое программирование путем измерения эталонных токов, относящихся к соответствующим уровням. Как показано на фиг. 1B, эталонные токи для контролирования не соотносятся явно или линейно с пороговыми напряжениями ячейки. Поэтому многоуровневое программирование не может непосредственно и эффективно контролироваться при способе управления током.

Соответственно, данное изобретение направлено на способ программирования энергонезависимой памяти, который позволяет в значительной степени решить одну или несколько проблем, обусловленных ограничениями и недостатками существующего уровня развития техники в данной области.

Цель изобретения состоит в создании способа программирования энергонезависимой памяти, который обеспечит одновременный контроль пороговых уровней при выполнении двухуровневого или многоуровневого программирования.

Другая цель изобретения заключается в создании способа программирования энергонезависимой памяти для регулирования соответствующих пороговых уровней напряжения, прилагаемых к управляющему затвору при выполнении двухуровневого или многоуровневого программирования, при котором соответствующие пороговые уровни и напряжение, прилагаемое к управляющему затвору, относящееся к соответствующим пороговым уровням, имеют линейную взаимозависимость.

Дополнительные признаки и преимущества данного изобретения будут изложены в следующем ниже описании и частично будут очевидны из описания, либо могут быть выявлены при практическом использовании изобретения. Цели и прочие преимущества данного изобретения будут реализованы и достигнуты структурой, конкретно изложенной в описании и формуле изобретения, и также на иллюстрирующих изобретение чертежах.

Для достижения вышеуказанных преимуществ и в соответствии с данным изображением - в том виде, в каком оно осуществлено и подробно описано, - предлагается способ программирования ячейки энергонезависимой памяти, которая имеет управляющей затвор, плавающий затвор, сток, исток и канальную область, расположенную между стоком и истоком, причем способ включает следующие операции: приложение первого напряжения к управляющему затвору для формирования инверсионного слоя в канальной области, причем первое напряжение изменяется для осуществления программирования по меньшей мере на двух пороговых уровнях ячейки памяти, приложение второго напряжения к стоку и третьего - к истоку, причем второе напряжение превышает третье напряжение, контроль тока, протекающего между стоком и истоком, при программировании на по меньшей мере двух пороговых уровнях, и прекращение подачи одного из напряжений - первого, второго, третьего - при достижении контролируемым током заданного эталонного тока, тем самым завершая программирование по меньшей мере на двух пороговых уровнях.

Ячейка энергонезависимой памяти, такая как ячейка ЭСППЗУ, в соответствии с данным изобретением включает в себя управляющий затвор, плавающий затвор, сток, исток и канальную область, расположенную между стоком и истоком.

Предложенный способ программирования по данному изобретению выполняется путем приложения первого напряжения, измеряемого согласно соответствующим пороговым уровням при программировании по меньшей мере на двух пороговых уровнях, к управляющему затвору для программирования ячейки ЭСППЗУ и формирования инверсионного слоя в канальной области. После этого второе напряжение и третье напряжения прикладываются соответственно к стоку и истоку таким образом, что прилагаемое к стоку напряжение выше того, которое прилагается к истоку. Затем ток, протекающий между стоком и истоком, контролируется при программировании соответствующих пороговых уровней ячейки ЭСППЗУ, и подача одного из напряжений (первого, второго, третьего), соответственно прилагаемых к управляющему затвору, стоку и истоку, прекращается для остановки программирования, когда контролируемый ток достигает заданного эталонного тока.

Нужно отметить, что как изложенное выше общее описание, так и следующее ниже подробное описание, приведены для примера и пояснений и предназначены для того, чтобы дать дальнейшее объяснение изобретения в том виде, в каком оно сформулировано в формуле изобретения.

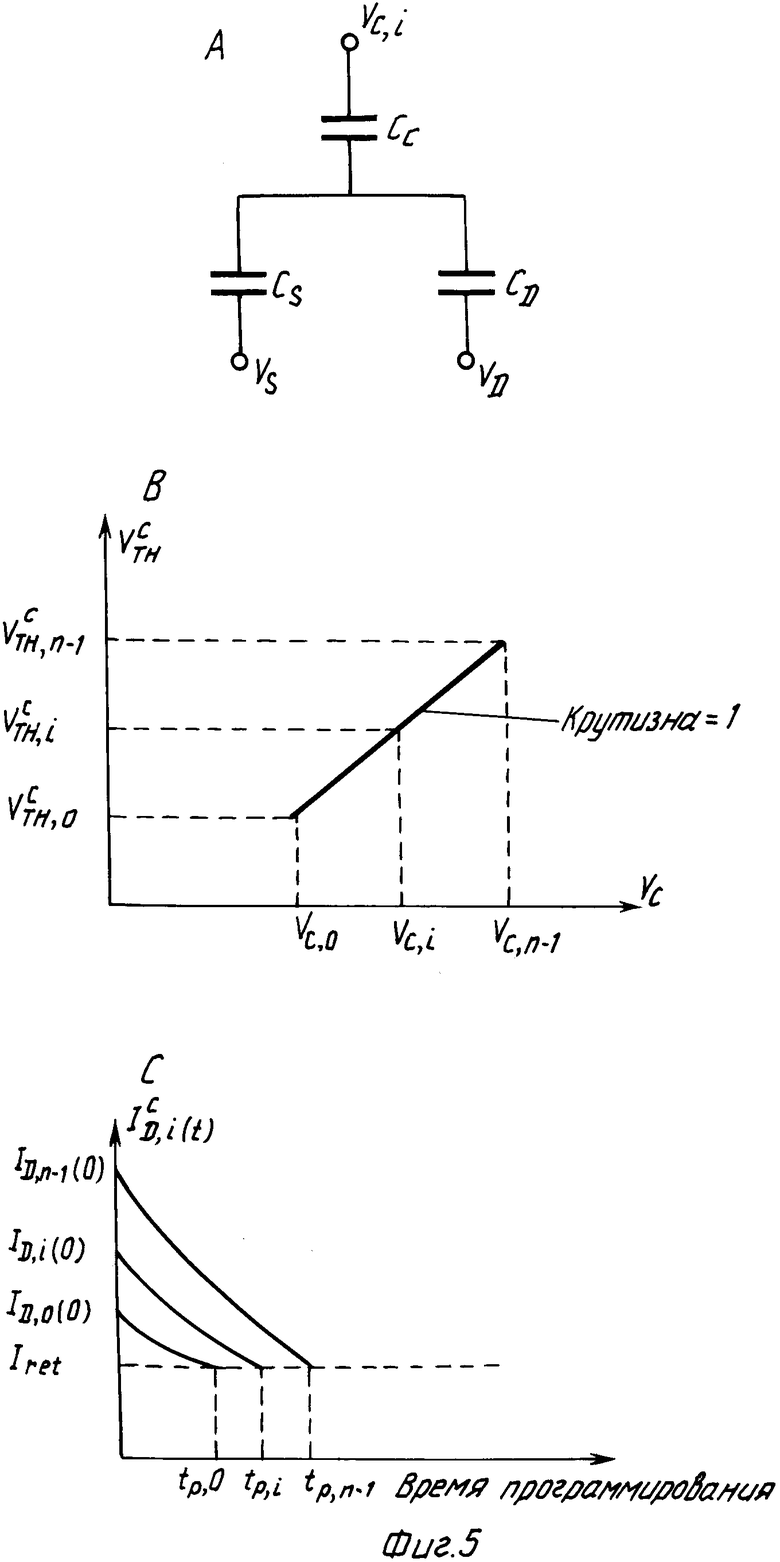

Прилагаемые чертежи предназначаются для дополнительного пояснения изобретения, представляют собой составную часть описания, иллюстрируют варианты осуществления изобретения, и вместе с описанием служат объяснению принципов данного изобретения. На фиг. 1A приведена принципиальная схема обычной ячейки энергонезависимой памяти; на фиг.1B - график, изображающий принцип автоматического контроля программирования ячейки энергонезависимой памяти фиг 1A; на фиг. 2 - схема, поясняющая способ программирования с использованием детектирования тока в соответствии с осуществлением изобретения; на фиг. 3A - 3G временная диаграмма сигналов для соответствующих узлов фиг. 2; на фиг. 4 - блок-схема процесса двухуровневого или многоуровневого программирования в соответствии с предпочтительным осуществлением изобретения; на фиг. 5A - эквивалентная принципиальная схема ячейки энергонезависимой памяти, изображенной на фиг. 1A, иллюстрирующая электрическую емкость, на фиг. 5B - график взаимосвязи между пороговыми уровнями, подлежащими программированию, и соответствующими напряжениями управляющего затвора; на фиг. 5C - график изменения тока стока от начала до завершения программирования по соответствующим уровням.

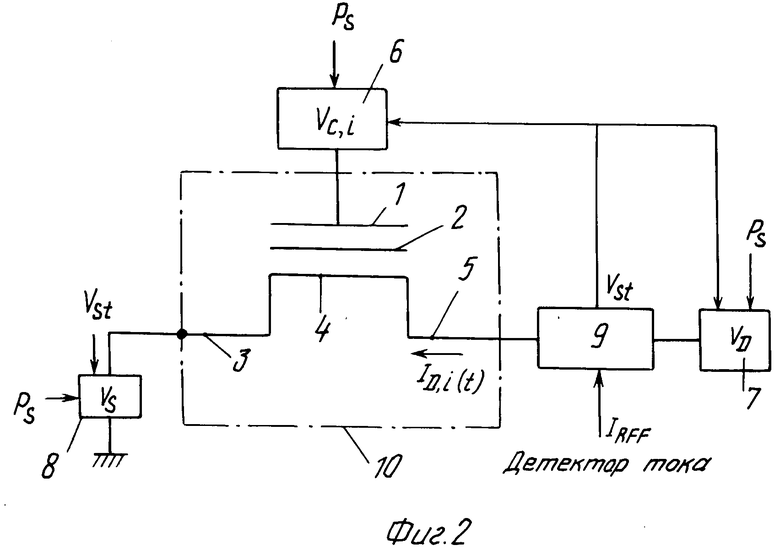

На фиг. 2 представлена схема, иллюстрирующая конструкцию энергонезависимого запоминающего устройства, предназначенную для осуществления способа программирования согласно данному изобретению. Энергонезависимое ЗУ, изображенное на фиг. 2, содержит первый источник напряжения 6, второй источник напряжения 7, третий источник напряжения 8, детектор тока 9 и ячейку ЭСППЗУ 10. Ps обозначает сигнал начала программирования от внешних устройств, Vst обозначает сигнал остановки программирования. На фиг. 1A показана наиболее распространенная структура ячейки ЭСППЗУ 10. Другими словами, типичная ячейка энергонезависимой памяти разнообразных типов, такая как с простым многоуровневым затвором, и структура с расщепленным каналом, может быть упрощена для рассмотрения режима операционного программирования до получения структуры, изображенной на фиг. 1A.

Источник первого напряжения 6 подает напряжение VC,i (где i = 0, 1, 2, . . . и n - 1) на управляющей затвор 1 ячейки ЭСППЗУ 10 для программирования i-го порогового уровня в многоуровневом программировании. Соответственно, напряжение VC,i имеет разные величины для каждого уровня. Источник второго напряжения 7 подает напряжение VD на сток 5, а источник третьего напряжения 8 подает напряжение VS на исток 3. Здесь в качестве напряжения VS может прилагаться любая величина, но для удобства объяснения предлагается, что Vs - напряжение земли, ID,i(t) обозначает ток, протекающий к столу 5. Детектор тока 9 имеет эталонную величину тока IREF и генерирует сигнал остановки программирования VST, когда ток ID,i(t), протекающий через сток 5, достигает величины эталонного тока IREF при программировании i-го порогового уровня.

Время tP,i обозначает момент окончания программированного i-го порогового уровня. В это время эталонный ток IREF детектора тока 9 определяется электрической характеристикой ячейки ЭСППЗУ 10, которая использует метод программирования согласно данному изобретению.

При повторном определении тока ID,i(t) стока 5 ток ID,i(t) стока зависит от времени. Эта величина ID,i(t) тока обозначает величину тока в стоке 5, обусловленную напряжением VF,i(t) на плавающем затворе 2 при программировании i-го уровня. Ток ID,i(t) является максимальным в начале периода программирования и уменьшается в процессе программирования. Также сигнал VST остановки программирования генерируется детектором тока 9, когда ток уменьшается ниже эталонного тока IREF детектора тока 9.

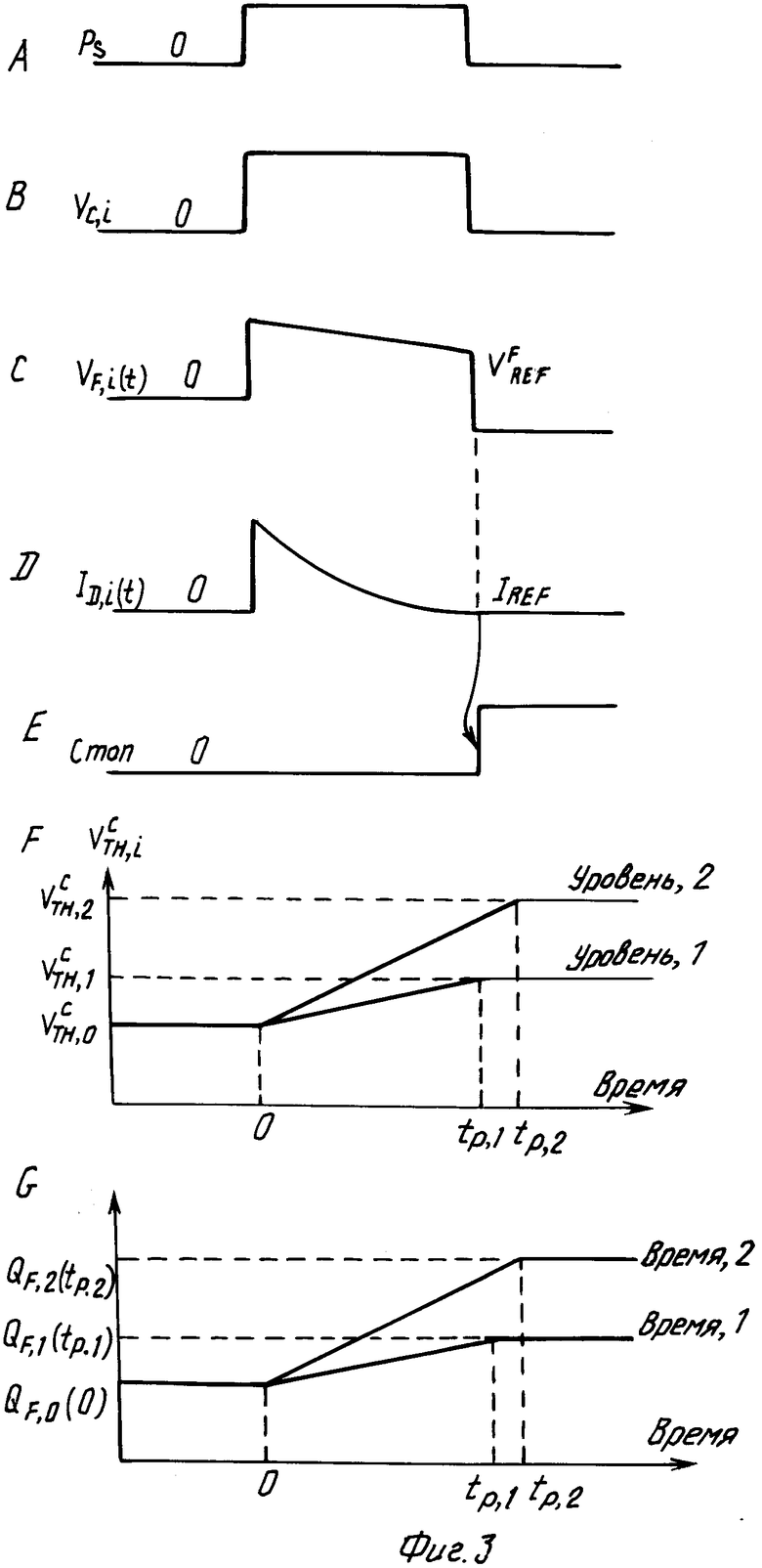

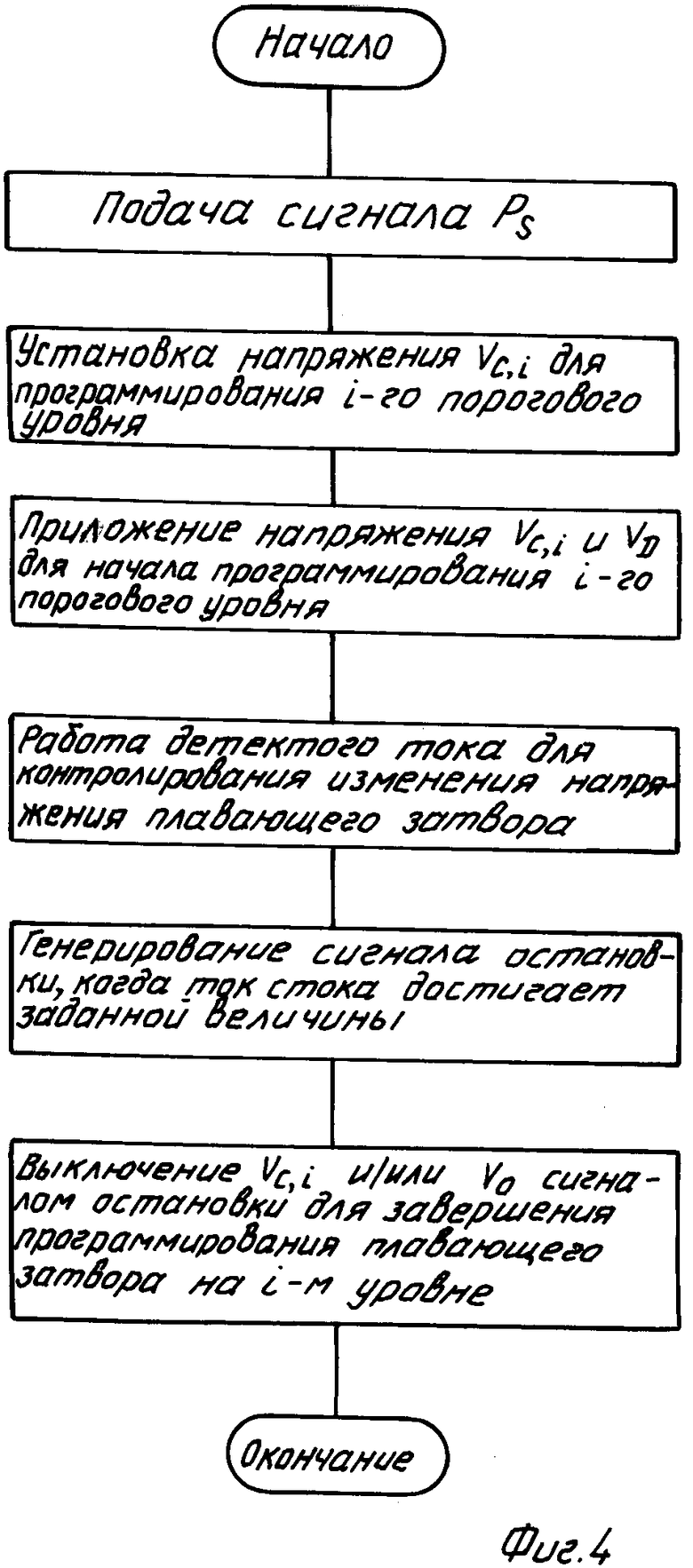

При описанных выше условиях процесс двухуровневого или многоуровневого программирования будет описан со ссылками на фиг. 3 и 4. На фиг. 3A - 3G изображены временные диаграммы сигналов в соответствующих точках схемы по фиг. 2, а фиг. 4 представляет собой блок-схему, изображающую процесс двухуровневого или многоуровневого программирования в соответствии с данным изображением. Далее способ программирования ячейки ЭСППЗУ 10 по фиг. 2 в соответствии с данным изобретением будет подробно описываться со ссылкой на блок-схему алгоритма, представленную на фиг. 4.

Для программирования ячейки ЭСППЗУ 10 и формирования инверсионного слоя в канальной области 4 первое напряжение, которое изменяется согласно программированию каждого порогового уровня во время программирования по меньшей мере на двух пороговых уровнях, прилагается к управляющему затвору 1, а второе напряжение и третье напряжение прилагаются соответственно к стоку 5 и истоку 3, при этом прилагаемое к стоку 5 напряжение превышает то, которое прилагается к истоку 3. Затем ток, протекающий между стоком 5 и истоком 3, контролируется при программировании соответствующих пороговых уровней ячейки ЭСППЗУ 10, и подача одного из напряжений (соответственно первого, второго, третьего), прилагаемых к управляющему затвору 1, стоку 5, истоку 3, прекращается, чтобы остановиться программирование, когда ток достигает величины заданного эталонного тока.

Этот способ будет подробно описан ниже. Предполагается, что соответствующая ячейка перед выполнением программирования находится в стертом состоянии. Здесь стертое состояние обозначает нулевой уровень, который является низшим уровнем. Также предполагается, что полевой транзистор плавающего затвора имеет структуру с каналом n-типа на подложке p-типа.

Во-первых, как показано на фиг. 3A, когда внешний сигнал Ps начала программирования подается для двухуровневого или многоуровневого программирования, напряжение VC,i, прилагаемое к управляющему затвору 1, устанавливается для программирования i-го уровня. В то время, когда подается сигнал Ps фиг. 3A начала программирования, напряжения VC,i, изображенные в фиг. 3B, и VD подаются от источника первого напряжения 6 и источника второго напряжения 7 на управляющий затвор 1 и источник 5 соответственно.

При этих условиях в плавающий затвор 2 подаются электроны для программирования i-го порогового уровня. В данном случае для подачи заряда в плавающий затвор 2 можно использовать любой механизм программирования, но обычно используется горячая инжекция носителей заряда или механизм туннелирования.

После приложения напряжений VC,i и VD соответственно к управляющему затвору 1 и стоку 5 включается детектор 9 для контролирования изменения напряжения в плавающем затворе 2. После приложения напряжений VC,i и VD к управляющему затвору 1 и стоку 5, как показано на фиг. 3C, напряжение VF,i(t) для программирования i-го порогового уровня подается на плавающий затвор 2, и в канальной области 4 полевого транзистора формируется инверсионный слой. Фактически, поскольку исток 3, сток 5 и канальная область 4 размещаются на полупроводниковой подложке (не показана), ток после формирования инверсионного слоя идет от стока 5 к истоку 3 через канальную область 4. В это время ток ID,i(t), протекающий в сток 5, максимален в начале периода, как показано на фиг. 3D, и электроны инжектируются в плавающий затвор 2 в ходе программирования, чтобы понизить напряжение плавающего затвора, и поэтому ток ID,i(t) также снижается.

Как описано выше, детектор тока 9 контролирует ток ID,i(t) стока во время программирования i-го порогового уровня.

Когда контролируемая величина достигает эталонного тока IREF, как показано на фиг. 3D, программирование i-го порогового уровня считается завершенным и выводится сигнал VST остановки программирования, как показано в фиг. 3E. Детектор тока 9 контролирует ток ID,i(t), что, как показано на фиг. 3C и 3G, может быть описано контролированием изменения напряжения или величины заряда в плавающем затворе 2 во время программирования.

Как показано на фиг. 3C, напряжение плавающего затвора достигает эталонного напряжения V

Как показано на фиг. 2, сигнал VST остановки программирования подается на источники 6 и 7 первого и второго напряжений, которые останавливают подачу напряжений VC,i и VD на управляющий затвор 1 и сток 5 в ответ на сигнал VST остановки программирования, как показано в фиг. 3B. Другими словами, если ток ID,i(t) меньше эталонного тока IREF при t = tP,i, то программирование i-го уровневого порога завершается. Поэтому время tP,i обозначает момент программирования i-го порогового уровня.

На фиг. 3F показано изменение пороговых напряжений V

На фиг. 3F изображено повышение порогового напряжения V

На фиг. 3G представлен график изменения заряда в плавающем затворе 2 от первоначальной величины заряда QF,0 (O) в плавающем затворе 2 до величины QF,1 (tP,1), когда программирование первого порогового уровня завершено, и величина заряда QF,2 (tP,2), когда программирование второго порогового уровня завершено, в случае первого и второго пороговых уровней. Как показано в фиг. 3G, величина заряда в плавающем затворе 2 увеличивается с первоначальной величины QF,0 (0) до соответствующих величин заряда QF,1(tP,1) и QF,2 (tP,2), когда напряжения VF,1(t) и VF,2(t) (где t = tP,1 и t = tP,2) на плавающем затвор 2 достигают эталонного напряжения V

Со ссылками на фиг. 5A будет описана взаимосвязь между напряжением VC,1, прикладываемым к управляющему затвору 1, и пороговым напряжением соответствующего уровня; эта взаимосвязь представляется значительным результатом, полученным при создании изобретения.

На фиг. 5A показана эквивалентная принципиальная схема, изображающая электрическую емкость ячейки ЭСППЗУ фиг. 1A. На фиг. 5A Cc обозначает электрическую емкость между управляющим затвором 1 и плавающим затвором 2: CD - емкость между стоком 5 и плавающим затвором 2, и CS - емкость между истоком (включая подложку) и плавающим затвором 2.

Сумма CT емкостей может быть записана следующим образом:

CT = CC + CD + CS (1)

Коэффициенты связи каждой емкости определяются следующим образом:

ac = Cc/CT, aD = CD/CT, aS = CS/CT (2)

Согласно фиг. 5A, напряжение на плавающем затворе 2 при программировании в общем виде записывается следующим образом:

где символ QF(t) обозначает величину заряда в плавающем затворе 2 в момент t.

При программировании пороговое напряжение V

V

Другими словами, V

Пороговое напряжение V

V

Пороговое напряжение V

Таким образом, напряжение VF (tP) плавающего затвора 2, когда программирование порогового уровня завершено, записывается следующим образом:

VF(tp) = V

После преобразования уравнения (5) напряжение VС, подаваемое от источника первого напряжения 6 на управляющий затвор 1, определяется следующей формулой:

VC= V

где

V1 = [VREF - aDVD - aSVS]/aC (7)

При регулировании трех параметров: напряжения VD, напряжения истока VS и эталонного напряжения V

Однако, как это видно из уравнения (5), напряжение стока VD и напряжение истока VS должны иметь одинаковую величину в конечный момент программирования соответствующих уровней. Другими словами, хотя напряжение VD стока и напряжение VS истока могут быть переменными величинами, отличающимися друг от друга в соответствии с временем программирования, указанная цель может быть достигнута только тогда, когда будет обеспечено, что эти величины будут равными в конечный момент программирования.

В уравнении (7), если коэффициенты связи aD и aS значительно меньше коэффициента связи aC, то два члена с коэффициентами связи aD и aS можно не учитывать.

В уравнении (5) величина напряжения VC на управляющем затворе соответствующих уровней может изменяться во времени. В этом случае величина напряжения VC соответствующих уровней является величиной конечного момента программирования соответствующих уровней.

Величина V1 устанавливается постоянной относительно каждого уровня программирования, как описано выше, поэтому напряжение VC,i управляющего затвора, требуемое для программирования i-го порогового уровня, выражается уравнением (8) посредством уравнения (7):

VC,i = VTH,i + V1 (где i = 0, 1, 2, 3,...n - 1) (8)

Из уравнения (8) следует, что программируемые пороговые уровни и напряжение управляющего затвора, соответствующее им, имеют линейную зависимость с крутизной, равной единице. Фиг. 5B иллюстрирует результат. Из уравнения (4) также следует, что величина заряда плавающего затвора 2 линейна относительно напряжений управляющего затвора.

Поскольку величина V1, как указано выше, постоянная, величина ΔVc,i i-го сдвига напряжения, приложенного к управляющему затвору во время многоуровневого программирования, выражается в следующем виде:

ΔVc,i= ΔV

Согласно уравнениям (8) и (9), когда величина сдвига ΔV

Поскольку эталонное напряжение V

Ниже будет описан способ определения величины напряжения VC,O и эталонного тока IREF для выполнения программирования низшего уровня.

Вначале, если определены требуемая величина низшего уровня V

Ячейка памяти регулируется до требуемой величины низшего уровня V

В изложенном выше описании величина V1 уравнения (7) фиксирована относительно программирования соответствующих уровней. Если параметры уравнения (7) регулируются для изменения величины V1 для программирования соответствующих уровней, то напряжение VC,i управляющего затвора и соответствующее пороговое напряжение V

Излагаемые здесь принципы данного изобретения объясняются независимо от механизма программирования. Таким образом, можно сделать вывод о том, что принципы данного изобретения применимы к механизму программирования любой системы, описываемой уравнением (3).

Если используется система горячая инжекция носителей заряда, то напряжение истока заземляется, а напряжение стока и управляющего затвора прилагаются с положительным потенциалом, достаточно высоким, чтобы обеспечить программирование горячей инжекцией носителей заряда. При этом ток протекает между стоком 5 и истоком 3, и этот ток программирования контролируется, чтобы завершить программирование, когда ток достигает эталонного тока.

При использовании системы тунеллирования положительное напряжение прикладывается к управляющему затвору 1, а отрицательное (или нулевое) напряжение прикладывается к стоку 5 и истоку 3. В результате этого прикладывается электрическое поле, достаточное для возникновения эффекта тунеллирования между плавающим затвором 2 и стоком 5, истоком 3 или канальной областью 4. В этом случае напряжение стока превышает напряжение истока, тем самым создавая току возможность протекания между стоком 5 и истоком 3. Ток контролируется, чтобы завершить программирование, когда ток достигнет эталонного тока IREF. Если на сток 5 или исток 3 подается отрицательное напряжение, то, когда сток 5 и исток 3 являются областями полупроводниковой легирующей примеси n-типа, а подложка является полупроводником p-типа, на подложку подается меньшее или равное напряжение.

До сих пор описывался двухуровневый или многоуровневый способ программирования. Далее поясняется способ стирания, использующий изложенную выше систему программирования.

При стирании на соответствующие точки ячейки подаются напряжения для приложения электрического поля, достаточно сильного, чтобы стереть носители заряда между плавающим затвором 2 и истоком 3, стоком 5 или канальной областью 4, и тем самым при помощи туннелирования стереть носители заряда к истоку 3, стоку 5 или канальной области 4. В соответствии с данным изобретением стертое состояние обозначает низший пороговый уровень, т.е. V

Во-первых, пороговые уровни всех ячеек в выбранном блоке стираются до уровня ниже нуля, т.е. ниже V

Здесь величину VC,0 можно установить на необходимое значение, как указано выше. Поскольку состояние стирания достигается изложенным выше механизмом программирования, может быть решена проблема избыточного стирания.

Изложенный выше метод программирования в соответствии с данным изобретением имеет следующие преимущества.

Во-первых, многоуровневое программирование легко выполняется, так как для каждого программирования соответствующих пороговых уровней изменяется только напряжение управляющего затвора.

Во-вторых, соответствующие уровни порогового напряжения и соответствующие им напряжения управляющего затвора, относящиеся к ним, имеют линейную взаимосвязь друг с другом, и величина сдвига порогового напряжения та же, что и величина сдвига напряжения управляющего затвора, тем самым создается возможность точной регулировки сдвига порогового напряжения соответствующих уровней.

В-третьих, поскольку стертое состояние регулируется дополнительным напряжением управляющего затвора с программированием низшего уровня, проблемы избыточного стирания в сущности не возникает.

В-четвертых, ячейка ЭСППЗУ характеризуется одновременным выполнением программирования и считывания и поэтому отдельная схема для контролирования программированного содержания не нужна, и вследствие этого скорость программирования увеличивается.

В-пятых, предшествующее программирование перед выполнением стирания не требуется.

В-шестых, точность многоуровневого программирования, т.е. распределение погрешностей программирования пороговых напряжений, точно определяется параметрами, установленными при изготовлении энергонезависимой памяти, и приложением напряжения смещения. Поэтому распределение погрешностей порогового напряжения соответствующих уровней энергонезависимой памяти в соответствии с данным изобретением не зависит от неоднократных циклов программирования/стирания. Помимо этого, программирование выполняется независимо от захвата заряда, подвижности носителей заряда в канале, сопротивления разрядной шины и нестабильности или допусков электрических компонентов.

В-седьмых, поскольку программирование энергонезависимой памяти в соответствии с данным изобретением осуществляется способом, использующим управление напряжением, посредством приложения напряжения к управляющему затвору, то многоуровневое программирование может выполняться легче и точнее, чем в случае способа, использующего управление током.

Специалистам в данной области будет очевидно, что при способе программирования энергонезависимой памяти в соответствии с данным изобретением могут быть осуществлены различные модификации и изменения в пределах объема и без изменения сущности данного изобретения. Данное изобретение включает в себя модификации и варианты при условии, что они находятся в пределах формулы изобретения и ее эквивалентов.

Изобретение относится к способам программирования запоминающего устройства и позволяет обеспечить одновременный контроль пороговых уровней при выполнении двухуровневого или многоуровневого программирования. Способ предназначен для программирования ячейки энергонезависимой памяти, которая имеет управляющий затвор, плавающий затвор, сток, исток и канальную область. Способ включает подачу первого напряжения к управляющему затвору, второго напряжения - к стоку и третьего - к истоку. Второе напряжение превышает третье. Способом предусмотрен контроль тока между стоком и истоком. При достижении током заданной величины завершают программирование на двух первых уровнях. 3 с. и 15 з.п. ф-лы, 5 ил.

| US, патент, 5422842, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| US, патент, 5043940, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1998-05-20—Публикация

1996-01-24—Подача