Изобретение относится к электронике и предназначено для использования в синхронных оперативных запоминающих устройствах.

Известны синхронные оперативные запоминающие устройства, см. например, Игнатьев С.М. Николаенко А.В. Савенков В.Н. Двухпортовое оперативное ЗУ типа К1627РП2В с широкими функциональными возможностями. Электронная промышленность. 1993, вып. 3, с. 48 52, рис. 1, в составе которых содержаться формирователи импульсов записи, определяющие начало и продолжительность информационных воздействий на выбираемые для записи элементы памяти. Стартовым сигналом для формирователей является спад синхроимпульсов, фиксирующий состояние входных триггеров адреса записи и данных.

Недостаток подобных устройств состоит в том, что временные позиции импульсов записи, оптимальные с точки зрения быстродействия и надежности функционирования в режиме записи, должен обеспечивать формирователь импульсов. Это значительно усложняет электрическую схему и затрудняет проектирование.

Устранить данный недостаток позволяет использование в синхронном запоминающем устройстве схемы записи, выполненной в соответствии [2] В таком запоминающем устройстве информационные сигналы записи селективно поступают в элементы памяти через дешифраторы выборки столбцов аналогично адресным сигналам, чем обеспечивается необходимое совпадение начала записи с завершением выборки и окончания записи с началом выборки другого адреса. Это устройство по технической сущности наиболее близко к данному изобретению.

Наиболее близкий аналог содержит матрицу элементов 1 памяти, первый 3 и второй 4 дешифраторы выборки столбцов. Входы элементов 1 памяти, составляющих строки матрицы, являются входами 7 выборки устройства. Входы первого 3 и второго 4 дешифраторов выборки столбцов являются адресными входами 8 устройства, а их дополнительные входы соответственно прямым 9 и инверсным 10 информационными входами устройства. Выходы первого 3 и второго 4 дешифраторов выборки столбцов соответственно подключены к первым и вторым информационным входам столбцов матрицы элементов 1 памяти.

Устройство-аналог работает следующим образом.

В режиме записи информации на вход 7 выборки, соответствующий строке, содержащей нужный элемент 1 памяти, поступает сигнал выборки, в то же время через соответствующие адресные 8 и информационные 9 и 10 входы устройства в дешифраторы 3 и 4 выборки столбцов поступают информационный и адресный сигналы, обуславливая появление сигнала записи на одном из информационных входов столбца матрицы, содержащего выбираемый для записи элемент 1 памяти. В результате этого элемент 1 памяти, одновременно принадлежащий выбранной строке и столбцу матрицы, подвергается совместному воздействию сигнала выборки и информационного сигнала и принимает требуемое состояние.

Достоинством описанного устройства является высокая синхронность начала воздействий на элемент 1 памяти по входам 8 выборки и информационным входам 9 и 10 при одновременном переключении соответствующих сигналов. Синхронность достигается благодаря распространению информационного сигнала через цепи дешифраторов 3 и 4 выборки столбцов, обеспечивающему равенство задержки информационных сигналов от момента появления на входах 9 и 10 и задержки сигнала выборки относительно адресных входов 7.

Недостатком устройства является его низкая помехозащищенность при нарушении одновременности смены сигналов адреса и данных на входах 8, 9 и 10. Опережение информационными сигналами на входах 9 и 10 сигналов адреса или проникновение на входы 7 ложных сигналов адреса во время записи способны нарушить сохраняемую в матрице информацию.

Задачей изобретения является устранение данного недостатка.

Поставленная задача решается за счет того, что в запоминающем устройстве, содержащем матрицу элементов памяти, первой и второй дешифраторы выборки столбцов, выходы которых соответственно подключены к прямым и инверсным информационным входам столбцов матрицы элементов памяти, по одному входу у первого и второго дешифраторов выборки столбцов подключено к инверсному и прямому информационным входам устройства соответственно, а остальные входы соединены с соответствующими адресными входами устройства, дешифраторы выборки столбцов имеют по одному входу запрета, которые подключены к входу синхронизации устройства.

Указанное выполнение запоминающего устройства позволяет посредством введения новых признаков обеспечить блокировку выходов дешифраторов выборки столбцов на время установки входных сигналов адреса и данных и тем самым исключить возможность ложной записи.

Отличительными признаками изобретения, позволившими получить новый технический результат, являются дополнение каждого из дешифраторов выборки столбцов одним входом запрета и подключение их к входу синхронизации устройства.

Проведенные патентные исследования подтвердили новизну изобретения, а также показали, что в литературе отсутствуют данные, указывающие на влияние отличий патентуемого изобретения на достижение технического результата. Поэтому следует считать, что патентуемое изобретение соответствует критериям новизны и изобретательского уровня.

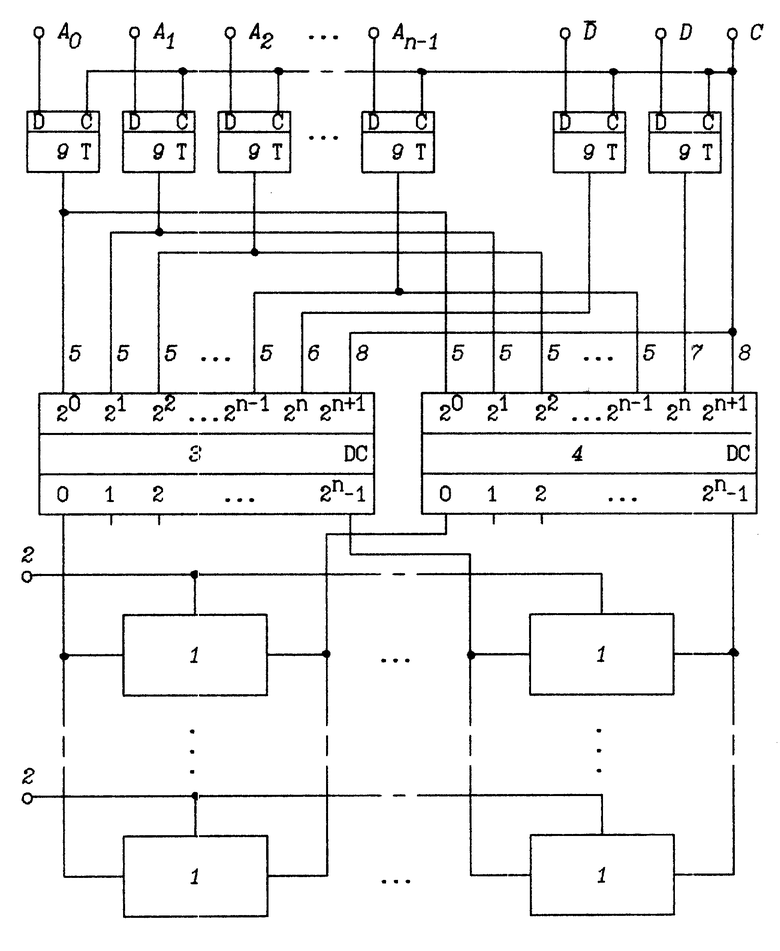

На чертеже изображена структурная схема запоминающего устройства.

Запоминающее устройство содержит матрицу элементов 1 памяти, входы выборки которых в каждой строке матрицы объединены и являются входами 2 выборки устройства, первый 3 и второй 4 дешифраторы выборки столбцов. В качестве дешифраторов 3 и 4 выборки столбцов в устройстве можно использовать неполные дешифраторы с разрядностью n+2, где n число разрядов кода адреса столбца матрицы. При этом каждый дешифратор 3 и 4 реализует четверть младших выходных кодов с нулевого до 2n-1. Таким образом, наличие логической единицы хотя бы на одном из старших входов 2n и 2n+1 приведет к формированию нулей на всех выходах, равносильному выполнению операции ЗАПРЕТ. Входы 20, 21, 22, 2n-1 дешифраторов 3 и 4 выборки столбцов являются адресными входами 5 устройства, а их дополнительные входы 2n -соответственно инверсным 6 и прямым 7 информационными входами устройства. Входы 2n+1 дешифраторов 3 и 4 соединены с входом 8 синхронизации устройства. Выходы дешифраторов 3 и 4 выборки столбцов соответственно подключены к прямым и инверсным информационным входам столбцов матрицы элементов 1 памяти. На выходах 5, 6 и 7 синхронного запоминающего устройства установлены D-триггеры 9, синхровходы С которых подключены к входу 8 синхронизации устройства, а на информационные входы D поступают соответствующие разряды A0 An-1 адресного кода и входные данные  и D.

и D.

Устройство работает следующим образом.

Выполнение каждого акта записи информации в конкретный элемент 1 памяти начинается с переключения логического сигнала на входе 8 с уровня нуля на уровень единицы. При этом триггеры 9 приобретают способность принимать состояния, соответствующие логическим сигналам, поступающим на входы D и определяющим записываемые данные и адрес столбца матрицы, содержащего нужный элемент 1 памяти. На всех выходах дешифраторов 3 и 4 устанавливаются логические нули, что прекращает всякое информационное воздействие на прежде выбранный элемент 1 памяти и он переходит в режим хранения. Затем уровень на входе 8 переходит в нулевое значение, фиксирующее состояния триггеров 9 и снимающее запрет с выходов дешифраторов 3 и 4. В это же время на вход 2 выборки, соответствующий строке, содержащей записываемый элемент 1 памяти, поступает сигнал выборки. Элемент 1 памяти, принадлежащий выбранной строке и столбцу матрицы и одновременно получающий воздействие сигнала выборки и информационное воздействие, приобретает требуемое состояние.

Для считывания информации в начале актов обращения на информационные входы 6 и 7 поступают логические нули, что приводит к формированию сигналов единичного уровня на информационных входах выбираемого столбца, принадлежащий ему элемент 1 памяти, получающий также сигнал выборки с входа 2, оказывается в режиме считывания.

Высокая помехозащищенность запоминающего устройства достигается благодаря обеспечению блокировки информационного воздействия на элементы 1 памяти с выходов дешифраторов 3 и 4 выборки столбцов на время установки входных сигналов адреса и данных. Необходимое для исключения ложной записи опережение сигналами выборки сигналов записи обеспечивается предустановом сигналов адреса и данных на выходах 5, 6 и 7 относительно синхросигнала на входе 8 и идентичностью трактов их распространения до выбираемых элементов 1 памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| БАЗОВЫЙ МАТРИЧНЫЙ КРИСТАЛЛ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1992 |

|

RU2089012C1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1992 |

|

RU2042216C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ЗАПИСИ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1994 |

|

RU2097843C1 |

| ПРЕОБРАЗОВАТЕЛЬ ДЛИТЕЛЬНОСТЬ-КОД | 2001 |

|

RU2210097C2 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1993 |

|

RU2069018C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2018979C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1991 |

|

RU2020614C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1991 |

|

RU2024048C1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

Изобретение относится к электронике и предназначено для использования в синхронных оперативных запоминающих устройствах. Его задачей является повышение помехозащищенности запоминающего устройства в режиме записи при нарушении одновременности смены сигналов на адресных и информационных входах 5, 6 и 7. Задача решается дополнением каждого из дешифраторов 3 и 4 выборки столбцов одним входом запрета и подключением их к входу 8 синхронизации устройства, что обеспечивает блокировку выходов дешифраторов 3 и 4 на время установки входных сигналов адреса и данных и этим исключает возможность ложной записи. На схеме запоминающего устройства обозначены также элементы 1 памяти, входы 2 выборки устройства и входные D-триггеры 9. 1 ил.

Запоминающее устройство, содержащее матрицу элементов памяти, первый и второй дешифраторы выборки столбцов, выходы которых соответственно подключены к прямым и инверсным информационным входам столбцов матрицы элементов памяти, по одному входу у первого и второго дешифраторов выборки столбцов подключено к инверсному и прямому информационным входам устройства соответственно, а остальные входы соединены с соответствующими адресными входами устройства, отличающееся тем, что дешифраторы выборки столбцов имеют по одному входу запрета, которые подключены к входу синхронизации устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Алексеенко А.Г., Шагурин И.И | |||

| Микросхемотехника | |||

| - М.: Радио и связь, 1982, 246-248, рис.7.1 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| SU, авторское свидетельство, 1203592, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1998-01-10—Публикация

1995-04-21—Подача