Изобретение относится к запоминающим устройствам на биполярных транзисторах.

Известен матричный накопитель, содержащий элементы памяти, каждый из которых состоит из двух транзисторов с перекрестно связанными базовыми и коллекторными выводами [1] . Недостатком подобных устройств является их низкая надежность функционирования, связанная с наличием однофазного выхода считываемой информации, что приводит к нарушению адекватности приема выходных данных последующими логическими каскадами при возникновении рассогласования уровня опорного напряжения считывания с уровнями логических напряжений в выбранном элементе памяти, обусловленного разбросом параметров компонентов матричного накопителя.

Наиболее близким к изобретению по технической сущности и достигаемому эффекту является матричный накопитель [2], в котором влияние разброса параметров элементов памяти уменьшено за счет использования парафазного принципа формирова- ния выходного информационного сигнала. Устройство-прототип содержит группу элементов памяти и буферный элемент, состоящий из первого и второго транзисторов связи и первого и второго нагрузочных резисторов, причем эмиттер первого транзистора связи соединен с первыми входами управления элементов памяти и является первым входом выборки устройства, а коллектор подключен к первому выводу первого нагрузочного резистора и к первому информационному выходу устройства, эмиттер второго транзистора связи соединен с вторыми входами управления элементов памяти и является вторым входом выборки устройства, а коллектор подключен к первому выводу второго нагрузочного резистора и к второму информационному выходу устройства, вторые выводы нагрузочных резисторов подключены к шине нулевого потенциала, а базы транзисторов связи соединены с входами управления матричного накопителя, входы выборки элементов памяти подключены к соответствующим входам словарной выборки устройства. Каждый элемент памяти состоит из первого и второго ключевых транзисторов с эмиттерами управления и хранения, соединенных двумя перекрестными связями база-коллектор, третьего и четвертого нагрузочных резисторов, первые выводы которых соответственно подключены к коллекторам первого и второго ключевых транзисторов, а вторые выводы соединены и являются входом выборки элемента памяти, при этом эмиттеры хранения первого и второго ключевых транзисторов объединены и являются входом тока хранения, а эмиттеры управления являются соответственно первым и вторым входами управления элемента памяти.

В режиме хранения информации состояния элементов памяти поддерживаются за счет протекания в них тока, поступающего по входам тока хранения.

В режиме записи информации выборка нужного элемента памяти осуществляется посредством повышения потенциала на соответствующем входе словарной выборки и включения тока записи в один из входов выборки. Ток записи включается в тот вход выборки, к которому подключен эмиттер управления ключевого транзистора выбранного элемента памяти, у которого в соответствии с поступающей информацией в результате записи на базе должен установиться высокий логический потенциал. Среди транзисторов, эмиттеры которых подключены к входу выборки с включенным током записи, самый высокий потенциал на базе имеет ключевой транзистор выбранного элемента памяти при любом его состоянии. Для обеспечения такого положения рассматриваемого базового уровня логический перепад на входах словарной выборки имеет величину, позволяющую низкому базовому уровню в выбранном элементе памяти превышать высокие базовые уровни в невыбранных элементах памяти, а на базе соответствующего транзистора связи в режиме записи устанавливается достаточно низкий уровень управляющего напряжения. Происходящее в описанных условиях включение тока записи в ключевой транзистор выбранного элемента памяти приводит к установке последнего в требуемое состояние.

В режиме считывания информации выборка элемента памяти производится повышением потенциала на соответствующем входе словарной выборки и включением двух токов считывания в оба соответствующих входа выборки. На базах транзисторов связи при этом устанавливаются одинаковые напряжения, уровень которых лежит между высоким и низким базовыми уровнями ключевых транзисторов выбранного элемента памяти. В таких условиях из двух токов считывания один протекает в эмиттер ключевого транзистора выбранного элемента памяти с высоким базовым уровнем, а другой - в эмиттер транзистора связи. Наличие тока в коллекторе одного транзистора связи при отсутствии тока в коллекторе другого приводит к формированию на информационных выходах дифференциального логического сигнала, соответствующего состоянию выбранного элемента памяти.

Устройство-прототип обладает рядом недостатков, негативно сказывающихся на его работе в режиме считывания. Первый недостаток заключается в низкой надежности функционирования, что обусловлено недостаточно высоким перепадом уровней напряжений на базах закрытого ключевого транзистора выбранного элемента памяти и соответствующего ему транзистора связи. Величина этого перепада в условиях воздействия различных дестабилизирующих факторов может быть недостаточной для того, чтобы исключить самопроизвольное включение тока считывания в эмиттер закрытого ключевого транзистора, приводящее к несанкционированному опрокиды- ванию выбранного элемента памяти. Второй и третий недостатки проявляются при смене считываемых элементов памяти и состоят в большой задержке формирования на выходах новой информационной разности потенциалов и затянутости этого процесса. В результате устройство-прототип имеет низкое быстродействие в режиме считывания и при смене адреса в течение довольно длительного периода имеет на выходах неопределенный логический сигнал, что способствует возникновению помех. Данные недостатки вызваны процессами переключения напряжений на узлах входов управления, элементов памяти, обладающих высокой емкостью, складываемой из эмиттерных емкостей ключевых транзисторов. Проявление этих недостатков возрастает при увеличении информационного объема матричного накопителя. Последнее утверждение справедливо и для первого недостатка, так как при увеличении размеров и количества компонентов влияние дестабилизирующих факторов тоже усиливается.

Целью изобретения является повышение быстродействия, помехоустойчивости и надежности работы матричного накопителя в режиме считывания информации.

С этой целью в матричном накопителе, содержащем группу элементов памяти и буферный элемент, состоящий из первого и второго транзисторов связи и первого и второго нагрузочных резисторов, эмиттер первого транзистора связи соединен с первыми входами управления элементов памяти и является первым входом выборки устройства, а коллектор подключен к первому выводу первого нагрузочного резистора, эмиттер второго транзистора связи соединен с вторыми входами управления элементов памяти и является вторым входом выборки устройства, а коллектор подключен к первому выводу второго нагрузочного резистора, входы выборки элементов памяти подключены к соответствующим входам словарной выборки устройства, первый и второй транзисторы связи соединены двумя перекрестными связями база-коллектор, а вторые выводы первого и второго нагрузочных резисторов подключены соответственно к первому и второму входам управления устройства.

Заявляемое техническое решение отличается от прототипа связями, следовательно, оно отвечает критерию "новизна".

Положительный эффект изобретения достигается благодаря тому, что задерживающее влияние процесса переключения узловых напряжений входов управления снижено за счет уменьшения перепада напряжений на этих узлах, ускорению процесса формирования выходного информацион- ного сигнала за счет введения порогового триггерного характера работы буферного элемента и увеличению разности потенциалов между базой закрытого ключевого транзистора выбранного элемента памяти и базой соответствующего транзистора связи.

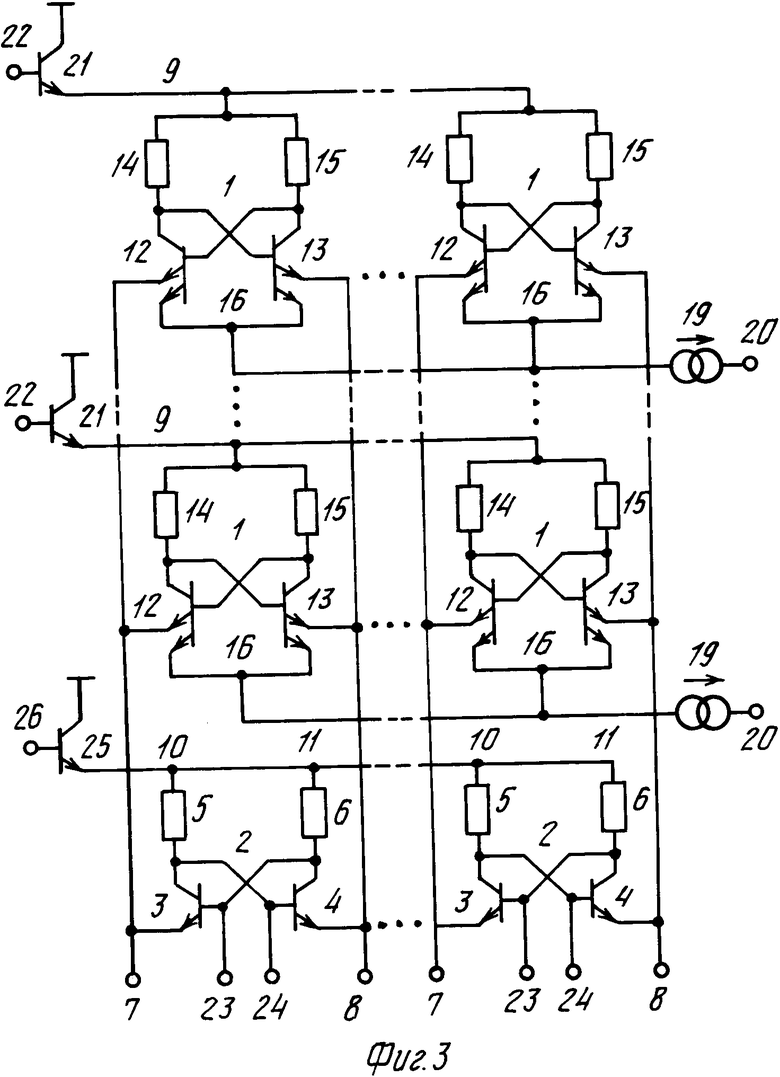

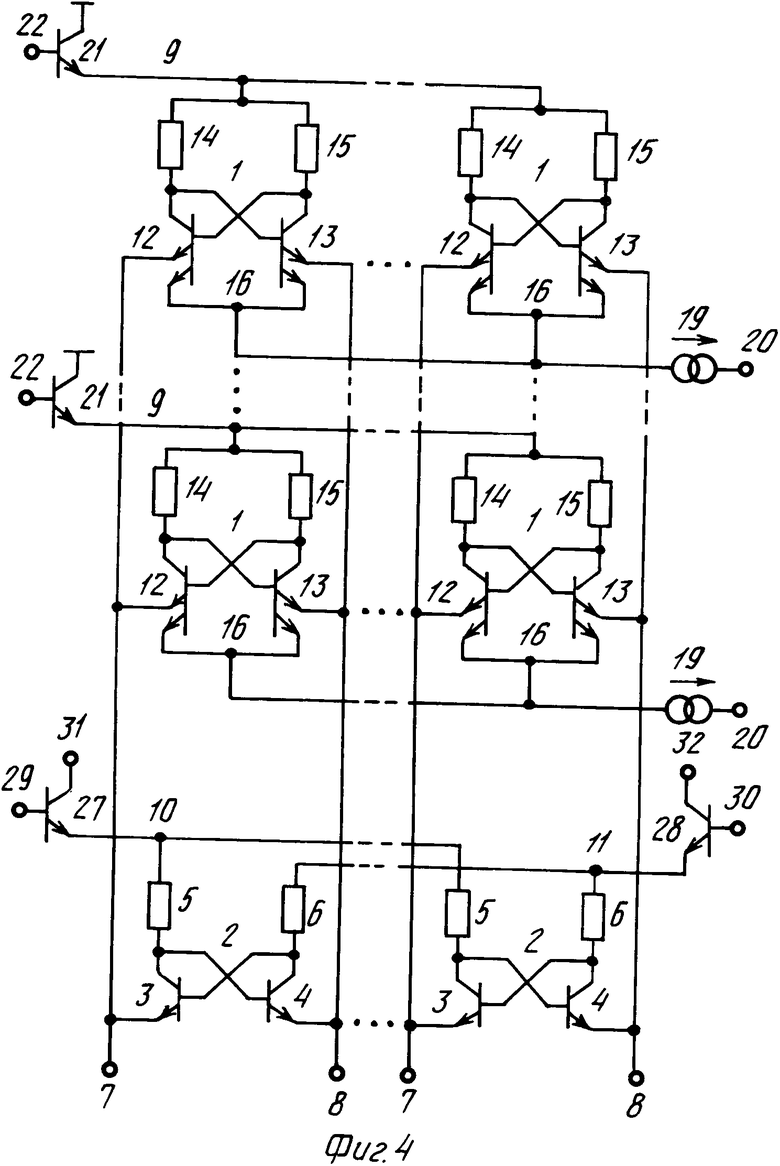

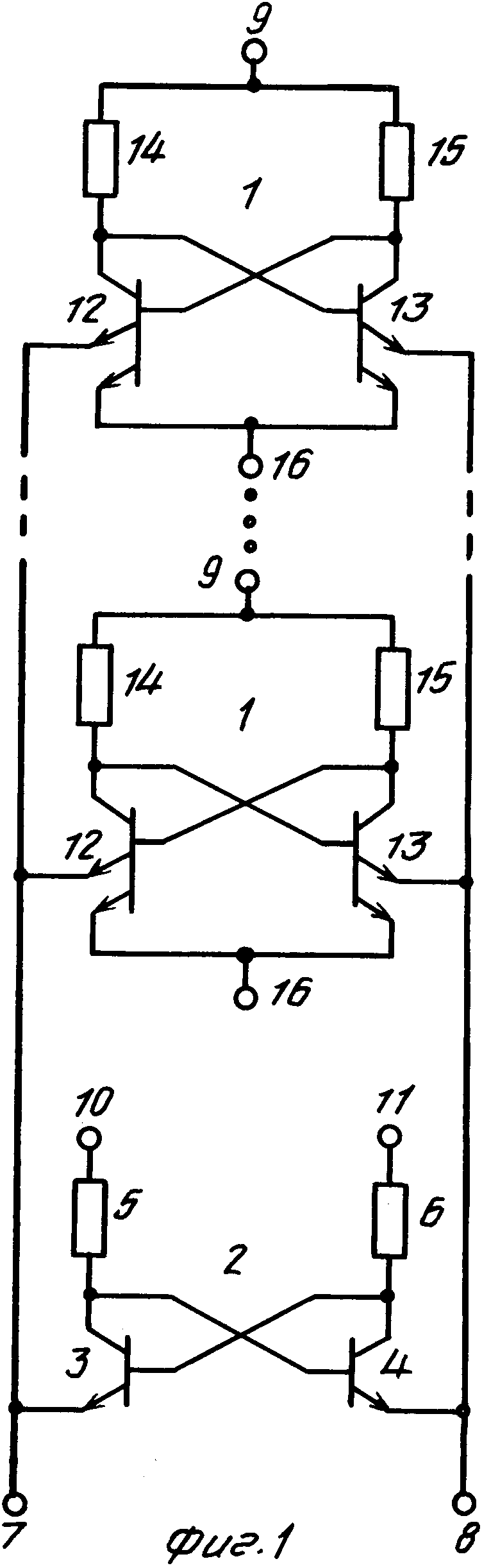

На фиг. 1 изображена принципиальная электрическая схема матричного накопителя; на фиг. 2 - временная диаграмма узловых напряжений в накопителе при смене элементов памяти; на фиг.3 и 4 - варианты его использования в запоминающих устройствах с потенциальной и токовой формами выходных информационных сигналов соответственно.

Матричный накопитель содержит группу элементов 1 памяти и буферный элемент 2, состоящий из первого и второго транзисторов 3 и 4 связи и первого и второго нагрузочных резисторов 5 и 6. Эмиттер первого транзистора 3 связи соединен с первыми входами управления элементов 1 памяти и является первым входом 7 выборки накопителя, а коллектор подключен к первому выводу первого нагрузочного резистора 5. Эмиттер второго транзистора 4 связи соединен с вторыми входами управления элементов 1 памяти и является вторым входом 8 выборки накопителя, а коллектор подключен к первому выводу второго нагрузочного резистора 6. Входы выборки элементов 1 памяти подключены к соответствующим входам 9 словарной выборки накопителя. Первый и второй транзисторы 3 и 4 связи соединены двумя перекрестными связями база-коллектор, а вторые выводы первого и второго нагрузочных резисторов 5 и 6 подключены соответственно к первому и второму входам 10 и 11 управления накопителя. Каждый элемент 1 памяти состоит из первого и второго ключевых транзисторов 12 и 13 с эмиттерами управления и хранения, соединенных двумя перекрестными связями база-коллектор, третьего и четвертого нагрузочных резисторов 14 и 15, первые выводы которых соответственно подключены к коллекторам первого и второго ключевых транзисторов 12 и 13, а вторые выводы соединены и являются входом выборки элемента 1 памяти. Эмиттеры хранения первого и второго ключевых транзисторов 12 и 13 объединены и являются входом 16 тока хранения, а эмиттеры управления являются соответственно первым и вторым входами управления элемента 1 памяти.

Матричный накопитель работает следующим образом.

Каждый элемент 1 памяти представляет собой триггер, имеющий два устойчивых состояния, которые условно различаются наличием открытого состояния у одного из двух ключевых транзисторов 12 и 13. Состояние элементов 1 памяти поддерживаются благодаря протеканию в них току, поступающему через входы 16 тока хранения. Ток хранения, протекая через открытый ключевой транзистор 12 или 13 в соответствующий ему нагрузочный резистор 14 или 15, создает на этом резисторе падение напряжения, что при отсутствии падения напряжения на другом нагрузочном резисторе 14, 15 приводит к формированию разности потенциалов на базах ключевых транзисторов 12 и 13, обеспечивающей устойчивое распределение тока хранения между их эмиттерами хранения.

В режиме записи информации выборка нужного элемента 1 памяти осуществляется посредством повышения потенциала на соответствующем входе 9 словарной выборки и включения тока записи в один из входов 7 или 8 выборки. Ток записи включается в тот вход 7, 8 выборки, к которому подключен эмиттер управления ключевого транзистора 12 или 13 выбранного элемента 1 памяти, у которого в соответствии с поступающей информацией в результате записи на базе должен установиться высокий логический потенциал. Среди транзисторов 3, 4, 12, 13, эмиттеры которых подключены к входу 7, 8 выборки с включенным током записи, самый высокий потенциал на базе имеет ключевой транзистор 12, 13 выбранного элемента 1 памяти при любом его состоянии. Для обеспечения такого положения рассматриваемого базового уровня логический перепад на входах 9 словарной выборки имеет величину, позволяющую низкому базовому уровню в выбранном элементе 1 памяти превышать высокие базовые уровни в невыбранных элементах 1 памяти, а на базе соответствующего транзистора 3, 4 связи в режиме записи устанавливается достаточно низкий уровень напряжения посредством снижения напряжения на соединенном с его базой входе 10, 11 управления накопителя. Происходящее в описанных условиях включение тока записи в ключевой транзистор 12, 13 выбранного элемента 1 памяти приводит к установке его в требуемое состояние.

В режиме считывания информации выборка элемента 1 памяти производится повышением потенциала на соответствующем входе 9 словарной выборки и включением двух токов считывания в оба соответствующих входа 7 и 8 выборки. На входах 10 и 11 управления при этом устанавливается напряжение, равное напряжению на выбранном входе 9 словарной выборки. В таких условиях один из токов считывания, включенный в тот вход 7, 8 выборки, который подключен к эмиттеру ключевого транзистора 12, 13 выбранного элемента 1 памяти с низким базовым уровнем, ответвляется в соответствующий транзистор 3 или 4 связи, а другой ток считывания полностью ответвляется в ключевой транзистор 12, 13 выбранного элемента 1 памяти с высоким базовым уровнем, так как после включения тока считывания в буферный элемент 2 возникающее на проводящем его нагрузочном резисторе 5 или 6 падение напряжения приводит к снижению базового уровня транзистора 3 или 4 связи, составляющего эмиттерно связанную пару открытому ключевому транзистору 12, 13 выбранного элемента 1 памяти. Наличие тока в коллекторе одного транзистора 3, 4 связи при отсутствии тока в коллекторе другого является признаком идентификации логического состояния выбранного элемента 1 памяти, который может быть воспринят последующими устройствами либо в форме дифференциального потенциального сигнала с коллекторов транзисторов 3, 4 связи, либо в виде дифференциального токового сигнала с входов 10, 11 управления.

Главной причиной нарушения нормальной работы накопителя в режиме считывания является самопроизвольное включение тока считывания в эмиттер управления ключевого транзистора 12, 13 выбранного элемента 1 памяти с низким уровнем напряжения на базе. Данное переключение может произойти в результате воздействия каких-либо помех или в результате отклонений параметров компонентов от номинала. Устойчивость к описанному негативному явлению определяет величина перепада напряжений между базой закрытого ключевого транзистора 12, 13 выбранного элемента 1 памяти и базой соответствующего транзистора 3, 4 связи, который в данном матричном накопителе увеличен до максимально возможной величины и при эквивалентности нагрузочных резисторов 5, 6 и 14, 15 равняется перепаду базовых напряжений в выбранном элементе 1 памяти, ограниченному величиной напряжения насыщения база-коллектор транзисторов.

При считывании информации из матричного накопителя в целях достижения минимальной задержки выборки допускается смена элементов 1 памяти, не выходя из режима считывания. Для пояснения работы накопителя в процессе смены элементов 1 памяти на фиг.2 изображены кривые изменения напряжений на базах эмиттерно связанных транзисторов: Uб12, Uб12′ первых ключевых транзисторов 12 прежде выбранного и выбираемого элементов 1 памяти и Uб3 первого транзистора 3 связи, Uб13, Uб13′ вторых ключевых транзисторов 13 прежде выбранного и выбираемого элементов 1 памяти и Uб4 второго транзистора 4 связи, а также напряжения U7 и U8 соответствующих эмиттерным узлам названных транзисторов.

Предположим для определенности, что в прежде выбранном элементе 1 памяти высокий уровень напряжения на базе транзистора 12 - Uб12, а в выбираемом - на базе транзистора 13 - Uб13′. При снижении напряжения на базе транзистора 12, вызванного переключением напряжения на входе 9 словарной выборки с уровня выборки в невыбранный уровень, по достижении уровня на базе транзистора 3 связи (точка 17) ток входа 7 переключается в эмиттер транзистора 3 и начинает протекать в соединенном с его коллектором резисторе 5, вызывая понижение уровня напряжения на базе транзистора 4. Падающий базовый потенциал транзистора 4 достигает уровня повышающегося базового потенциала Uб13′ транзистора 13 выбираемого элемента 1 памяти в точке 18, в результате чего ток входа 8 переключается из транзистора 4 в транзистор 13. Вызванное этим процессом уменьшение падения напряжения на резисторе 6 приводит к повышению потенциала на базе транзистора 3 связи.

Высокое быстродействие матричного накопителя при смене элементов 1 памяти в режиме считывания достигается благодаря тому, что при обеспечении равенства высоких уровней базовых напряжений в выбранном элементе 1 памяти и в буферном элементе 2 напряжения в узлах входов 7 и 8 выборки в установившемся режиме имеют одинаковые уровни напряжений, не зависящие от состояния выбранного элемента 1 памяти. Это обстоятельство позволяет уменьшить вклад процессов переключения емкости узлов входов 7, 8 в задержку переходных процессов при смене элементов 1 памяти.

Рассматриваемый матричный накопитель может иметь не только линейную, но и двумерную организацию. В этом случае он содержит несколько групп элементов 1 памяти, каждая из которых составляет отдельный столбец, содержащий, кроме того, соответствующий буферный элемент 2 (фиг.3). Элементы 1 памяти, составляющие строки матрицы, имеют общие входы 9 словарной выборки и входы 16 тока хранения, которые через источники 19 тока хранения соединены с шиной 20 питания. Входы 9 словарной выборки матричного накопителя запоминающего устройства на биполярных транзисторах обычно подключены к выходам формирователей напряжения выборки, каждый из которых состоит из усилительного транзистора 21, эмиттер которого соединен с соответствующим входом 9, а база подключена к соответствующему входу 22 формирователя напряжения выборки. Коллекторы транзисторов 19 соединены с шиной нулевого потенциала.

Если выходной сигнал матричного накопителя предусмотрено формировать в виде напряжений, первый и второй информационные выходы 23 и 24 подключаются к базам соответственно первого и второго транзисторов 3 и 4 связи. Входы 10, 11 управления буферного элемента 2 через p-n-переход эмиттер-база транзистора 25 смещения подключен к входу 26 напряжения смещения, коллектор транзистора 25 соединен с шиной нулевого потенциала. При работе накопителя в данной конфигурации на входе 26 устанавливается напряжение, равное напряжению высокого уровня на входах 22. В режиме записи информации формирование низкого уровня на базах транзисторов 3, 4 связи осуществляется включением тока в соответствующий нагрузочный резистор 5 или 6 через выход 23, 24.

Информационный сигнал матричного накопителя может быть получен и в токовой форме. Для этого первые и вторые входы 10, 11 управления соединены в два узла, которые через p-n-переходы эмиттер-база соответственно первого и второго передающих транзисторов 27 и 28 подключены к первому и второму входам 29 и 30 управляющих напряжений. Коллекторы первого и второго передающих транзисторов 27 и 28 являются соответственно первым и вторым выходами 31 и 32 информационного тока. В режиме считывания информации на входах 29 и 30 устанавливаются одинаковые напряжения, равные напряжению высокого уровня на входах 22. В режиме записи информации на одном из входов 29, 30, который соответствует базе запираемого транзистора 3, 4 связи, напряжение падает до низкого уровня на входах 22.

Таким образом, матричный накопитель обладает высоким быстродействием помехоустойчивостью и надежен в работе при считывании информации благодаря уменьшению перепада напряжений узловых емкостей входов управления элементов памяти, ускорению процесса формирования выходного информационного сигнала за счет введения триггерного порогового характера работы буферного элемента и увеличению разности потенциалов между базой закрытого ключевого транзистора выбранного элемента памяти и базой соответствующего транзистора связи. Применение данного технического решения наиболее целесообразно в микросхемах памяти средней и большой информационной емкости, например его использование в ИС ОЗУ 4 Кбит ЭСЛ-типа К1500РУ470 позволит уменьшить время выборки адреса на 15%.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2018979C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ЗАПИСИ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1994 |

|

RU2097843C1 |

| Запоминающее устройство | 1990 |

|

SU1751816A1 |

| Запоминающее устройство | 1990 |

|

SU1751814A1 |

| ВЫХОДНАЯ СХЕМА С ТРЕМЯ СОСТОЯНИЯМИ | 1992 |

|

RU2072629C1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Накопитель | 1988 |

|

SU1536442A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1573472A1 |

| Накопитель для оперативного запоминающего устройства | 1990 |

|

SU1751815A1 |

Изобретение относится к запоминающим устройствам на биполярных транзисторах. Целью является повышение быстродействия, помехоустойчивости и надежности работы матричного накопителя в режиме считывания информации, которая достигается изменением связей транзисторов 3, 4 связи и нагрузочных резисторов 5, 6 буферного элемента 2, позволяющим снизить задерживающее влияние процесса переключения узловых напряжений входов 7, 8 выборки за счет уменьшения перепада напряжений на этих узлах, ускорить процесс формирования выходного информационного сигнала за счет введения триггерного порового характера работы буферного элемента 2 и увеличить разность потенциалов между базой закрытого ключевого транзистора 12, 13 выбранного элемента 1 памяти и базой соответствующего транзистора 3, 4 связи. Кроме указанных элементов накопитель содержит резисторы 14, 15 и имеет входы 9 словарной выборки, входы 10, 11 управления и входы 16 тока хранения. 4 ил.

НАКОПИТЕЛЬ ИНФОРМАЦИИ, содержащий группу элементов памяти, каждый из которых состоит из первого и второго ключевых транзисторов, базы первого и второго ключевых транзисторов соединены соответственно с коллекторами второго и первого ключевых транзисторов, из первого и второго нагрузочных резисторов, первые выводы которых подключены соответственно к коллекторам первого и второго ключевых транзисторов, а вторые выводы соединены между собой и являются входом выборки накопителя, эмиттеры хранения первого и второго ключевых транзисторов объединены и являются входом тока хранения накопителя, буферный элемент, состоящий из первого и второго транзисторов связи и третьего и четвертого нагрузочных резисторов, эмиттеры первого и второго транзисторов связи соединены соответственно с эмиттерами управления первого и второго ключевых транзисторов и являются первым и вторым входами управления накопителя, а коллекторы первого и второго транзисторов связи подключены к первым выводам соответственно третьего и четвертого нагрузочных резисторов, отличающийся тем, что, с целью повышения быстродействия и помехоустойчивости в работе устройства, коллекторы первого и второго транзисторов связи соединены соответственно с базами второго и первого транзисторов связи, а вторые выводы третьего и четвертого нагрузочных резисторов являются соответственно третьим и четвертым входами управления накопителя.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1994-09-30—Публикация

1991-04-19—Подача