Изобретение касается криптографических преобразований и может быть использовано в связных, вычислительных и, информационных системах для криптографического закрытия двоичной информации.

Целью изобретения является шифрование информации блоками различной длины с использованием ключа такой длины, которая обеспечивает невозможность его опробования за разумное время.

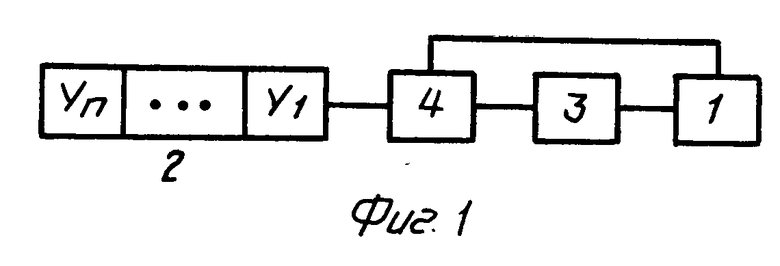

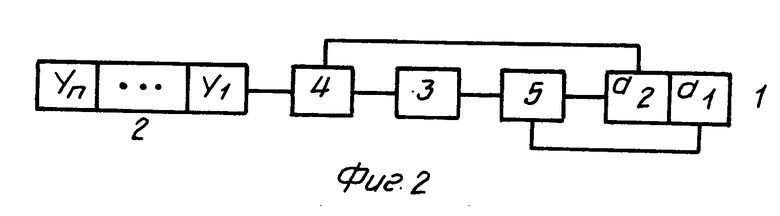

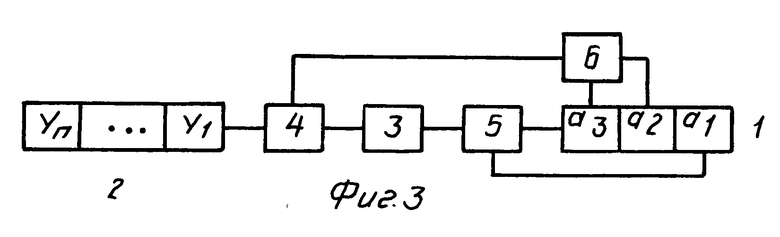

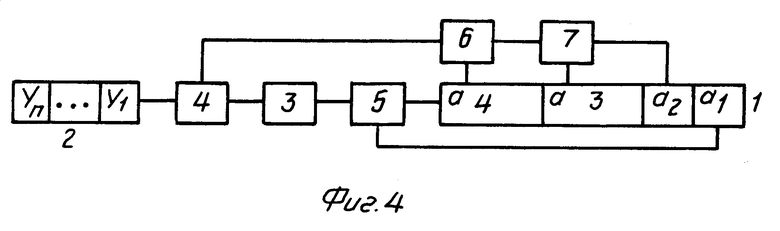

На фиг. 1-4 представлены структурные схемы устройства шифрования двоичной информации для m 1,2,3 и 4 -байтного информационного регистра соответственно.

Устройство шифрования содержит mp-байтный информационный регистр 1, np-байтный ключевой регистр 2, блок 3 8р-разрядного функционального преобразования функции F, первый 8р-разрядный сумматор 4 по модулю 28р, 8р-разрядный сумматор 5 по модулю 2, второй и третий 8р-разрядные сумматоры 6 и 7 по модулю 28р.

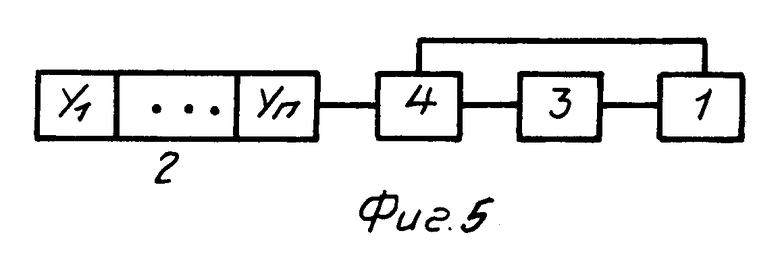

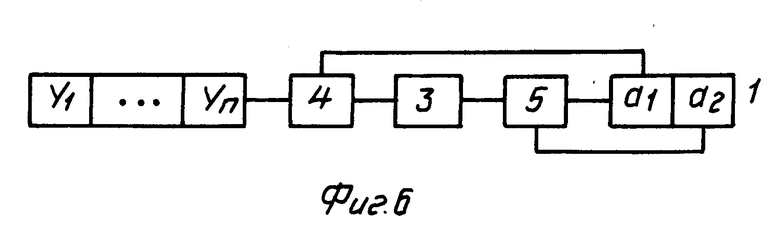

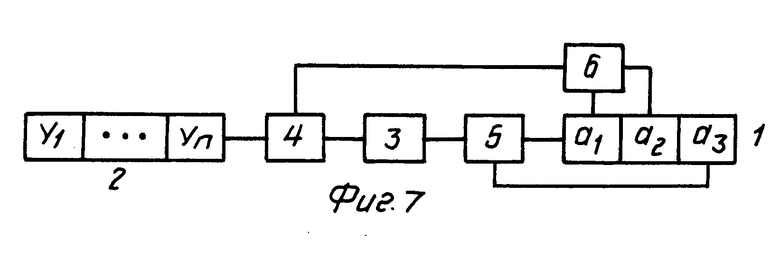

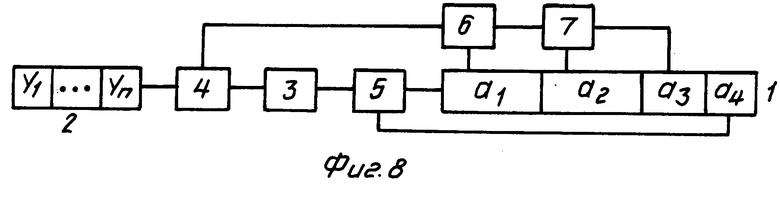

На фиг. 5-8 представлены структурные схемы устройств расшифрования, содержащие те же блоки.

Устройство шифрования двоичной информации работает следующим образом.

При m=1 р байт исходной информации записываются в информационный регистр 1. Устройство шифрования работает n циклов, после которых содержимое р-байтного информационного регистра 1 является результирующей информацией. Все циклы работы устройства шифрования идентичны. В i-й цикл 1 <= i < n, к содержимому р-байтного информационного регистра 1 прибавляется по модулю 28р содержимое i-й р-байтной ячейки ключевого регистра 2, сумма преобразуется блоком 3, и результат записывается в р-байтный информационный регистр 1.

Если содержимое np-байтного ключевого регистра 2 обозначить через Y1,Yn, a p-байтного информационного регистра 1 в i-й цикл через а (i), то в (i+1)-й цикл содержимое р-байтного информационного регистра 1 станет

a(i+1) F(a(i) yi) где a(i) Yi [0,1,28p-1] i > 1;

yi) где a(i) Yi [0,1,28p-1] i > 1; сложение по модулю 28р;

сложение по модулю 28р;

F функция 28р значной логики,

При m 2 2р-байт исходной информации записываются в 2р-байтный информационный регистр 1. Устройство шифрования работает n циклов, после которых содержимое 2р-байтного информационного регистра 1 является результирующей информацией. Все циклы работы устройства шифрования идентичны. В i-й цикл 1 < i < n к содержимому второй р-байтной ячейки 2р-байтного информационного регистра 1 прибавляется по модулю 28рсодержимое i-й р-байтной ячейки ключевого регистра 2, сумма преобразуется функциональным преобразованием 3, к результату прибавляется по модулю 2 содержимое первой р-байтной ячейки 2р-байтного информационного регистра 1, и полученная сумма записывается на место второй р-байтной ячейки информационного регистра 1, содержимое которого предварительно сдвинуто на 8р двоичных разрядов в сторону младших разрядов (вправо).

Если содержимое 2р-байтного информационного регистра i в 1-й цикл обозначить через а2(i), а1(i), то в i+1-й цикл содержимое 2р-байтного информационного регистра 1 станет

a2(i+1) F(a2(i) yi) ⊕ a1 (i) где а1 (i+1)=a2(i), ⊕ сложение по модулю 2.

yi) ⊕ a1 (i) где а1 (i+1)=a2(i), ⊕ сложение по модулю 2.

При m= 3 3p-байт исходной информации записываются в 3р-байтный информационный регистр 1. Устройство шифрования работает n-циклов, после которых содержимое 3р-байтного информационного регистра 1 является результирующей информацией. Все циклы работы устройства шифрования идентичны. В i-й цикл, 1 < i < n, к сумме по модулю 28р содержимых второй и третьей р-байтных ячеек 3р-байтного информационного регистра 1 прибавляется по модулю 28р содержимое i-й р-байтной ячейки ключевого регистра 2, сумма преобразуется функциональным преобразованием 3, к результату прибавляется по модулю 2 содержимое первой р-байтной ячейки информационного регистра 1, и полученная сумма записывается на место третьей р-байтной ячейки информационного регистра 1, содержимое которого предварительно сдвинуто на 8р разрядов в сторону младших разрядов (вправо).

Если содержимое 3р-байтного информационного регистра 1 в i-й цикл обозначить через (а3(i),a2(i), a1(i), то в i+1-й цикл содержимое информационного регистра 1 станет

a3(i+1) F(a3(i) a2(i)

a2(i) yi) ⊕ a1 (i)

yi) ⊕ a1 (i)

а2(i+1) а3(i), a1(i+1) a2(i)

При m 4 4р байт исходной информации записываются в информационный регистр 1. Устройство шифрования работает в n циклов, после которых содержимое 4р-байтного информационного регистра 1 является результирующей информацией. Все циклы работы устройства шифрования идентичны. В i-й цикл 1 < i < n к сумме по модулю 28р содержимых второй, третьей и четвертой р-байтных ячеек информационного регистра 1 прибавляется по модулю 28р содержимое i-й р-байтной ячейки ключевого регистра 2, сумма преобразуется функциональным преобразованием 3, к результату прибавляется по модулю 2 содержимое первой р-байтной ячейки информационного регистра 1 и полученная сумма записывается на место m-й р-байтной ячейки информационного регистра 1, содержимое которого предварительно cдвинуто на 8р разрядов в сторону младших разрядов (вправо).

В i+1-й цикл содержимое m p-байтного информационного регистра 1 станет

a4(i+1) F(a4(i) a3(i)

a3(i) a2(i)

a2(i) yi) ⊕ a1 (i) am-1(i+1) am(i), a1(i+1)

yi) ⊕ a1 (i) am-1(i+1) am(i), a1(i+1)

a2(i).

Рекомендуется выбирать значение р в границах от 2 до 16, m от 1 до 8, t (длина ключа, из которого вырабатываются nр байт заполнения ключевого регистра) от 4 до 32. Эти границы не критичны. Однако следует помнить, что при выборе больших значений р,m, t следует увеличивать длину ключевого регистра n, определяющую количество циклов работы устройства шифрования, а следовательно и скорость обработки информации.

Длина n nр-байтного ключевого регистра выбирается исходя из значений t и m. Например, если 4 <t < 16, то рекомендуется выбирать n > 16 при m 1 и n > 32 при 2 < m < 8. Если 17 < t < 32, то n > 32 при m 1 и n > 64 при 2 < m < 8. Если 33 < t < 64, то n > 64 при m > 1 и n > 128 при 2 < m < 8.

При выборе значения n надо руководствоваться правилом: чем больше n, тем надежнее шифруется информация.

np-байт заполнения ключевого регистра 2 формируются из байт ключа x1,xt, например, путем повторения байт ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА - "АЛБЕР" | 1994 |

|

RU2099890C1 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ "АЛБЕР" | 1991 |

|

RU2024209C1 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ "АЛБЕР" | 1991 |

|

RU2007884C1 |

| СИСТЕМА ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ, СИСТЕМА СИНХРОНИЗАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ШИФРАЦИИ ИЛИ ДЕШИФРАЦИИ ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ | 1996 |

|

RU2099885C1 |

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2097931C1 |

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2096918C1 |

| СПОСОБ И УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 1998 |

|

RU2130641C1 |

| СПОСОБ ШИФРОВАНИЯ СООБЩЕНИЯ, ПРЕДСТАВЛЕННОГО В ВИДЕ МНОГОРАЗРЯДНОГО ДВОИЧНОГО ЧИСЛА | 2015 |

|

RU2580060C1 |

| СПОСОБ ШИФРОВАНИЯ БЛОКОВ ДАННЫХ | 2001 |

|

RU2207736C2 |

| СПОСОБ ШИФРОВАНИЯ ЦИФРОВОЙ ПОДПИСИ ДВОИЧНОГО СООБЩЕНИЯ (АЛБЕР-ПОДПИСЬ) | 1991 |

|

RU2030836C1 |

Использование: в области криптографических преобразований в связных, вычислительных и информационных системах для криптографического закрытия двоичной информации. Сущность изобретения: устройство шифрования двоичной информации содержит 8m-p-байтный информационный регистр, 8n-p-байтный ключевой регистр, блок 8-разрядного функционального преобразования функций F, первый 8p-разрядный сумматор по модулю 2. 8p-разрядные сумматоры по модулю 2, второй и третий 8p-разрядные сумматоры по модулю 2. Использование периодического криптографически сложного обновления ключа и рекурентного способа выработки исходных состояний с зашифрованной начальной позиции позволит надежно скрыть любую информацию о ключе и тем самым существенно улучшит эксплуатационные параметры устройства шифрования. 4 с. п. ф-лы, 8 ил.

| Д | |||

| Сяо, Д | |||

| Керр и С | |||

| Мэдник | |||

| Защита ЭВМ, М.: Мир, 1982, с.137-162. |

Авторы

Даты

1995-12-20—Публикация

1991-11-22—Подача