Изобретение относится к области регулирования и может быть использовано в каналах управления летательного аппарата, электропривода робота и при автоматизации различных технологических процессов.

Известен регулятор канала продольного движения самолета, содержащий демпфер, состоящий из сервопривода, датчика угловой скорости корректора передаточного числа (см. книгу Максимов М.В. и др. Радиоэлектронные системы самонаведения. М.: изд. "Радио и связь", 1982, с. 255, рис. 7.7).

Демпфер совместно с другими блоками управления образует систему.

С помощью демпфера эффективно гасятся угловые колебания по тангенсу, что осуществляется за счет уменьшения коэффициента передачи.

Такая система ухудшает управляемость самолета, т.к. летчик вынужден более энергично отклонять ручку управления.

Известен также автоматический электрический регулятор привода робота, содержащий задатчик и блок обратной связи, выходы которого соединены с входами вычислительного блока, выход которого соединен с входом выходного блока (см. издание "Роботехника и гибкие автоматизированные производства", книга 2 "Приводы робототехнических систем". М.: изд. "Высшая школа", 1986, с. 110, рис. 4.3).

Регулятор работает следующим образом.

Сигнал ошибки системы фиксируется на входе вычислительного блока путем разности сигнала от задатчика и сигнала обратной связи.

На основе текущего значения сигнала ошибки и принятого закона регулирования вычислительный блок формирует управляющий сигнал, который поступает в выходной блок.

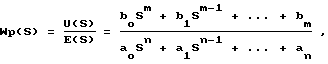

Данный регулятор имеет передаточную функцию вида

где a и b - постоянные коэффициенты,

U(S) - управляющий сигнал,

E(S) - сигнал ошибки.

Для того, чтобы получить переходной процесс с конечным временем регулирования, необходимо вводить в контур регулирования дифференцирующие элементы и обеспечить параметрическую оптимизацию.

Однако дифференцирование сигнала, особенно второго порядка и выше, приводит к увеличению помех, подавление которых возможно при чрезмерном усложнении регулятора.

В этом случае повышение быстродействия достигается за счет увеличения коэффициента усилия разомкнутой системы электропривода, что приводит к колебательному процессу. При этом увеличение быстродействия за счет введения в контур управления дифференцирующей составляющей может привести к усилению помех.

Техническим результатом заявляемого изобретения является повышение быстродействия, эффективности демпфирования системы и получение конечного времени регулирования.

Технический результат достигается тем, что в автоматическом электрическом регуляторе, содержащем задатчик уровня сигнала, вычислительный блок, выходной блок и блок обратной связи с объектом управления, выход задатчика уровня сигнала соединен с первым входом вычислительного блока, выход блока обратной связи с объектом управления соединен с вторым входом вычислительного блока, снабжен конечно-временным формирователем, состоящим из двух групп блоков задержки, вход одной из которых подключен к выходу вычислительного блока, выход соединен с входом выходного блока, связь между выходом блока обратной связи с объектом управления и вторым входом вычислительного блока выполнена в виде подключенной между ними другой группы блоков задержки своим входом и выходом соответственно.

Одна группа блоков задержки состоит из последовательно соединенных блоков задержки, выход каждого блока задержки, кроме последнего, нечетного через инвертор, четного непосредственно соединены с входами первого сумматора, выход которого через пропорциональный преобразователь соединен с одним из входов второго сумматора, выход которого через второй пропорциональный преобразователь соединен с одним из входов третьего сумматора, выход которого является выходом указанной группы блоков задержки, выход последнего блока задержки через соответствующий инвертор подключен к другому входу второго сумматора и непосредственно к другому входу третьего сумматора, вход первого блока задержки и третий вход второго пропорционального преобразователя являются входом указанной группы блоков задержки.

Другая группа блоков задержки состоит из последовательно соединенных блоков задержки, выход каждого из которых, кроме последнего, нечетного непосредственно, четного через инвертор соединены с входами пятого сумматора, выход которого через четвертый пропорциональный преобразователь подключен к одному из входов четвертого сумматора, выход последнего блока задержки через соответствующий инвертор и через последовательно соединенные пятый пропорциональный преобразователь и инвертор подключены соответственно к другим входам четвертого сумматора, выход которого и вход первого блока задержки являются выходом указанной группы блоков задержки, последний вход четвертого сумматора соединен с выходом третьего пропорционального преобразователя, вход которого является входом указанной группы блоков задержки.

Числа блоков задержки в группах блоков задержки равны.

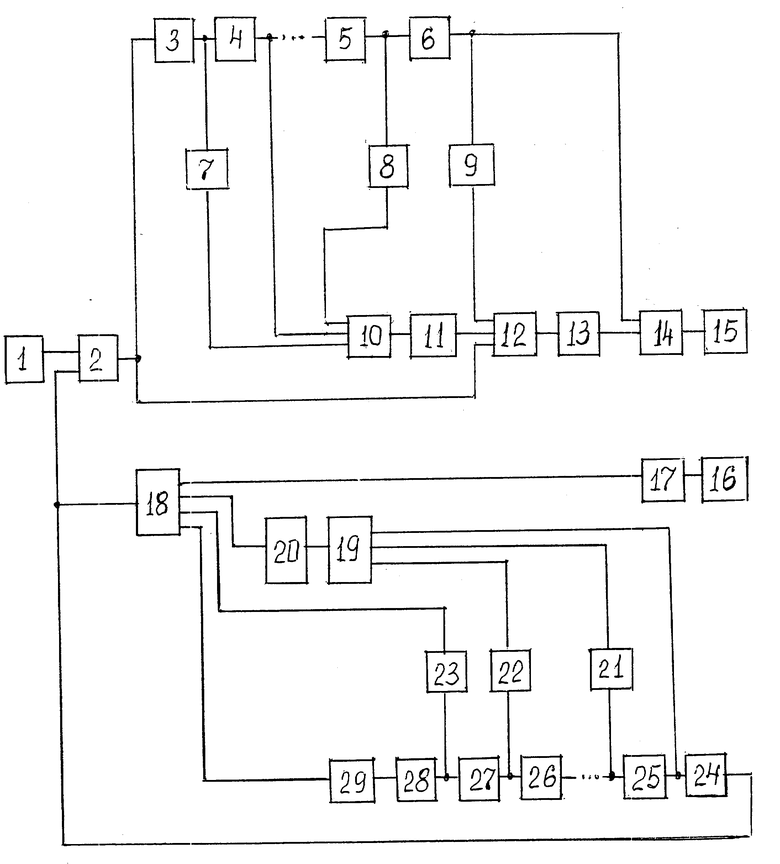

На чертеже приведена схема регулятора.

Автоматический электронный регулятор содержит задатчик уровня сигнала 1, вычислительный блок 2, блоки задержки 3 - 6, инверторы 7 - 9, первый сумматор 10, первый пропорциональный преобразователь 11, второй сумматор 12, второй пропорциональный преобразователь 13, третий сумматор 14, выходной блок 15, блок обратной связи 16 с объектом управления, третий пропорциональный преобразователь 17, четвертый сумматор 18, пятый сумматор 19, четвертый пропорциональный преобразователь 20, инверторы 21 - 23, блок задержки 24 - 27, пятый пропорциональный преобразователь 28, инвертор 29.

В представленном выполнении регулятора выход задатчика 1 уровня сигнала и выход цепи обратной связи с четвертого сумматора 18 подключены к входу вычислительного блока 2, выход которого подключен к входу блока 3 задержки одной группы блоков задержки и к первому входу второго сумматора 12, выход которого соединен с вторым пропорциональным преобразователем 13, выход которого подключен к входу третьего сумматора 14. Одновременно выход последнего блока 6 задержки подключен к входу третьего сумматора 14, выход которого соединен с входом выходного блока 15. Выходы нечетных блоков 3, 5 задержки одной группы также подключены к входам первого сумматора 10 через инверторы 7, 8, а выход четного блока 4 подключен к входу первого сумматора 10 непосредственно.

Выход сумматора 10 соединен через последовательно включенный первый пропорциональный преобразователь 11 с вторым входом второго сумматора 12, третий вход которого соединен с выходом последнего блока 6 задержки. Выход блока 16 обратной связи с объектом подключен через третий пропорциональный преобразователь к первому входу четвертого сумматора 18, выход которого соединен с выходом первого блока 24 задержки, выход которого подключен к первому входу пятого сумматора 19 непосредственно. Выходы блоков 25, 26 задержки другой группы подключены соответственно к второму и третьему входам сумматора через инверторы 21, 22. Выход сумматора 19 через четвертый пропорциональный преобразователь подключен к второму входу четвертого сумматора 18, третий вход которого соединен с входом блока 27 через инвертор 23, а четвертый вход которого соединен с выходом 28 через инвертор 29.

Для поддержания заданного параметра регулирования блок 15 связан с объектом управления, выход которого соединен с входом блока 16 обратной связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПТИМАЛЬНЫЙ РЕГУЛЯТОР | 1996 |

|

RU2105341C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ЦИФРОВОГО ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНОГО РЕГУЛЯТОРА | 1989 |

|

RU2012033C1 |

| Адаптивное регулирующее устройство | 1982 |

|

SU1064271A1 |

| Адаптивный прогнозатор | 1982 |

|

SU1049866A1 |

| Адаптивный регулятор | 1984 |

|

SU1149215A1 |

| Система автоматического регулирования | 1987 |

|

SU1476433A1 |

| Система управления объектом с запаздыванием | 1984 |

|

SU1200241A1 |

| Вентильный электропривод | 1984 |

|

SU1277341A1 |

| Адаптивная система контроля и регулирования | 1982 |

|

SU1070507A1 |

| Система регулирования объектов высокого порядка с запаздыванием | 1989 |

|

SU1667002A1 |

Изобретение относится к области регулирования и может быть использовано в каналах управления летательного аппарата, электропривода робота и при автоматизации различных технологических процессов. Техническим результатом является повышение быстродействия, эффективности демпфирования системы и получение конечного времени регулирования. Технический результат достигается тем, что в автоматическом электрическом регуляторе, содержащем задатчик уровня сигнала, вычислительный блок, выходной блок и блок обратной связи с объектом управления, выход задатчика уровня соединен с первым входом вычислительного блока, выход блока обратной связи с объектом управления соединен с вторым входом вычислительного блока, снабжен конечно-временным формирователем, состоящим их двух групп блоков задержки, вход одной из которых подключен к выходу вычислительного блока, выход соединен с входом выходного блока, связь между выходом блока обратной связи с объектом управления и вторым входом вычислительного блока выполнена в виде подключенной между ними другой группы блоков задержки своим входом и выходом соответственно. 3 з.п. ф-лы, 1 ил.

| Робототехника и гибкие автоматизированные производства | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| - М.: Высшая школа, 1986, с.110, рис.4.3. | |||

Авторы

Даты

1998-02-20—Публикация

1995-07-24—Подача