Устройство относится к области управления и может быть использовано в каналах управления летательных аппаратов, электроприводов роботов и при автоматизации технологических процессов.

Известен оптимальный регулятор по быстродействию, содержащий сравнивающий сумматор, выход которого подключен к релейному элементу, представляющему формирователь выходного сигнала, выход которого является выходом регулятора, выход блока обратной связи с объектом управления соединен с первым входом сравнивающего сумматора, второй вход которого подключен к выходу вычислительного блока .

Данный регулятор выбран в качестве прототипа.

Регулятор работает следующим образом.

Сигнал ошибки системы формируется в сравнивающем сумматоре путем вычисления разности сигналов на выходе вычислительного блока и сигнала обратной связи с объектом управления. На основе текущего значения сигнала ошибок релейный элемент включает управление объектом с определенным знаком.

Недостатками данного регулятора являются чрезвычайная сложность его реализации, особенно для объектов выше третьего порядка, кроме того, регулятор ориентирован только на те случаи, когда корни характеристического уравнения объекта управления являются действительными.

Техническим результатом изобретения является повышение быстродействия управления, сравнительно простая техническая реализация, повышение точности регулирования, демпфирования систем без потери быстродействия и получения конечного времени регулирования, возможность регулировать объект управления высоких порядков.

Технический результат достигается тем, что в оптимальном регуляторе, содержащем сравнивающий сумматор, первый вход которого подключен к выходу блока обратной связи с объектом управления, и формирователь выходного сигнала, выход которого является выходом регулятора, введены задатчик управляющего воздействия, блок определения изменения параметра на заданном временном интервале, блок определения моментов переключения, блок определения сигнала коррекции, выход которого соединен с управляющим входом задатчика управляющего воздействия, выход которого подключен ко второму входу сравнивающего сумматора, выход которого подключен к первому входу блока определения моментов переключения, ко входу блока определения изменения параметра на заданном временном интервале и ко входу формирователя выходного сигнала, выходы блока определения изменения параметра на заданном временном интервале соединены соответственно с вторым и третьим входами блока определения моментов переключения, выход и группа выходов которого подключены к соответствующим входам блока определения сигнала коррекции.

Кроме того, блок определения сигнала коррекции при нечетном показателе степени уравнения системы регулирования содержит инверторы, умножители на два, задатчик единичного сигнала, умножитель, сумматор и последовательно соединенные управляемые элементы задержки, выход сумматора соединен с первым входом умножителя, второй вход которого является входом блока, выход является выходом блока, вход первого управляемого элемента задержки и задающий вход сумматора соединены с выходом задатчика единичного сигнала, выход каждого четного управляемого элемента задержки и каждого нечетного, кроме последнего, соединены соответственно через одноименный умножитель на два, и последовательно соединенные одноименные инвертор и умножитель на два с соответствующими входами сумматора, выход последнего нечетного управляемого элемента задержки подключен через одноименный инвертор к соответствующему входу сумматора, управляющие входы управляемых элементов задержки являются входами группы блока.

Кроме того, блок определения сигнала коррекции при четном показателе степени уравнения системы регулирования содержит инверторы, умножители на два, задатчик единичного сигнала, умножитель, сумматор и последовательно соединенные управляемые элементы задержки, выход сумматора соединен с первым входом умножителя, второй вход которого является входом блока, выход является выходом блока, вход первого управляемого элемента задержки и задающий вход сумматора соединены с выходом задатчика единичного сигнала, выход каждого нечетного управляемого элемента задержки через последовательно соединенные инвертор и умножитель на два и выход каждого четного управляемого элемента задержки, кроме последнего, через одноименный умножитель на два подключены к соответствующим входам сумматора, выход последнего четного управляемого элемента задержки через одноименный инвертор соединен с соответствующим входом сумматора, управляющие входы управляемых элементов задержки являются входами группы блока.

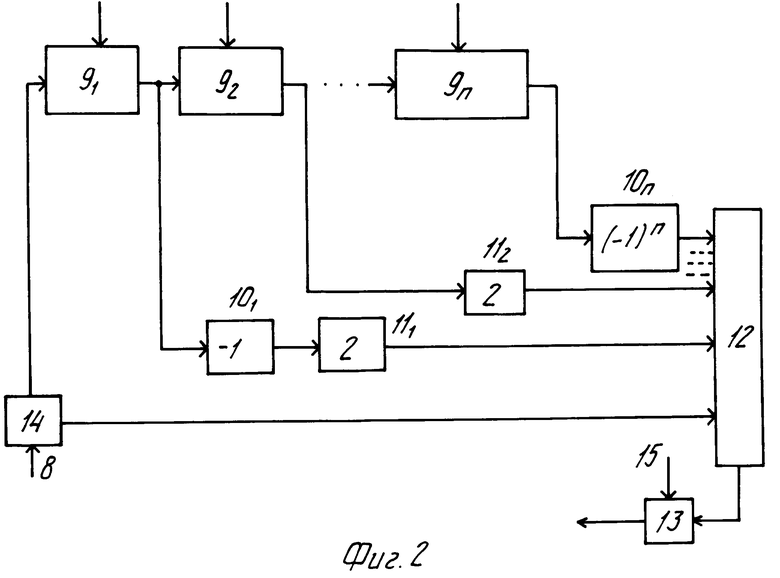

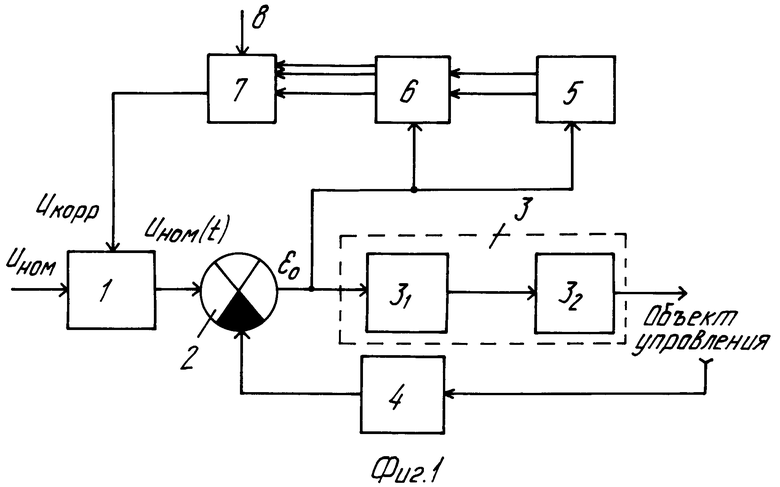

Функциональная схема оптимального регулятора приведена на фиг.1, функциональная схема блока определения сигнала коррекции приведена на фиг. 2.

Устройство содержит задатчик 1 управляющего воздействия, сравнивающий сумматор 2, формирователь 3 выходного сигнала, блок 4 обратной связи с объектом управления, блок 5 определения изменения параметра на заданном временном интервале, блок 6 определения моментов переключения, блок 7 определения сигнала коррекции, управляющий вход 8 устройства.

Блок определения сигнала коррекции содержит последовательно соединенные управляемые элементы задержки 91 -9n, инверторы 10, умножители 11 на два, сумматор 12, умножитель 13, задатчик единичного сигнала 14, вход 15 подачи сигнала λ.

Устройство работает следующим образом. Выходом регулятора является управляющий вход объекта управления (на чертеже не показан), выход параметра регулирования которого соединен с входом блока 4 обратной связи с объектом управления, являющимся информационным входом регулятора. Блок 4 является необходимым признаком для согласования сигнала параметра регулирования объекта управления с аппаратурой обработки сигналов в оптимальном регуляторе. Сигнал на выходе блока 4 обратной связи Uобр.связипоступает на один из входов сравнивающего сумматора 2, на второй вход которого подается сигнал Uном(t) от задатчика 1 управляющего воздействия. Разница Ео между указанными сигналами, определяемая в сумматоре 2, поступает на вход формирователя 3 выходного сигнала и далее в качестве сигнала управляющего воздействия - на объект управления (на чертеже не показан). В случае необходимости формирования управляющего сигнала в виде сложной функции управления формирователь 3 выходного сигнала может состоять из функционального преобразователя и согласующего элемента (на чертеже не показан).

Данный регулятор решает задачу управления объектом для различных систем регулирования на заданном конечном временном интервале. Для этого величина вышеуказанной разности Ео поступает на блоки 5 и 6 для определения корректирующего сигнала в блоке 7, учитывающегося при формировании сигнала управляющегося воздействия.

В блоке 5 определения изменения параметра на заданном временном интервале вычисляют первую  вторую производные величины Еo (порядок производных зависит от порядка уравнений или другого математического аппарата, используемых для вычисления параметров управляющего воздействия.) Определение величин

вторую производные величины Еo (порядок производных зависит от порядка уравнений или другого математического аппарата, используемых для вычисления параметров управляющего воздействия.) Определение величин  (или более высоких порядков) производят любым известным блоком дифференцирования или программно.

(или более высоких порядков) производят любым известным блоком дифференцирования или программно.

Полученные таким образом значения производных Еo поступают в блок 6 определения моментов переключения, где определяют величины значения моментов переключений t1, t2... и величину параметра регулирования λ.

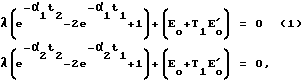

Например, для случая апериодического объекта управления второго порядка процесс регулирования описывается уравнением второго порядка.

,

,

где λ - параметр регулирования,

T1 - постоянная времени объекта управления,

T2- постоянная времени объекта управления, ,

,

t1- момент переключения,

t2 - момент переключения на заданном временном интервале быстродействия.

Полученные в результате решения системы уравнений (1) величины λ и t1, t2, . .. поступают в блок 7 определения сигнала коррекции (фиг.2), на выходе которого формируется сигнал коррекции Uкорр.

Блок 7 определения величины коррекции с учетом поступающего из блока 6 сигнала λ(t), меняющегося в процессе работы регулятора в пределах от 0 до +/-1,  ≤1 и величин моментов переключения управления соответственно t1, t2, . . . , вычисляет значение Uкорр, использующееся для изменения величины Uном.

≤1 и величин моментов переключения управления соответственно t1, t2, . . . , вычисляет значение Uкорр, использующееся для изменения величины Uном.

Блок 7 содержит управляемые элементы задержки 91-9п, на управляющие входы которых поступают сигналы, соответствующие моментам времени t1, t2,... tn, вычисленные в блоке 6.

Элементы задержки последовательно соединены между собой, на первый вход первого элемента 91 задержки поступает единичный сигнал из задатчика 14, управляемого по входу 8. С выходов элементов задержки сигналы через последовательно соединенные инвертор 10 и умножитель на два или непосредственно через инвертор поступают на сумматор 12, где величины, поступающие с выходов элементов задержки, складываются с единичным сигналом в сумматоре 12, полученный сигнал перемножается в умножителе 13 с сигналом λ(t), поступающим из блока 6, и на выходе блока 7 формируется сигнал коррекции Uкорр.

Полученный сигнал Uкорр являющийся функцией λ(t), передают в задатчик 1 управляющего воздействия в детермированный момент времени переключения, он может поступать и посредством сигнала управления, синхронизированного с сигналом по входу 8. В результате этого в задатчике 1 сигнал (сигнал номинального уровня) преобразуется в сигнал, форма которого меняется в зависимости от значения величины λ(t).

Предложенное устройство обеспечивает регулирование объекта на заданном временном интервале с заданным быстродействием в зависимости от заданных условий регулирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОМАТИЧЕСКИЙ ЭЛЕКТРИЧЕСКИЙ РЕГУЛЯТОР | 1995 |

|

RU2105339C1 |

| Самонастраивающаяся система управления | 1978 |

|

SU746415A1 |

| Самонастраивающаяся система управления | 1981 |

|

SU1008698A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ЦИФРОВОГО ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНОГО РЕГУЛЯТОРА | 1989 |

|

RU2012033C1 |

| Устройство для оценки эмоциональной устойчивости оператора | 1986 |

|

SU1434480A1 |

| Устройство для управления асинхронным электродвигателем | 1989 |

|

SU1663734A1 |

| Устройство для обучения операторов систем управления | 1986 |

|

SU1434479A1 |

| Самонастраивающаяся система для регулирования объектов с запаздыванием | 1977 |

|

SU634235A1 |

| Система управления | 1976 |

|

SU623178A1 |

| Кодирующее устройство кода Рида-Соломона | 1989 |

|

SU1716609A1 |

Изобретение относится к области управления и может быть использовано в каналах управления летательных аппаратов, электроприводов роботов и при автоматизации технологических процессов. Технический результат заключается в повышении быстродействия управления, упрощении технической реализации, повышении точности регулирования, демпфировании систем без потери быстродействия и получении конечного времени регулирования. Технический результат достигается введением в регулятор блока определения моментов переключения и блока определения сигнала коррекции управляющего воздействия. В результате определения этих величин задатчик управляющего воздействия формирует сигнал управления, величина и момент изменения величины которого наиболее оптимальны для объекта управления, процесс регулирования которого описывается определенной математической зависимостью. 2 з.п. ф-лы, 2 ил.

| Атанс М., Фалб П | |||

| Оптимальное управление | |||

| - М.: Машиностроение, 1968, с | |||

| Способ обмыливания жиров и жирных масел | 1911 |

|

SU500A1 |

| Устройство для электрического видения на расстоянии | 1924 |

|

SU769A1 |

Авторы

Даты

1998-02-20—Публикация

1996-06-24—Подача