Предлагаемое техническое решение относится к вычислительной технике и может найти применение в информационных системах, в системах технического зрения и в автоматизированных системах управления АСУ индустриального и специального назначения, в которых необходимо решать задачи по распознаванию сложных образов и принятию решения в условиях реального времени.

Цель изобретения - повышение быстродействия системы, предназначенной для обработки данных, поступающих в режиме реального времени.

В настоящее время известны подобные устройства для обработки данных, а именно для обнаружения и распознавания объектов, представляющие собой дополнительный модуль процессора, содержащий блок ввода исходного изображения и вывода результатов распознавания, блок предварительной обработки данных для выделения характеристик обнаруженных объектов и блок, содержащий набор нейронных слоев, число которых соответствует степени абстракции характеристических данных [1]. Недостатком этого устройства является жесткость его структуры, то есть отсутствие возможности настройки системы на другой класс задач.

Известно также устройство, используемое для разработки нейрокомпьютера, выполненное на основе FPGA, реализуемое в виде платы, подключаемой к системной шине ПЭВМ PC IBM/AT, и работающее в режиме сопроцессора [2]. Это устройство может работать в режиме моделирования различных видов нейросетей, но не решает задачу распознавания и имеет медленную шину ввода-вывода информации.

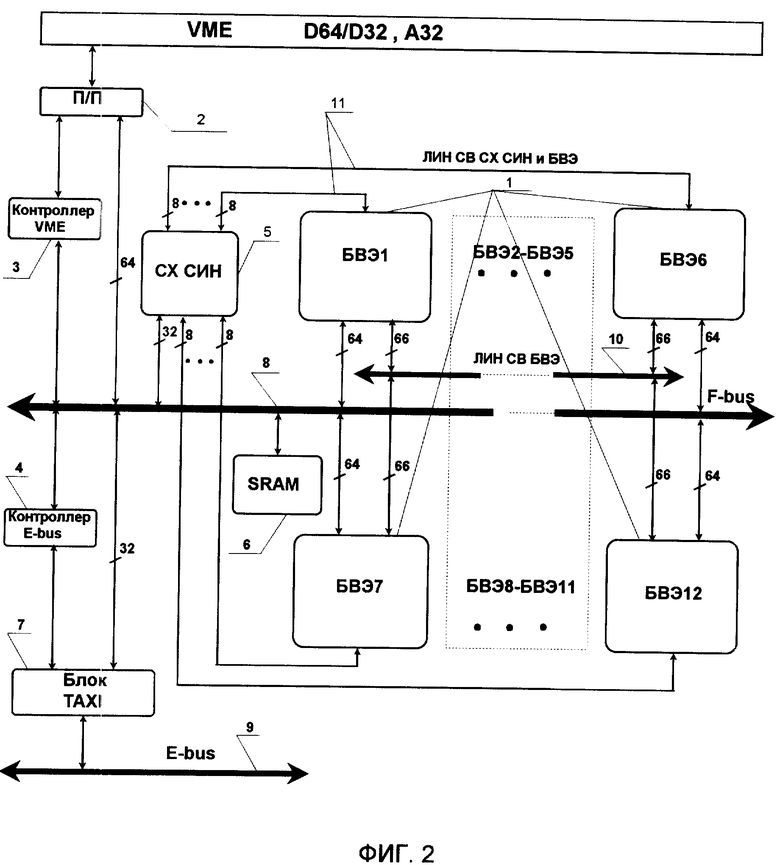

Наиболее близким к предлагаемому вычислителю является устройство Splash [3], используемое для идентификации цепочек в генной инженерии. Это устройство представляет собой две платы расширения для рабочих станций SUN-3 и SUN-4, выполненные в стандарте VME (Versabus modified for Eurocard). На первой плате размещается линейный массив вычислителей, а на второй - двухпортовая память. Линейный массив вычислителей устройства Splash содержит 32 последовательно соединенных вычислительных устройства ВЭО-ВЭ31, выполненных на базе программируемых пользователем микросхем Xilinx, к входам-выходам которых подсоединены 32 микросхемы памяти ОЗУ (см. фиг. 1), причем каждая микросхема памяти подсоединена только к одному выходу предыдущего и к одному входу последующего ВЭ. Вход и выход массива ВЭ подсоединены к входу и выходу входного и выходного устройств FIFO, которые, в свою очередь, подсоединены к входу-выходу блока управления, выполненного на двух дополнительных микросхемах Xilinx. Входы-выходы блока управления подсоединены к шине VME рабочей станции SUN для управления работой устройства и к шине VSB для ввода-вывода данных.

Вторая плата содержит только микросхемы двухпортовой памяти и ее входы-выходы подсоединены к шине VME рабочей станции для инициализации и перезагрузки платы, а также к шине VSB для обмена данными с первой платой.

Это устройство является высокоэффективным средством для распознавания двух похожих последовательностей и может быть использовано для распознавания образов и речи, восстановления данных и генетического анализа.

Основным недостатком устройства является отсутствие внешней шины, которая позволяла бы наращивать его вычислительную мощность, путем подключения дополнительных плат линейных вычислителей, имеющих возможность быстрого обмена информацией между собой.

Задача, на решение которой было направлено это изобретение состояла в разработке структуры гибкого нейроподобного вычислителя, предназначенного для построения систем распознавания образов и обработки графической информации в режиме реального времени, который имел бы высокоскоростную внешнюю шину, позволяющую объединять несколько вычислителей в единую систему при решении сложных задач, и отличающегося от традиционных нейронных вычислителей тем, что в данном вычислителе фиксирование связей между отдельными базовыми вычислительными элементами будут меняться в зависимости от типа задачи и проведенного обучения.

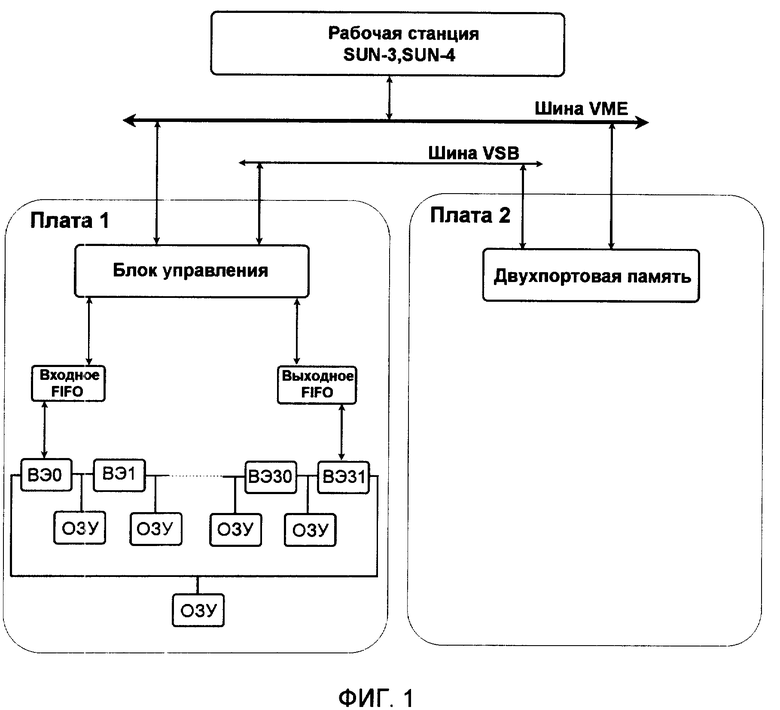

Для решения этой задачи вычислитель с перепрограммируемой архитектурой, содержащий в своей основе базовые вычислительные элементы (БВЭ1-БВЭ12), входы-выходы которых соединены между собой по принципу каждый с каждым линиями связи базовых вычислительных элементов (ЛИН СВ БВЭ), подсоединены к общей внутренней шине (F-bus) и подсоединены отдельными линиями связи схемы синхронизации и базового вычислительного элемента (ЛИН СВ СХ СИН и БВЭ) к схеме синхронизации (СХ СИН), выполненной на основе микросхемы FPGA, входы-выходы которой подсоединены к шине F-bus, посредством которой все эти устройства подсоединены к локальной статической памяти (SRAM), к входам-выходам контроллера шины VME (контроллер VМЕ) и к приемникам-передатчикам шины VME (ПЯТ), к входам-выходам контроллера внешней шины (контроллер E- bus), предназначенной для межплатной связи, и к блоку TAXI, который подсоединен к внешней шине (E-bus).

Вычислитель реализован на основе многопроцессорной шины VME с использованием мультиплексированных 7 D64 и блочных передач данных, базовые вычислительные элементы выполнены на базе современных программируемых пользователем микросхемах FPGA, а блок TAXI выполнен на основе высокоскоростных асинхронных приемников-передатчиков TAXI, позволяющих использовать для передачи данных электрические и оптические линии связи.

Вычислитель предназначен для решения задачи обработки изображения, выполняемой в масштабе реального времени. Модуль может использоваться в качестве базовой ячейки для реализации многослойной нейронной сети с изменяемыми параметрами. Вычислитель реализован на основе 12 программируемых пользователем логических микросхем FPGA. Использование перепрограммируемых пользователем микросхем FPGA позволяет реализовывать на одной и той же плате нейронные сети разного типа и размера. Процесс переконфигурирования осуществляется путем загрузки файла конфигурации, содержащего данные о схеме и хранящегося в ПЗУ или на диске ЭВМ.

На фиг. 2 представлена блок-схема предлагаемого вычислителя с перепрограммируемой архитектурой, где 1 - базовые вычислительные элементы, 2 - приемники-передатчики шины VME, 3 - контроллер шины VME,4 - контроллер шины E-bus, 5 - схема синхронизации, 6 - локальная статическая память, 7- блок TAXI, 8 - внутренняя шина F-bus, 9 - внешняя шина E-bus, 10 - линии связи базовых вычислительных элементов, 11- линии связи схемы синхронизации и базовых вычислительных элементов.

Работа контроллера.

В настоящее время в НИИСИ РАН разработана модель опытного образца предлагаемого вычислителя с перепрограммируемой архитектурой, который будет эксплуатироваться в составе ЭВМ серии "Багет" с системной магистралью VME и микропроцессором i80486DX2/DX4 в качестве дополнительного модуля, расширяющего возможности ЭВМ.

Контроллер шины VME выполняет следующие функции:

запросчика прерывания шины УМЕ (interrupter),

поддержки режима ведомого (slave).

Запросчик прерывания программируется вектором прерывания и уровнем линий прерывания выставляемых модулем в цикле подтверждения прерывания шины VМЕ.

Режим ведомого программируется адресными модификаторами и старшими разрядами линий адреса шины VME и поддерживает мультиплексированные блочные A32, D64 и блочные A32, D32 передачи данных.

БВЭ используются для выполнения простейших арифметических операций типа суммирование, вычитание, умножение и вычисление пороговых функций. Каждый БВЭ содержит четыре вычислительных элемента, состоящих из 8-разрядного конвейерного умножителя, 24-разрядного сумматора-вычитателя, схемы логического умножения, компаратора и набора регистров. Прохождение данных через любой вычислительный элемент определяется путем установки соответствующих битов в регистре контроля. Загрузка регистра контроля выполняется центральным процессором либо напрямую, либо через схему синхронизации. Остальные регистры используются для хранения значений входных коэффициентов, порогов и результатов вычислений.

Локальная статическая память собрана на основе восьми микросхем емкостью 256 Кбайт или 0,5 Мбайт и организацией 64К*8 или 128К*8 соответственно. Для обеспечения обращения к памяти за один такт при системной частоте 33,3 МГц используются микросхемы с временем выборки не более 20 нс. Память предназначена для хранения общих коэффициентов, а также промежуточных результатов вычислений или окончательных результатов, подготовленных к передаче на шину VME или E-bus.

Схема синхронизации используется для управления потоками данных в вычислителе и соединена отдельными линиями связи со всеми БВЭ. Синхронизация передачи данных между БВЭ усложняется большим количеством шин и может осуществляться двумя способами, используя прерывания и семафоры. Блок TAXI содержит четыре высокоскоростных асинхронных передатчика Am7968-175, и четыре высокоскоростных асинхронных приемника Am7969-175. Каждая такая пара приемник-передатчик позволяет выполнять обмен 8-разрядными данными по принципу точка-точка со скоростью до 17,5 Мбайт в секунду. При одновременном использовании четырех каналов скорость обмена данными равна 70 Мбайт в секунду. Передатчик выполняет преобразование (прозрачное для пользователя) 8-разрядных данных в последовательный код, используя способ кодировки 4В/5В или 5В/6В, который позволяет избегать ошибок передачи. Приемник, в свою очередь, выполняет обратное преобразование. TAXI позволяет производить обмен данными, используя электрические или оптические линии связи.

В зависимости от организации процесса вычислений каскадирование БВЭ может быть выполнено двумя способами:

через линии, связывающие между собой БВЭ, когда вычисления выполняются в пределах одной платы нейровычислителя;

через внешнюю шину E-bus, когда результаты вычислений с выхода одного вычислителя передаются на входы последующего.

Литература.

1. Заявка ЕПВ(EP) N 0457909, кл. G 06 F 15/70, опубл. 27.11.91.

2. С. С. Забара, Э.И. Комухаев, М.Э. Куссуль, В.Г, Сахарин. Проектирование логических схем нейрокомпьютера в элементном базисе ПЛИС ХС2000. УСиМ, 1993, N 1.

3. M. Gokhale, W.Holmes, A. Kopser. Building and Using a Highly Parallel Programmable Logic Array, Computer, January 1991, р. 81 - 88.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПЕРЕПРОГРАММИРУЕМЫЙ ВЫЧИСЛИТЕЛЬ ДЛЯ СИСТЕМ ОБРАБОТКИ ИНФОРМАЦИИ | 1998 |

|

RU2146389C1 |

| СИСТЕМНЫЙ КОНТРОЛЛЕР | 1996 |

|

RU2110834C1 |

| СИСТЕМНЫЙ КОНТРОЛЛЕР | 1996 |

|

RU2124751C1 |

| ПРОГРАММИРУЕМЫЙ ЛОГИЧЕСКИЙ КОНТРОЛЛЕР | 1995 |

|

RU2101757C1 |

| Устройство приоритетного прерывания | 1990 |

|

SU1793440A1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ СИГНАЛОВ В ГИДРОАКУСТИЧЕСКИХ СИСТЕМАХ | 2001 |

|

RU2207620C2 |

| УПРАВЛЯЮЩИЙ МОДУЛЬ | 2014 |

|

RU2569576C1 |

| СПОСОБ И УСТРОЙСТВО ОБРАБОТКИ СИГНАЛОВ ЛИНИЙ СВЯЗИ ПО МОДЕЛИ СИГНАЛА И ПЕРЕПРОГРАММИРУЕМЫМ ЭЛЕКТРИЧЕСКИМ СХЕМАМ | 2005 |

|

RU2317641C2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2017211C1 |

| ПЕРЕДАТЧИК СО СЛЕДЯЩЕЙ ОБРАТНОЙ СВЯЗЬЮ | 2013 |

|

RU2558609C2 |

Изобретение относится к вычислительной технике и может найти применение в автоматизированных системах управления АСУ индустриального и специального назначения. Изобретение позволяет решать задачи по распознаванию сложных образов и принятию решения в условиях реального времени. Вычислитель с перепрограммируемой архитектурой содержит базовые вычислительные элементы 1, приемники/передатчики шины VМЕ 2, контроллер шины VМЕ 3, контроллер шины Е-bus 4, схему синхронизации 5, статическую память 6, блок ТАХI 7, внутреннюю шину F-bus 8, внешнюю шину Е-bus 9, линии связи базовых вычислительных элементов 10, линии связи схемы синхронизации и базовых вычислительных элементов 11. 2 ил.

Вычислитель с перепрограммируемой архитектурой, содержащий базовые вычислительные элементы и локальную статистическую память, отличающийся тем, что входы/выходы базовых вычислительных элементов соединены между собой по принципу каждый с каждым и присоединены к общей внутренней шине F-bus, к которой подсоединены входы/выходы схемы синхронизации, локальная статическая память, входы/выходы контроллера шины VME и приемники/передатчики шины VME, входы/выходы контроллера внешней шины E-bus, предназначенной для межплатной связи, блок TAXI, содержащий высокоскоростные асинхронные приемники и передатчики.

| Ионный денситометр для измерения плотности газа | 1973 |

|

SU457909A1 |

| Computer, January, 1991, Gokhale M | |||

| и др | |||

| Buildin g and Using a Highlu Parallel Programmable Logic с | |||

| Горный компас | 0 |

|

SU81A1 |

| Cypress Se micon ductor Corp., Application Handbook, 1994, с.4-46, 4-49, 4-57, 5- 76, 5-92 | |||

| Каган Б.М | |||

| Электронные вычислительные машины и системы | |||

| - М | |||

| : Энергоатомиз дат, 1985, с | |||

| Льномолотилка веялка | 1923 |

|

SU498A1 |

| Забара С.С | |||

| и др | |||

| ЩИТОВОЙ ДЛЯ ВОДОЕМОВ ЗАТВОР | 1922 |

|

SU2000A1 |

| - М | |||

| : УСиМ, 1993, N 1, с.9-1 2 | |||

| VITA, VME64 Draft Specitication Ref D 1.6, 1993 | |||

| Newbridge Corporation, SCV64 User Manual, 1994 | |||

| Tundra Semicon ductor Corp., CA 91C042 Applicatio n Note, 1996. | |||

Авторы

Даты

1998-07-10—Публикация

1996-12-04—Подача