Предлагаемое техническое решение относится к вычислительной технике и может найти применение в информационных системах, в системах технического зрения и в автоматизированных системах управления АСУ индустриального и специального назначения, в которых необходимо решать задачи по обработке информации, распознаванию сложных образов и принятию решения в условиях реального времени.

Цель изобретения - повышение быстродействия системы, предназначенной для обработки данных, поступающих в режиме реального времени.

В настоящее время известны подобные устройства для обработки данных, а именно, для обнаружения и распознавания объектов, представляющие собой дополнительный модуль процессора, содержащий блок ввода исходного изображения и вывода результатов распознавания, блок предварительной обработки данных для выделения характеристик обнаруженных объектов и блок, содержащий набор нейронных слоев, число которых соответствует степени абстракции характеристических данных [1] . Недостатком этого устройства является жесткость его структуры, то есть отсутствие возможности настройки системы на другой класс задач.

Кроме того, известны многопроцессорный модуль цифровой обработки сигналов и специализированная микросхема Нейропроцессор NM6403, разработанные в АО "НТЦ" Модуль [2], [3].

Многопроцессорный модуль цифровой обработки сигналов выполнен на цифровых сигнальных процессорах TMS320C40 фирмы Texas Instruments и представляет собой одноплатную многопроцессорную вычислительную машину. Модуль содержит: 6 процессоров TMS320C40-GFL50, соединенных по схеме "каждый с каждым" посредством линк-портов, 7 блоков быстрой статической памяти по 1 Мбайт и 4 блока динамической памяти по 16 Мбайт каждый, подключенные к четырем процессорам.

Нейропроцессор NM6403 состоит из двух вычислительных единиц: процессора с уменьшенным набором команд для управления потоками данных и векторным АЛУ (арифметическо-логическое устройство) аппаратно поддерживающим векторно-матричные операции. Разрядность векторного АЛУ может изменяться от 1 до 64. При работе с 8-ми разрядными операндами АЛУ можно рассматривать как 8 независимых единиц.

Как многопроцессорный модуль так и специализированный процессор могут быть использованы для сигнальной обработки, моделирования нейронных сетей и обработки изображения.

Наиболее близким к предлагаемому вычислителю является специализированный сигнальный процессор SM320C80 фирмы Texas Instruments [4].

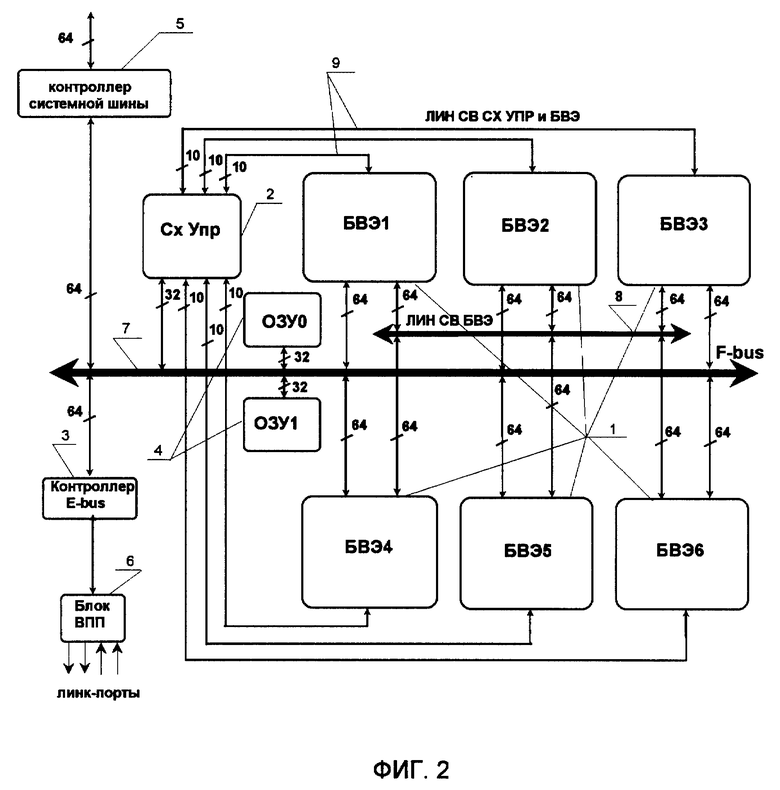

Устройство SM320C80 состоит из управляющего процессора с уменьшенным набором команд УП и 4-х цифровых сигнальных процессоров СП0-СП3 входы/выходы портов данных Д и инструкций И управляющего процессора и локального порта Л, глобального порта Г и порта инструкций И сигнальных процессоров посредством мультиплексируемых каналов пересечения шин могут быть соединены друг с другом, с входами/выходами 5 отдельных банков памяти ОЗУ0-ОЗУ3, ОЗУ УП и с входами/выходами контроллера системной шины СК (фиг 1).

Устройство может быть использовано для задач обработки сигналов, обработки изображения и моделирования нейронных сетей.

Основными недостатками устройства являются недостаточная гибкость, отсутствие внешних портов, которые позволяли бы объединять несколько микросхем для создания высокопроизводительных параллельных систем и небольшая разрядность шины данных.

Задача на решение которой было направлено это изобретение состояла в разработке структуры гибкого вычислителя, предназначенного для построения систем распознавания образов и обработки графической информации в режиме реального времени, который имел бы высокоскоростную внешнюю шину, позволяющую объединять несколько вычислителей в единую систему при решение сложных задач, позволял аппаратно реализовывать векторно-матричные и матрично-матричные операции и отличающегося от традиционных нейронных вычислителей тем, что в данном вычислителе фиксирование связей между отдельными базовыми вычислительными элементами будут меняться в зависимости от типа задачи.

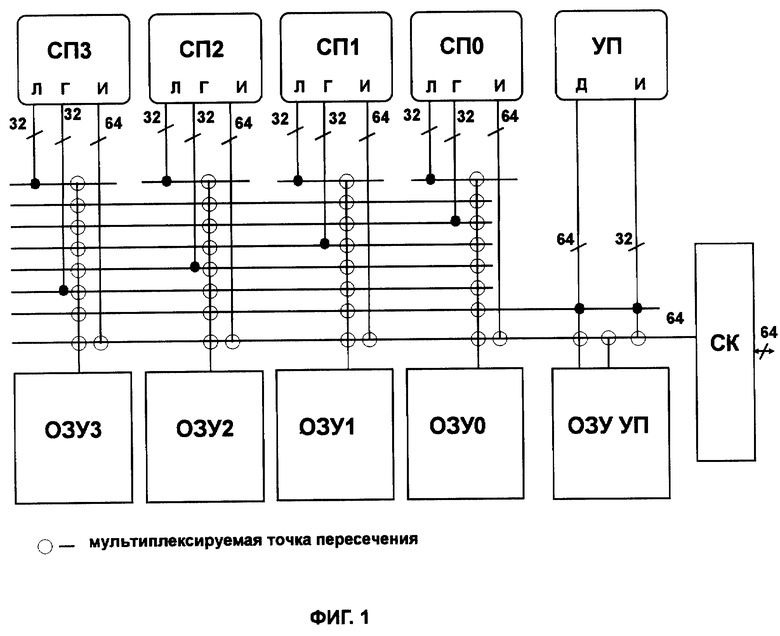

Для решения этой задачи перепрограммируемый вычислитель для систем обработки информации, содержащий в своей основе базовые вычислительные элементы (БВЭ1- БВЭ6), входы/выходы которых соединены между собой по принципу каждый с каждым линиями связи базовых вычислительных элементов (ЛИН СВ БВЭ), подсоединены к общей внутренней шине (F-bus), и подсоединены отдельными линиями связи схемы управления и базового вычислительного элемента (ЛИН СВ СХ УПР и БВЭ) к схеме управления (СХ УПР), выполненной на основе микросхемы FPGA, входы/выходы которой подсоединены к шине F-bus, посредством которой все эти устройства подсоединены к двум массивам локальной статической памяти (ОЗУ0-ОЗУ1), к входам/выходам контроллера внешней шины (Контроллер E-bus), входы/выходы которого подсоединены к блоку высокоскоростных приемников/передатчиков (Блок ВПП), реализован на базе современных перепрограммируемых пользователем микросхем типа FPGA, схема управления представляет собой специализированный процессор с уменьшенным набором команд собственной разработки, а блок ВПП выполнен на основе высокоскоростных асинхронных приемников/передатчиков HOTLink фирмы Cypress, позволяющих использовать для передачи данных электрические и оптические линии связи.

Вычислитель предназначен для решения задачи обработки изображения или любой другой информации, выполняемой в масштабе реального времени. Модуль может использоваться в качестве базовой ячейки для реализации многослойной нейронной сети с изменяемыми параметрами.

Вычислитель реализован на основе 8 перепрограммируемых пользователем логических микросхем FPGA. Использование перепрограммируемых пользователем микросхем FPGA позволяет решать на одной и той же плате задачи различного вида и реализовывать нейронные сети разного типа и размера.

Процесс переконфигурирования осуществляется путем загрузки файла конфигурации, содержащего данные о схеме и хранящегося в ПЗУ или на диске ЭВМ.

Предлагаемое изобретение поясняется чертежом, где на фиг. 2 представлена блок-схема предлагаемого перепрограммируемого вычислителя для систем обработки информации.

Перепрограммируемый вычислитель для систем обработки информации содержит следующие функциональные блоки:

1 - базовые вычислительные элементы

2 - схема управления

3 - контроллер внешней шины

4 - два массива локальной статической памяти

5 - контроллер системной шины

6 - блок ВПП

7 - внутренняя шина F-bus

8 - линии связи базовых вычислительных элементов

9 - линии связи схемы управления и базовых вычислительных элементов

Работа перепрограммируемого вычислителя для систем обработки информации.

В настоящее время в НИИСИ РАН разработана модель опытного образца предлагаемого перепрограммируемого вычислителя для систем обработки информации, который будет эксплуатироваться в составе ЭВМ серии "Багет" с системной магистралью VME и микропроцессором i80486DX2/DX4 в качестве дополнительного модуля, расширяющего возможности ЭВМ.

Контроллер системной шины - в настоящее время контроллер шины VME, является стандартным устройством и выполняет следующие функции:

- запросчика прерывания шины VME (interrupter);

- поддержки режима ведомого (slave).

Запросчик прерывания программируется вектором прерывания и уровнем линий прерывания выставляемых модулем в цикле подтверждения прерывания шины VME.

Режим ведомого программируется адресными модификаторами и старшими разрядами линий адреса шины VME и поддерживает мультиплексированные блочные A32, D64 и блочные A32, D32 передачи данных.

В качестве контроллера может быть использована любая стандартная микросхема, например SCV64 [5].

При работе с другими системными шинами, например с шиной PCI, в качестве системного контроллера может быть использован любой стандартный контроллер шины PCI [7].

БВЭ используются для выполнения простейших арифметических операций типа: суммирование, вычитание, умножение и вычисление пороговых функций. Каждый БВЭ содержит 4 вычислительных элемента, состоящих из 8-разрядного конвейерного умножителя, 24-разрядного сумматора/вычитателя с накоплением результата, схемы логического умножения, компаратора и набора регистров. Наличие таких ресурсов БВЭ позволяет аппаратно выполнять векторно-матричные и матрично-матричные операции, которые являются базовыми при обработке изображения и реализации нейронных сетей. Выбор необходимой арифметической операции, проводимой над входными данными, и путь прохождения данных через любой вычислительный элемент определяется установкой схемой управления соответствующей команды, набора битов на шину ЛИН СВ СХ УПР и БВЭ. Остальные внутренние регистры БВЭ используются для хранения значений входных коэффициентов, порогов и результатов вычислений.

Два массива локальной статической памяти собраны из 8 микросхем статической памяти емкостью 0,5 Мбайт, имеют размер 4 Мбайт и организованы как массив 512К 8-байтовых слов. Массивы памяти связаны со схемой управления отдельными адресными шинами и могут функционировать независимо друг от друга. Для обеспечения обращения к памяти за один такт при системной частоте 33.3 МГц, используются микросхемы с временем выборки не более 15 нс. Память предназначена для хранения общих коэффициентов, а также промежуточных результатов вычислений или окончательных результатов, подготовленных к передаче через контроллер системной шины в центральный процессор или контроллер E-bus на линк-порты.

Схема управления используется для управления потоками данных в вычислителе и соединена отдельными линиями связи со всеми БВЭ. В качестве схемы управления может быть использован стандартный 32-разрядный процессор с уменьшенным набором команд типа R3000 фирмы MIPS, ARM710T, ARM720T и ARM740T фирмы ARM или процессоров семейства Am29000 фирмы AMD. Описание структуры, набора команд и функциональных особенностей процессора с уменьшенным набором команд приводится в книге [8]. Особенностью схемы управления перепрограммируемого вычислителя для систем обработки информации является наличие рабочей команды, управляющей шестью базовыми вычислительными элементами. Команда позволяет одновременно, за один такт, задавать различные режимы функционирования шести базовым вычислительным элементам и инкрементировать оба массива памяти на любое число от 0 до 255, хранимое в регистрах инкремента, причем каждому массиву соответствует свой регистр. Команда может повторяться любое количество раз в соответствии со значением хранимым в специальном регистре. Это позволяет выполнять основную команду без потерь на организацию циклов и переходов.

Контроллер E-bus используется для управления приемниками и передатчиками блока ВПП, синхронизации и распределения данных, передающихся между схемой управления и блоком ВПП. Он представляет из себя набор 4-х стандартных FIFO (память магазинного типа, первый вошел, первый вышел) и регистров управления и данных.

Блок ВПП содержит два высокоскоростных асинхронных передатчика CY7B923 и два высокоскоростных асинхронных приемника CY7B933. Пара приемник/передатчик позволят выполнять обмен 8-разрядными данными по принципу точка-точка со скоростью до 33 Мбайт в секунду. При одновременном использовании четырех каналов (два прием, два передача) скорость обмена данными равна 132 Мбайт в секунду. Передатчик выполняет преобразование (прозрачное для пользователя) 8-разрядных данных в последовательный код, используя способ кодировки 4В/5В или 5В/6В, который позволяет избегать ошибок передачи. Приемник, в свою очередь, выполняет обратное преобразование. Блок ВПП позволяет производить обмен данными, используя электрические или оптические линии связи.

В зависимости от организации процесса вычислений каскадирование БВЭ может быть выполнено двумя способами:

- через линии связывающие, между собой БВЭ, когда вычисления выполняются в пределах одной платы нейровычислителя;

- через внешнюю шину E-bus, когда результаты вычислений с выхода одного вычислителя передаются на входы последующего.

Использование данного изобретения в автоматизированных системах управления АСУ индустриального и специального назначения удовлетворит длительно существующую потребность в высокопроизводительном и гибком устройстве, позволяющем решать различные задачи по распознаванию сложных образов и принятию решения в условиях реального времени.

Источники информации

1. Заявка N 0457909, ЕПВ(EP), G 06 F 15/70, опубл. 27.11.91.

2. Ю. Борисов, В.Кашкаров, С.Сорокин. Нейросетевые методы обработки информации и средства их программно-аппаратной поддержки. Открытые системы, N 4, 1997.

3. П.Виксне, Д.Фомин, В.Черников. Аппаратно-программные комплексы поддержки нейровычислений. Приборостроение, N 7, 1996.

4. SM320C80 Digital Signal Processor, Texas Instruments, SGUS21, August, 1996.

5. Newbridge Corporation, SCV64 User Manual, 1994.

6. 82420/82430 PCIset ISA and EISA Bridges, Intel Corp., Order Number: 290483-001.

7. Электроника СБИС, Проектирование микроструктур, - М.: Мир, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬ С ПЕРЕПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 1996 |

|

RU2115161C1 |

| СИСТЕМНЫЙ КОНТРОЛЛЕР | 1996 |

|

RU2110834C1 |

| СИСТЕМНЫЙ КОНТРОЛЛЕР | 1996 |

|

RU2124751C1 |

| ПРОГРАММИРУЕМЫЙ ЛОГИЧЕСКИЙ КОНТРОЛЛЕР | 1995 |

|

RU2101757C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ СИГНАЛОВ В ГИДРОАКУСТИЧЕСКИХ СИСТЕМАХ | 2001 |

|

RU2207620C2 |

| ПОДСИСТЕМА ПАМЯТИ ЯДРА МИКРОПРОЦЕССОРА | 2011 |

|

RU2475822C1 |

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| УПРАВЛЯЮЩИЙ МОДУЛЬ | 2014 |

|

RU2569576C1 |

| Устройство приоритетного прерывания | 1990 |

|

SU1793440A1 |

| УСТРОЙСТВО ОБРАБОТКИ ИНФОРМАЦИИ | 2011 |

|

RU2480820C1 |

Изобретение относится к вычислительной технике и может найти применение в автоматизированных системах управления АСУ индустриального и специального назначения, в которых необходимо решать задачи по распознаванию сложных образов, обработке информации и принятию решения в условиях реального времени. Вычислитель с перепрограммируемой архитектурой содержит базовые вычислительные элементы, схему управления, контроллер внешней шины, два массива локальной статической памяти, контроллер системной шины, блок ВПП, внутреннюю шину F-bus. Базовые вычислительные элементы соединены между собой линиями связи ЛИН СВ БВЭ по принципу каждый с каждым, подсоединены отдельными линиями ЛИН СВ СХ УПР и БВЭ к схеме управления. Последняя представляет собой специализированный процессор с уменьшенным набором команд. К внутренней шине подсоединены входы/выходы контроллера. Технический результат изобретения заключается в возможности объединения нескольких плат для решения сложных задач. Блок ВПП реализован на высокоскоростных приемниках/передатчиках HOTLink, позволяющих использовать электрические и оптические линии связи. 2 ил.

Перепрограммируемый вычислитель для систем обработки информации, содержащий схему управления, представляющую собой процессор с уменьшенным набором команд, входы/выходы которой соединены с внутренней шиной, к которой подсоединены входы/выходы базовых вычислительных элементов, входы/выходы двух массивов локальной статической памяти и входы/выходы контроллера системной шины, отличающийся тем, что базовые вычислительные элементы соединены между собой линиями связи по принципу каждый с каждым и подсоединены отдельными линиями связи к схеме управления, а к внутренней шине подсоединены входы/выходы контроллера внешней шины, к входам/выходам которого подсоединены входы/выходы блока высокоскоростных приемников/передатчиков, причем указанный блок выполнен на высокоскоростных асинхронных приемниках/передатчиках, позволяющих использовать электрические и оптические линии связи и предназначенных для каскадирования базовых вычислительных элементов.

| Прибор для подогрева воздуха отработавшими газам и двигателя | 1921 |

|

SU320A1 |

| INSTRUMENTS, SGUSO21, August, 1996 | |||

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| US 4144566 A, 13.03.79 | |||

| ШАРОВАЯ ОПОРА | 0 |

|

SU333306A1 |

| ЦИФРОВОЙ КОМПЬЮТЕР С ВОЗМОЖНОСТЬЮ ПАРАЛЛЕЛЬНОГО ВЫПОЛНЕНИЯ ДВУХ И БОЛЕЕ КОМАНД | 1991 |

|

RU2109333C1 |

Авторы

Даты

2000-03-10—Публикация

1998-07-07—Подача