Изобретение относится к устройствам для поддержания работоспособности процессора (интеллектуального промышленного контроллера) в системе контроля и управления различными объектами газовой и нефтяной промышленности, тепло- и гидроэнергетики. Газовая промышленность: АСУТП транспортировки газа (компрессорные станции, газоперерабатывающие заводы). Нефтяная промышленность: АСУТП переработки нефти (нефтеперерабатывающие заводы). Тепло- и гидроэнергетика: АСУТП (ГЭС, ГГЭС, ТЭЦ, котельные).

В настоящее время известны устройства для контроля и запоминания ошибки в логике программного обеспечения системы, представляющие собой встроенную память центрального процессора, реализующие автоматический контроль преобразованием адреса в адресную информацию в центральном процессоре через информационную шину внешне установленной памяти с выделением соответствующей информации во встроенную память путем ее загрузки по адресной шине [1]. Система эта очень сложна и дорога и требует разработки специальных устройств, включающих специализированный микропроцессор. Известны также устройства для восстановления работоспособности процессора в микропроцессорной системе [2]. Система обеспечивается одним из процессоров, который обнаруживает сбой в работе других процессоров и отключает питание при обнаружении сбоев. Применение таких устройств требует разработки специализированного контроллера питания. Ни первое, ни второе из описанных устройств не осуществляют селекцию ошибок и не предусматривают оканчание текущего цикла процессора.

Наиболее близким к предлагаемому является системный контроллер, типа VIC068/VAC068 [5].

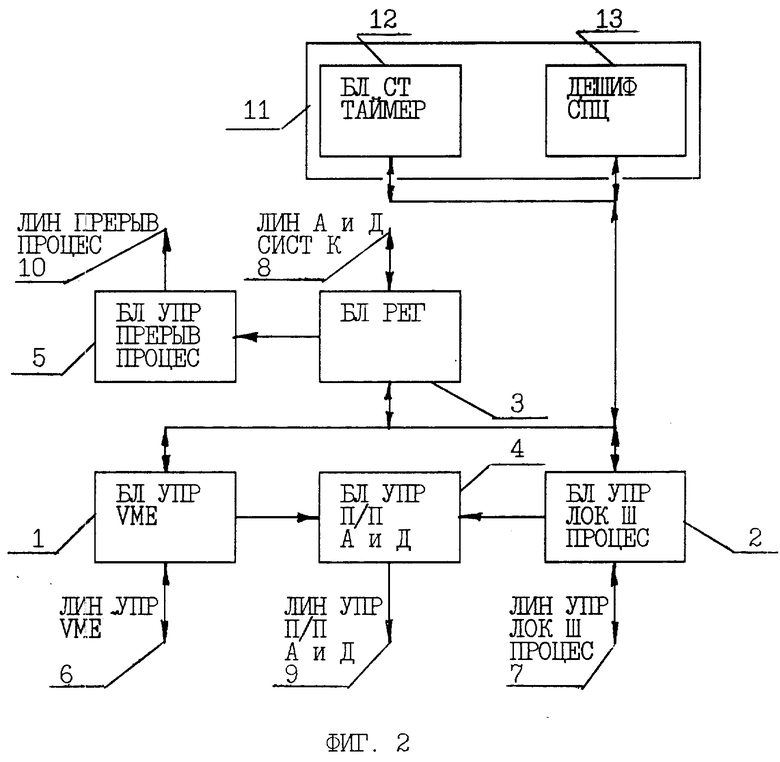

Системный контроллер содержит блок управления шиной VME (БЛ УПР VME), к входам/выходам которого подсоединены входы/ выходы линий управления шины VME (ЛИН УПР VME), блок управления локальной шиной процессора (БЛ УПР ЛОК III ПРОЦЕС), к входам/выходам которого подсоединены входы/выходы линий управления локальной шины процессора (ЛИН УЯР ЛОК III ПРОЦЕС), а к выходам блока управления шиной VME и блока управления локальной шиной процессора подсоединены входы блока управления приемниками/передатчиками адреса и данных (БЛ УПР П/П А и Д), выходы которого подсоединены к линиям управления приемниками/передатчиками адреса и данных (ЛИН УПР П/П А и Д), блок регистров (БЛ РЕГ), к выходам/входам которого подсоединены линии адреса и данных системного контроллера (ЛИН А и Д СИСТ К), а к выходам которого подсоеденены входы блока управления прерываниями процессора (БЛ УПР ПРЕРЫВ ПРОЦЕС), выходы которого подсоединены к линиям прерывания процессора (ЛИН ПРЕРЫВ ПРОЦЕС), при этом входы/выходы блока управления шины VME подсоединены к входам/ выходам локальной шины процессора и к входам/выходам блока регистров (см. фиг. 1).

Этот контроллер является высокоэффективным средством построения систем на базе шины VME. Поддерживает блочные передачи, обеспечивает уменьшение потребляемой мощности по сравнению с дискретным исполнением, поддерживает прямой доступ к памяти и межпроцессорный обмен.

Основной недостаток контроллера - ненадежность его работы в системах контроля и управления объектами промышленности. Ошибки в логике программного обеспечения могут привести к нарушению технологического процесса из-за отсутствия в контроллере средств, фиксирующих и корректирующих ошибки.

Задача, на решение которой было направлено данное изобретение, состояла в обеспечении надежной работы контроллера за счет снабжения его аппаратными средствами, способными выполнять системную функцию по фиксированию и созданию условий для коррекции ошибки, заключающуюся в заканчивании текущего цикла процессора сигналом готовности.

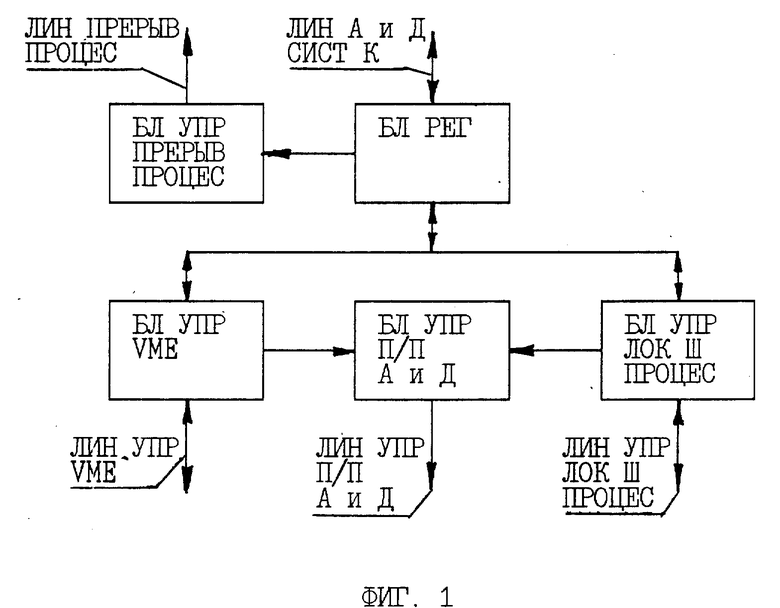

Для решения этой задачи системный контроллер, содержащий блок управления шиной VME (БЛ УПР VME), к входам/выходам которого подсоединены входы/выходы линий управления шины VME (ЛИН УПР VME), блок управления локальной шиной процессора (БЛ УПР ЛОК III ПРОЦЕС), к входам/выходам которого подсоединены входы/выходы линий управления локальной шины процессора (ЛИН УПР ЛОК III ПРОЦЕС), а к выходам блока управления шиной VME и блока управления локальной шиной процессора подсоединены входы блока управления приемниками/передатчиками адреса и данных (БД УПР П/П А и Д), выходы которого подсоединены к линиям управления приемопередатчиками адреса и данных (ЛИН УПР П/П А и Д), блок регистров (БЛ РЕГ), к выходам/входам которого подсоединены линии адреса и данных системного контроллера (ЛИН А и Д СИСТ К), а к выходам которого подсоединены входы блока управления прерываниями процессора (БЛ УПР ПРЕРЫВ ПРОЦЕС), выходы которого подсоединены к линиям прерывания процессора (ЛИН ПРЕРЫВ ПРОЦЕС), при этом входы/выходы блока управления шины VME подсоединены к входам/выходам блока управления локальной шины процессора и к входам/выходам блока регистров, который выполнен на базе программируемой пользователем микросхеме FPGA и программируемых логических матрицах PAL и снабжен блоком коррекции (БЛ КОРР), содержащим блок сторожевых таймеров (БЛ СТ ТАЙМЕР) и дешифратор специальных циклов процессора (ДЕШИФ СПЦ), входы/выходы блока сторожевых таймеров и дешифратора подключены к входам/выходам блока управления шиной VМЕ, к входам/выходам блока управления локальной шины процессора и к входам/выходам блока регистров.

Блок сторожевых таймеров включает: сторожевой таймер VME, сторожевой таймер локальной шины процессора и сторожевой таймер для периодического тестирования.

Дешифратор специальных циклов процессора выполнен на элементе 5И, имеет 5 входов с блока управления локальной шины процессора и один выход на блок регистров и блок сторожевых таймеров.

Выполнение контроллера на базе микросхем FPGA и PAL позволяет ввести в контроллер блок коррекции, раскрытый выше.

Введение в системный контроллер блока коррекции, состоящего из блока сторожевых таймеров и дешифратора специальных циклов процессора, соединенных описанным выше способом, обеспечивает контроллеру системную функцию по заканчиванию текущего цикла процессора сигналом готовности.

Сторожевой таймер для периодического тестирования запоминает аппаратную ошибку системы управления, выставляет запрос на прерывание и заканчивает текущий цикл процессора.

При выполнении циклов обращения к несуществующему адресу сторожевой таймер VME или сторожевой таймерлокальной шины процессора запоминает (фиксирует) ошибку в блоке регистров, выставляет запрос на прерывание процессора (создание условий для коррекции) и заканчивает текущий цикл процессора.

При выполнении несанкционированных специальных циклов процессора дешифратор специальных циклов процессора запоминает ошибку в блоке регистров, выставляет запрос на прерывание, а блок сторожевых таймеров заканчивает текущий цикл процессора.

В итоге контроллер приобретает системную функцию по заканчиванию текущего цикла процессора при возникновении аппаратных ошибок и ошибок логики программы и создает условия для коррекции ошибок.

На фиг. 2 представлена блок-схема предлагаемого системного контроллера.

Системный контроллер содержит:

1 - блок управления шиной VME,

2 - блок управления локальной шиной процессора,

3 - блок регистров,

4 - блок управления приемниками/передатчиками адреса и данных,

5 - блок управления прерываниями процессора,

6 - линии управления VME,

7 - линии управления локальной шины процессора,

8 - линии адреса и данных системного контроллера,

9 - линии управления приемниками/передатчиками адреса и данных,

10 - линии прерывания процессора,

11 - блок коррекции,

12 - блок сторожевых таймеров,

13 - дешифратор специальных циклов процессора.

Работа контроллера

В 1995 г. в КБ Корунд-М был собран и испытан модуль БТ02-203, в состав которого входил предлагаемый системный контроллер. Модуль входит в систему контроля и управления газокомпрессорной станцией АНКОР. Модуль работает на базе микропроцессора i386EX. Системный контроллер реализован на базе программируемой пользователем микросхеме XC4005 (фирма XILINIX) и программируемых логических матриц PAL22V10 (фирма AMD). Блок управления шины VME выполняет следующие функции:

- запросчика прерывания шины VME (interrupter);

- обработчика прерывания шины VME (interrupt handler);

- формирователя последовательной цепочки подтверждения запроса на прерывание шины VME (iack daisy-chain driver);

- запросчик шины VME (requester);

- арбитр шины VME (arbiter);

- формирователь последовательной цепочки подтверждения захвата шины (bus request daisy-chain driver);

- обеспечение режима ведущего (master);

- поддержка режима ведомого (slave).

Запросчик прерывания программируется вектором прерывания и уровнем линии прерывания, выставляемых модулем в цикле подтверждения прерывания шины VME.

Обработчик прерывания шины VME аппаратно обрабатывает запросы прерываний, выставленных на шине VME. Приоритет прерываний жестко задан.

Запросчик шины VME пытается захватить шину всякий раз, когда центральный процессор обращается к VME или когда происходит цикл обращения к ОЗУ при одновременном доступе со стороны VME.

Режим ведущего программируется адресными модификаторами, выставляемыми на VME.

Блок ведомого программируется адресными модификаторами и старшими разрядами линий адреса шины VME.

В свете выполнения задачи, решаемой изобретением, блок управления локальной шины процессора 2 выставляет сигнал готовности процессору, блок регистров 3 фиксирует аппаратные ошибки и ошибки логики программы, блок управления приемниками/передатчиками адреса и данных 4 выставляет сигналы направления и разрешения передачи адреса и данных, блок управления прерываниями процессора 5 через линии 10 выставляет процессору прерывание.

Блок коррекции 11 состоит из блока сторожевых таймеров 12 и дешифратора специальных циклов 13. Блок сторожевых таймеров включает:

- сторожевой таймер, выполняющий функцию тайм-аута на шине VME;

- сторожевой таймер, выполняющий функцию тайм-аута на шине процессора;

- сторожевой таймер для периодического тестирования. Таймер шины VME служит для определения временного интервала, после которого на шине VME выставляется сигнал ошибки. Таймер в реализованной схеме был запрограммирован на интервал 80 мкс. При возникновении ошибки выставляется немаскируемое прерывание NMI, сигнал ошибки шины BERR и заканчивается текущий цикл процессора.

Сторожевой таймер шины процессора выставляет немаскируемое прерывание NMI при отсутствии отклика в течении 160 мкс, а также оканчивает текущий цикл процессора.

В состав системного контроллера также входит сторожевой таймер для периодического тестирования с фиксированной длительностью 640 мс, по истечении которого выставляется запрос маскируемого прерывания IRQ5 и запускается программа тестирования основных устройств модуля. Если тестирование происходит без ошибок, запрос на прерывание IRQ5 сбрасывается, в противном случае через время 40 мс выставляется запрос на немаскируемое прерывание NMI и сигнал ошибки ERROR.

Контроллер снабжен возможностью подачи сигналов в звуковой форме (управление динамиком) и световой форме оператору, а также сигнала ошибки для удаленного контроля.

Дешифратор специальных циклов фиксирует и корректирует ошибки, возникающие в результате несанкционированного выполнения команд HALT и SHUTDOWN.

При работе системного контроллера в описанной системе была обнаружена и скорректирована ошибка процессора, возникающая в результате выполнения несанкционированной команды HALT. Через шину 7 и блок 2 дешифратором специальных циклов 13 проводится анализ текущих циклов процессора. При возникновении несанкционированного цикла HALT блок 13 воздействует на блок 3, в котором фиксируется ошибка. Блок 3 воздействует на блок 5 и через линию 10 выставляет прерывание процессору. При этом воздействие блока 13 передается блоку сторожевых таймеров 11, который воздействует на блок 2 и по линии 7 передается сигнал готовности процессору (оканчивание текущего цикла процессора). Процессор выполнив команду HALT и получив прерывание по линии 10, не останавливает выполнение программы, а запускает программу обработки прерывания, которая воздействуя по линиям 7 через блок 2 по линиям 8 считывает содержимое блока 3, по которому определяет источник ошибки.

Результаты испытаний показали надежную работу системного контроллера в системе АНКОР при работе с операционными системами OS-9000, VxWorks, MS-DOS.

Использование в промышленных системах данного изобретения удовлетворит длительно существующую потребность в выполнении контроллером системной функции, заключающейся в заканчивании текущего цикла процессора сигналом готовности после фиксирования и создания условий для коррекции ошибки, что принесет системным котроллерам этого типа коммерческий успех на рынке.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМНЫЙ КОНТРОЛЛЕР | 1996 |

|

RU2124751C1 |

| ПЕРЕПРОГРАММИРУЕМЫЙ ВЫЧИСЛИТЕЛЬ ДЛЯ СИСТЕМ ОБРАБОТКИ ИНФОРМАЦИИ | 1998 |

|

RU2146389C1 |

| ПРОГРАММИРУЕМЫЙ ЛОГИЧЕСКИЙ КОНТРОЛЛЕР | 1995 |

|

RU2101757C1 |

| ВЫЧИСЛИТЕЛЬ С ПЕРЕПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 1996 |

|

RU2115161C1 |

| Устройство приоритетного прерывания | 1990 |

|

SU1793440A1 |

| УПРАВЛЯЮЩИЙ МОДУЛЬ | 2014 |

|

RU2569576C1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ ПОТОКОВ ДАННЫХ, СЧИТЫВАЕМЫХ ИЗ ОЗУ | 2011 |

|

RU2475817C1 |

| СПОСОБ ИСПРАВЛЕНИЯ ОДИНОЧНЫХ ОШИБОК И ПРЕДОТВРАЩЕНИЯ ВОЗНИКНОВЕНИЯ ДВОЙНЫХ ОШИБОК В РЕГИСТРОВОМ ФАЙЛЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2465636C1 |

Изобретение относится к устройствам для поддержания работоспособности процессора в системах контроля и управления различными объектами газовой, нефтяной промышленности и тепло- и гидроэнергетики. Системный контроллер содержит блок управления шиной VМЕ, блок управления локальной шиной, блок регистров, блок управления приемниками/передатчиками адреса и данных, блок управления прерываниями процессора, линии управления шиной V МЕ, линии управления локальной шиной процессора, линии адреса и данных системного контроллера, линии управления приемниками/передатчиками адреса и данных, линии прерывания процессора, блок коррекции, блок сторожевых таймеров, дешифратор специальных циклов процессора. 2 ил.

Системный контроллер, содержащий блок управления шиной VME, к входам/выходам которого подсоединены входы/выходы линий управления шины VME, блок управления локальной шиной процессора, к входам/выходам которого подсоединены входы/выходы линий управления локальной шиной процессора, а к выходам блока управления шиной VME и блока управления локальной шиной процессора подсоединены входы блока управления приемниками/передатчиками адреса и данных, выходы которого подсоединены к линиям управления приемниками/передатчиками адреса и данных, блок регистров, к входам/выходам которого подсоединены линии адреса и данных системного контроллера, к выходам которого подсоединены входы блока управления прерываний процессора, выходы которого подсоединены к линиям прерывания процессора, при этом входы/выходы блока управления шины VME подсоединены к входам/выходам блока управления локальной шиной процессора и к входам/выходам блока регистров, отличающийся тем, что системный контроллер снабжен блоком коррекции, содержащим блок сторожевых таймеров и дешифратор специальных циклов процессора, входы/выходы блока сторожевых таймеров и дешифратора специальных циклов процессора подключены к входам/выходам блока управления шиной VME, к входам/выходам блока управления локальной шиной процессора и к входам/выходам блока регистров.

Авторы

Даты

1998-05-10—Публикация

1996-02-20—Подача