Изобретение относится к вычислительной технике и может быть использовано в многоканальных устройствах сопряжения ЭВМ с последовательными каналами связи.

Известно сетевое интерфейсное устройство [1], состоящее из сетевого процессора, включающего в свой состав микропроцессор, память и шинный интерфейс, выходящий на шину данных, интерфейса приемопередатчика, включающего в свой состав приемный буфер магазинной памяти, передающий буфер магазинной памяти, блок прямого доступа к памяти и шинный интерфейс, выходящий на шину данных, приемопередатчика, сопрягаемого с каналом связи последовательного типа и шины данных.

Устройство обеспечивает высокую скорость обмена данными, однако является одноканальным. С другой стороны, сопряжение ЭВМ с N каналами связи посредством N сетевых интерфейсов приводит к значительной аппаратурной избыточности распределенной системы в целом.

Наиболее близким по технической сущности к заявляемому устройству является устройство для сопряжения ЭВМ с каналами связи [2], содержащее приемопередатчик, блок управления, включающий в себя микропроцессор и память, блок передатчиков, блок приемников, блок обработки прерываний, триггер, блок элементов И и блок триггеров.

Однако устройство не обеспечивает высокую производительность обмена из-за необходимости затрат времени ЭВМ на буферизацию данных для каналов связи, анализ достоверности передаваемой информации, организацию передачи данных по определенному протоколу, а также диагностику средств передачи.

Целью изобретения является повышение производительности обмена данными между ЭВМ и каналами связи.

Цель достигается тем, что в устройство для сопряжения ЭВМ с каналами связи, содержащее приемопередатчик, блок управления, блок передатчиков, блок приемников, блок обработки прерываний и блок триггеров, введены элементы ИЛИ, приемный буфер магазинной памяти, передающий буфер магазинной памяти и блок прямого доступа в память, при этом входы-выходы данных блока обработки прерываний, блока управления, приемного и передающего буферов магазинной памяти, блока передатчиков, блока приемников, приемопередатчика и вход управления блока прямого доступа в память объединены шиной данных, выход данных приемного буфера магазинной памяти и вход данных передающего буфера магазинной памяти соединены с первым входом-выходом данных блока прямого доступа в память, второй вход-выход которого является входом-выходом устройства, а выход прерывания подключен к первому входу блока обработки прерываний, второй и третий входы которого соединены со статусными выходами соответственно приемного и передающего буферов магазинной памяти, четвертый - со статусным выходом приемопередатчика, пятый - с выходом элемента ИЛИ, а выход - с входом прерывания блока управления, статусные входы которого соединены с информационными выходами блока триггеров и с соответствующими входами элемента ИЛИ, а управляющий выход - с входом сброса блока триггеров, объединяющим входы сброса всех триггеров, установочные входы каждого из которых подключены к соответствующим информационным выходам блока приемников, входы которого соединены с канальными входами устройства, а выход данных - с входом приемопередатчика, выход которого подключен к входу данных блока передатчиков, выходы которого соединены с канальными выходами устройства.

Введенные элементы являются признаками, обладающими существенными отличиями от прототипа, так как эти элементы: элемент ИЛИ, приемный и передающий буферы магазинной памяти и блок прямого доступа в память в совокупности и во взаимосвязи с элементами известного устройства образуют новую совокупность признаков, обеспечивающую выполнение устройством новой функции: организацию такого обмена между ЭВМ и некоторым множеством каналов связи, когда информация для каналов связи сначала целиком переписывается из памяти ЭВМ в режиме прямого доступа в передающий буфер магазинной памяти, откуда затем под управлением блока управления подается в приемопередатчик, с выхода которого данные в последовательном виде через блок передатчиков поступают в выделенный канал связи, а информация для ЭВМ из какого-либо канала связи, поступающая с выхода блока приемников в последовательном виде на вход приемопередатчика, с его входа-выхода данных передается под управлением микроЭВМ в приемный буфер магазинной памяти, откуда затем в режиме прямого доступа целиком переписывается в память ЭВМ. Это дает положительный эффект - повышает производительность обмена данными между ЭВМ и каналами связи за счет сокращения затрат времени ЭВМ на буферизацию данных в программном режиме, анализ достоверности передаваемой информации, организацию передачи данных по определенному протоколу и диагностику средств передачи.

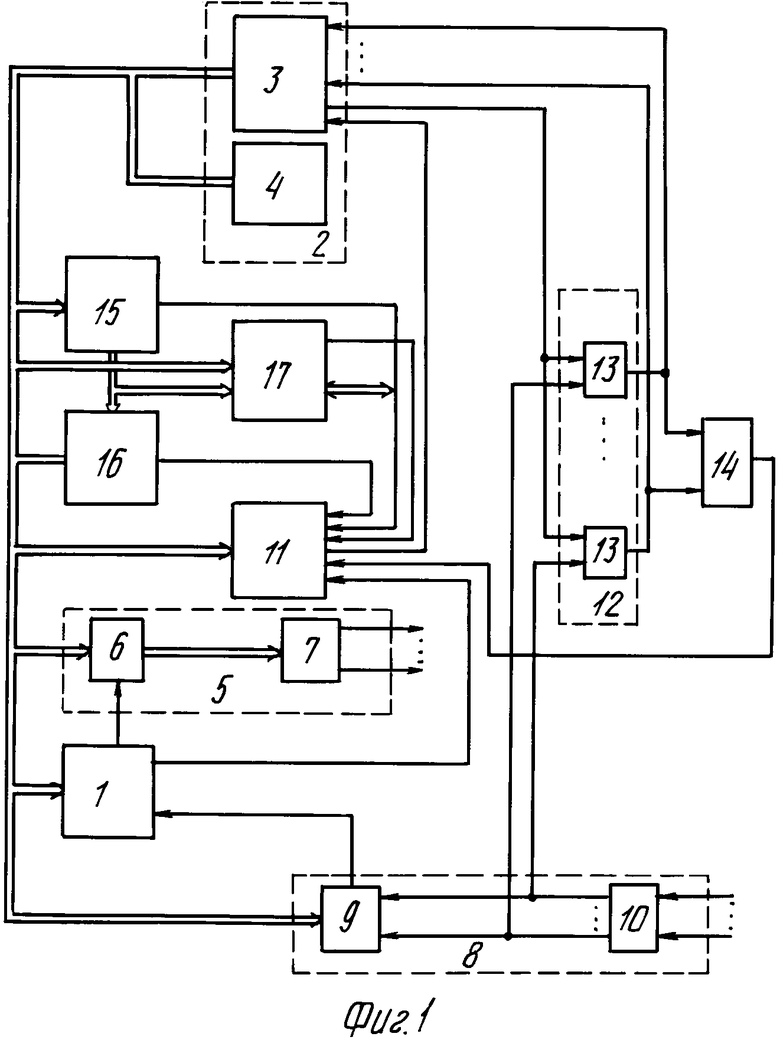

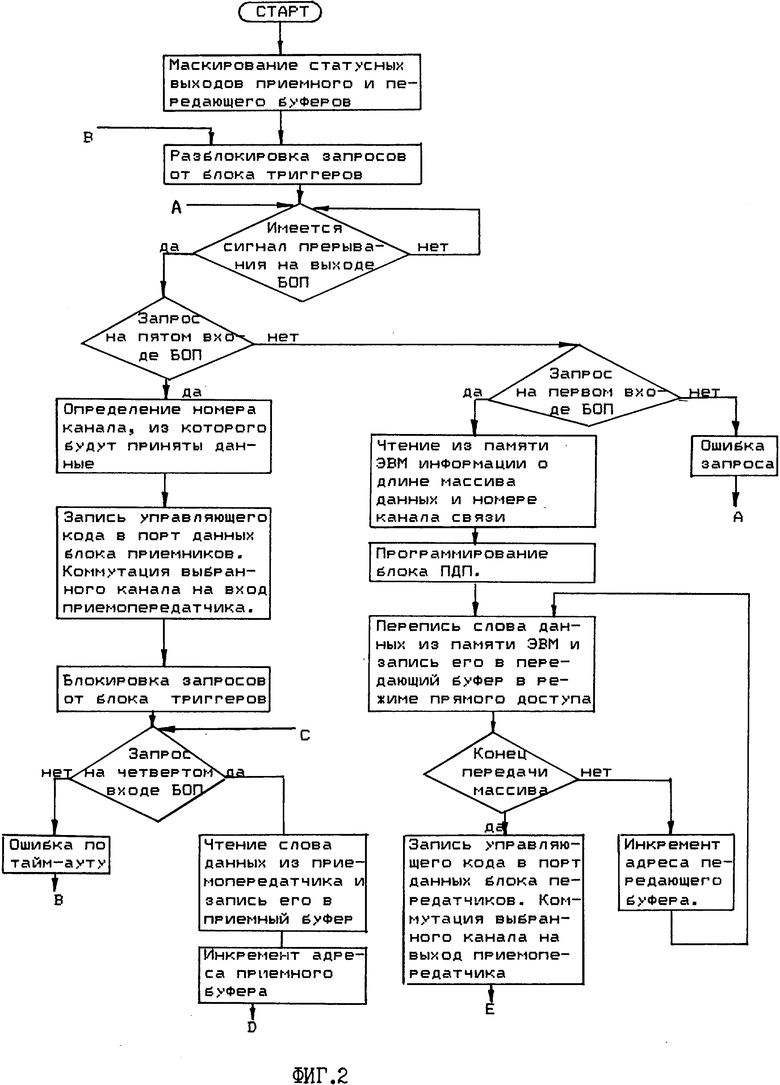

Блок-схема устройства представлена на фиг.1; алгоритм его функционирования - на фиг.2

Устройство содержит приемопередатчик 1, блок 2 управления, включающий в себя микропроцессор 3 и память 4, блок 5 передатчиков, включающий в себя мультиплексор 6 передатчика и преобразователи 7 уровня, блок 8 приемников, включающий в себя мультиплексор 9 приемников и преобразователи 10 уровня, блок 11 обработки прерываний, блок 12 триггеров, содержащий RS-триггеры 13 по числу каналов связи, элемент ИЛИ 14, приемный 15 и передающий 16 буферы магазинной памяти и блок 17 прямого доступа в память.

Входы-выходы данных блока 11 обработки прерываний, блока 2 управления, приемного 15 и передающего 16 буферов магазинной памяти, блока 5 передатчиков, блока 8 приемников, приемопередатчика 1 и вход управления блока 17 прямого доступа в память объединены шиной данных. Выход данных приемного 15 и вход данных передающего 16 буферов магазинной памяти соединены с первым входом-выходом данных блока 17 прямого доступа в память, второй порт которого сопрягается с памятью ЭВМ и является входом-выходом устройства, а выход прерывания подключен к первому входу блока 11 обработки прерываний. Второй и третий входы блока 11 соединены со статусными выходами соответственно приемного 15 и передающего 16 буферов магазинной памяти, четвертый вход - со статусным выходом приемопередатчика 1, пятый вход - с выходом элемента ИЛИ 14, а выход - с входом прерывания блока 2 управления, статусные входы которого соединены с выходами блока 12 триггеров и с соответствующими входами элемента ИЛИ 14, а управляющий выход - с входом сброса блока 12 триггеров, объединяющим входы сброса всех триггеров 13. Установочные входы триггеров 13 подключены к соответствующим информационным выходам преобразователей 10 уровня и входам мультиплексора 9 блока 8 приемников, входы которого соединены с канальными входами устройства, а выход данных - с последовательным входом приемопередатчика 1, последовательный выход которого подключен через мультиплексор 6 и преобразователи 7 уровня блока 5 передатчиков к канальным выходам устройства.

Устройство работает следующим образом.

Информационная посылка в виде последовательдного кода поступает по одному или одновременно нескольким из канальных входов на соответствующий вход преобразователя 10 уровней, где преобразуется в потенциальный вид и с соответствующего выхода которого поступает на один из входов мультиплексора 9 приемников и вход установки соответствующего RS-триггера 13 блока 12 триггеров. Триггер 13 устанавливается, сигнал с его выхода поступает на один из статусных входов блока 2 управления и элемент ИЛИ 14, с выхода которого подается на пятый вход блока 11 обработки прерываний, формирующего в ответ на своем выходе сигнал прерывания, поступающий на вход прерывания блока 2 управления и вызывающий переход блока управления от выполнения основной программы к обслуживанию прерывания. В ходе исполнения подпрограммы прерывания блок 2 управления анализирует состояние блока 11 обработки прерываний, вытесняя источник прерывания, и считывает содержимое своих статусных входов, отражающее состояние блока 12 триггеров. Позиционный код, считанный блоком 2 управления из блока триггеров, показывает, из каких каналов связи пришли информационные посылки к моменту формирования сигнала прерывания. Считав этот позиционный код, блок 2 управления принимает в соответствии с заложенной программой решение о степени приоритета того или иного канала связи и затем посылает управляющий код на вход-выход данных блока 8 приемников, переключая выход данных мультиплексоров 9 на соответствующий выход преобразователя 10 уровня. Теперь все последующие информационные посылки из выбранного таким образом канала связи проходят на вход приемопередатчика 1, где они преобразуются из последовательного вида в параллельный. Каждый раз по окончании преобразования приемопередатчик 1 формирует на своем статусном выходе сигнал, поступающий на четвертый вход блока 11 обработки прерываний, который в ответ формирует на своем выходе прерывания сигнал, поступающий на вход прерывания блока 2 управления и вызывающий переход блока управления к выполнению подпрограммы обслуживания прерывания. В результате анализа состояния блока 11 обработки прерываний блок 2 управления в данном случае считывает из входа-выхода данных приемопередатчика 1 слово данных и записывает его в инкрементном режиме в приемный буфер 15 магазинной памяти, после чего размаскирует статусный выход буфера 15, соединенный с вторым входом прерывания блока 11 обработки прерываний.

Размаскированный сигнал на статусном выходе буфера 15 появляется лишь в случае, когда буфер 15 полностью считан, поэтому в данном случае блок 11 не формирует сигнал прерывания для блока 2 управления.

В дальнейшем прием данных с выбранного канала связи происходит аналогично описанному выше вплоть до момента окончания передачи массива данных, после чего блока 2 управления через вход управления по шине данных программирует соответствующим образом блок 17 прямого доступа в память. По окончании программирования блок 17 осуществляет перепись содержимого буфера 15 в память ЭВМ, после чего буфер 15 формирует на своем статусном выходе сигнала, по которому блок 11 обработки прерываний вырабатывает сигнал прерывания, поступающий на вход прерывания блока 2 управления, который таким образом информируется, что операция переписи массива данных из канала связи в ЭВМ закончилась. После этого блок 2 управления вновь маскирует статусный выход буфера 15 и устройство, таким образом, оказывается подготовленным к дальнейшему взаимодействию ЭВМ с каналами связи.

Если инициатором передачи данных выступает ЭВМ, то на выходе прерывания блока 17 прямого доступа в память появляется сигнал, поступающий на первый вход блока 11 обработки прерываний, который формирует сигнал, поступающий на вход прерывания блок 2 управления и вызывающий переход блок управления к выполнению подпрограммы обслуживания прерывания. В ходе исполнения подпрограммы блок 2 управления анализирует состояние блока 11 обработки прерываний, вытесняя источник прерываний, и считывает из ЭВМ через второй вход-выход данных блока 17 информацию о массиве данных, включающую, в частности, размер массива и номер канала связи, в которой будут переданы эти данные. В дальнейшем блок 2 управления через вход управления по шине данных программирует соответствующим образом блок 17 прямого доступа в память. По окончании программирования блок 17 осуществляет перепись массива данных из памяти ЭВМ в передающий буфер 16 магазинной памяти, после чего блок 2 управления размаскирует статусный выход буфера 16. Размаскированный сигнал на статусном выходе буфера 16 появляется лишь в случае, когда буфер 16 полностью считан, поэтому в данном случае блок 11 не формирует сигнал прерывания для блока 2 управления. Теперь блок управления через вход данных посылает управляющий код в блок 5 передатчиков, переключая тем самым последовательный выход приемопередатчика 1 на соответствующий канальный выход устройства через мультиплексор 6 передатчика и преобразователи 7 уровня, после чего в декрементном режиме пересылает данные из буфера 16 на вход-выход данных приемопередатчика 1, с последовательного выхода которого эти данные в последовательном виде проходят через блок 5 передатчиков в выбранный канальный выход устройства. По окончании передачи каждого слова данных приемопередатчик 1 формирует на своем статусном выходе сигнал, поступающий на четвертый вход блока 11 обработки прерываний и вызывающий появление на выходе блока 11 сигнала прерывания, поступающего на вход прерывания блока 2 управления, по которому тот определяет готовность приемопередатчика 1 к приему из буфера 16 следующего слова данных.

После того, как массив данных из передающего буфера 16 полностью считан, на статусном выходе буфера 16 появляется сигнал, по которому блок 11 формирует сигнал прерывания для блока 2 управления, в результате чего статусный выход буфера 16 вновь маскируется и устройство, таким образом, оказывается подготовленным к дальнейшему обеспечению взаимодействия ЭВМ с каналами связи.

В процессе обмена данными между буферами 15, 16 и каналами связи блок 2 управления может осуществлять анализ достоверности передаваемой информации, диагностику средств передачи, а также организует обмен данными между ЭВМ и каналами связи по определенному протоколу.

В реализованном варианте заявляемого устройства блок управления содержит однокристальную микроЭВМ типа К1816ВЕ51 (Весноватвов М.Г., Карацюба Г. В. , Павлов В.В., Старшина В.А. Перспективные однокристальные ЭВМ // Микропроцессорные средства и системы, 1987, N 2, с.7-8) и память программ на УФППЗУ типа К573РФ6. Двунаправленная шина данных микроЭВМ объединена с входами данных памяти программ, с входами-выходами данных памяти данных и является входами-выходами данных блока 2 управления, причем вход внешнего прерывания INTO микроЭВМ является входом прерывания блока управления.

Информация со статусных входов блока 2 управления через выводы Р1.0... Р1.6 квазидвунаправленного порта Р1 микроЭВМ может быть прочитана, а информация на управляющем выходе блока управления через вывод Р1.7 порта Р1 микроЭВМ установлена специальными командами чтения-записи микроЭВМ. Прерывание программы микроЭВМ инициируется фронтом сигнала, поступающего на вход INTO прерывания, а возврат из прерывания - специальной командой микроЭВМ, после чего микроЭВМ готова к обработке следующего прерывания. Управляющая программа микроЭВМ хранится в памяти программ и запускается при включении питания устройства.

По сравнению с устройством-прототипом предлагаемое устройство за счет исполнения им описанных выше интеллектуальных функций позволяет в несколько раз повысить производительность обмена данными между ЭВМ и каналами связи, причем выигрыш существенно повышается при увеличении объема информации, передаваемой в виде массива данных, оформленного в соответствии с определенным протоколом обмена.

Изобретение может найти широкое применение в составе распределенных систем автоматизации экспериментальных исследований, в особенности имеющих гетерогенную структуру. В таких системах на устройство может быть возложен ряд дополнительных функций, таких, например, как преобразование форматов информационных посылок и т.п., что приводит к повышению качества системы автоматизации в целом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1991 |

|

SU1837303A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Устройство для сопряжения двух микроЭВМ с общим внешним устройством | 1985 |

|

SU1345206A1 |

| ПЕРЕПРОГРАММИРУЕМЫЙ ВЫЧИСЛИТЕЛЬ ДЛЯ СИСТЕМ ОБРАБОТКИ ИНФОРМАЦИИ | 1998 |

|

RU2146389C1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство связи кольцевой оптоволоконной сети | 1988 |

|

SU1689963A1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| ВЫЧИСЛИТЕЛЬ С ПЕРЕПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 1996 |

|

RU2115161C1 |

| Устройство сопряжения многопроцессорной системы | 1987 |

|

SU1575195A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

Изобретение относится к вычислительной технике и может быть использовано в многоканальных устройствах сопряжения ЭВМ с последовательными каналами связи. В устройстве организован обмен данными между ЭВМ и каналами связи с помощью блока управления и двух буферов магазинной памяти, один из которых работает только на ввод, а другой - только на вывод данных. Устройство содержит приемопередатчик, блок управления, блок передатчиков, блок приемников, блок обработки прерываний, блок триггеров, элемент ИЛИ, приемный и передающий буферы магазинной памяти и блок прямого доступа в память. 2 ил.

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛАМИ СВЯЗИ, содержащее приемопередатчик, блок управления, блок передатчиков, блок приемников, блок обработки прерываний и блок триггеров, причем входы-выходы данных блока обработки прерываний, приемопередатчика, блока управления, блока передатчиков и блока приемников объединены шиной данных, выходы блока передатчиков и входы блока приемников соединены с канальными выходами и входами устройства, отличающееся тем, что в него введен элемент ИЛИ, приемный и передающий буферы магазинной памяти и блок прямого доступа в память, при этом входы-выходы данных приемного и передающего буферов магазинной памяти и вход управления блока прямого доступа в память подключены к шине данных устройства, выход данных приемного и вход данных передающего буферов соединены с первым входом-выходом данных блока прямого доступа в память, второй вход-выход данных которого является входом-выходом данных устройства, а выход прерывания подключен к первому входу блока обработки прерываний, второй и третий входы которого

соединены со статусными выходами соответственно приемного и передающего буферов магазинной памяти, четвертый вход - со статусным выходом приемопередатчика, пятый вход - с выходом элемента ИЛИ, а выход - с входом прерывания блока управления, статусные входы которого соединены с выходами блока триггеров и входы прерывания - с соответствующими входами элемента ИЛИ, а управляющий выход - с входом сброса блока триггеров, установочные входы которого подключены к соответствующим информационным выходом блока приемников, выход данных которого соединен последовательным с входом данных приемопередатчика, последовательный выход которого подключен к входу данных блока передатчиков.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1474659A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-07-30—Публикация

1990-08-23—Подача