Предлагаемое техническое решение относится к вычислительной технике и является усовершенствованием системного контроллера (заяв. N 96103215, Россия, 27.02.1996). Цель изобретения - расширение возможностей адресации процессора в системе контроля и управления различными объектами промышленности в составе многопроцессорных вычислительных комплексов.

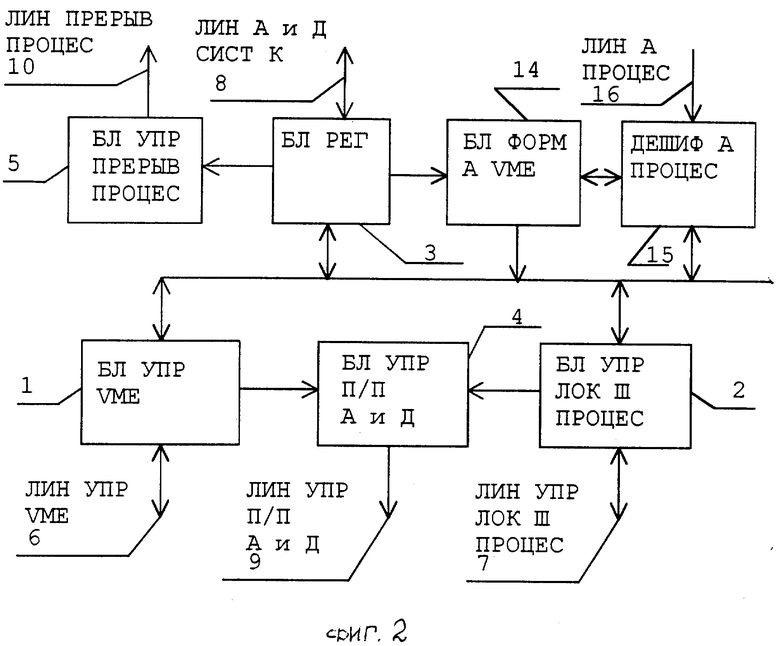

Прототип, системный контроллер (VIC068/VAC068, CYPRESS SEMICONDUCTOR DATA BOOK, BICMOS, CMOS, 1992, p. 11.1 - 11.26), содержит блок управления шиной VME (БЛ УПР VME), к входам/выходам которого подсоединены входы/выходы линий управления шины VME (ЛИН УПР VME), блок управления локальной шиной процессора (БЛ УПР ЛОК Ш ПРОЦЕС), к входам/выходам которого подсоединены входы/выходы линий управления локальной шины процессора (ЛИН УПР ЛОК Ш ПРОЦЕС), а к выходам блока управления шиной VME и блока управления локальной шиной процессора подсоединены входы блока управления приемниками/передатчиками адреса и данных (БЛ УПР П/П А и Д), выходы которого подсоединены к линиям управления приемниками/передатчиками адреса и данных (ЛИН УПР П/П А и Д), блок регистров (БЛ РЕГ), к входам/выходам которого подсоединены линии адреса и данных системного контроллера (ЛИН А и Д СИСТ К), а к выходам которого подсоединены входы блока управления прерываниями процессора (БЛ УПР ПРЕРЫВ ПРОЦЕСС), выходы которого подсоединены к линиям прерываний процессора (ЛИН ПРЕРЫВ ПРОЦЕС), при этом входы/выходы блока управления шины VME подсоединены к входам/выходам блока управления локальной шины процессора и к входам/выходам блока регистров (см. фиг. 1).

Этот системный контроллер ориентирован на использование в системах на основе процессоров 68ххх. Также возможна работа контроллера с процессорами семейства х86 (i386, i486). Недостатком контроллера при работе в системах на основе процессора х86 является невозможность доступа к шине VME со стороны процессора, работающего в реальном режиме. При работе в таких операционных системах, как MS-DOS, Windows, это, в свою очередь, не позволяет использовать находящиеся на VME устройства как обычные системные ресурсы.

Задача, на решение которой было направлено данное изобретение, состояла в расширении возможностей адресации процессора в системе и обеспечении доступа к устройствам на шине VME, используя стандартные средства операционных систем, таких как MS-DOS и Windows.

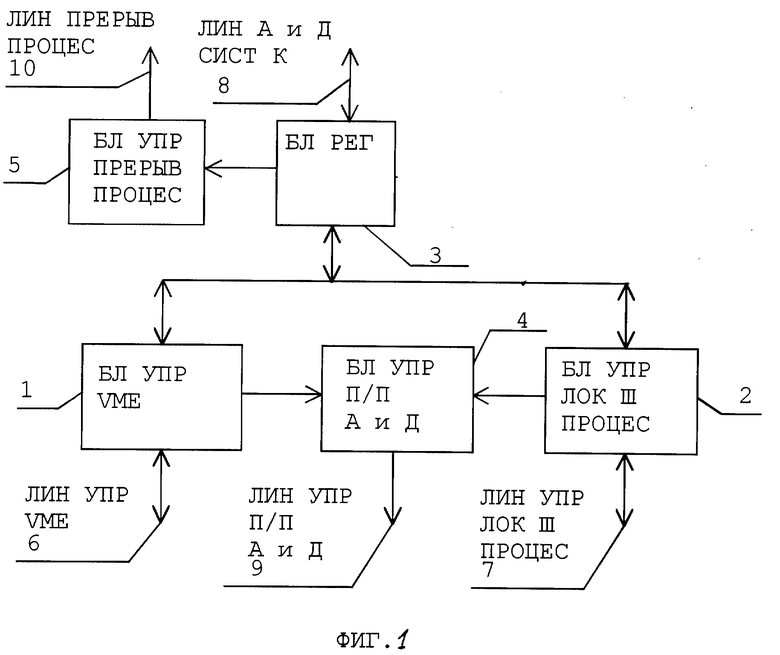

Для решения этой задачи системный контроллер, содержащий блок управления шиной VME (БЛ УПР VME), к входам/выходам которого подсоединены входы/выходы линий управления шины VME (ЛИН УПР VME), блок управления локальной шиной процессора (БЛ УПР ЛОК Ш ПРОЦЕС), к входам/выходам которого подсоединены входы/выходы линий управления локальной шины процессора (ЛИН УПР ЛОК Ш ПРОЦЕС), а к выходам блока управления шиной VME и блока управления локальной шиной процессора подсоединены входы блока управления приемниками/передатчиками адреса и данных (БЛ УПР П/П А и Д), выходы которого подсоединены к линиям управления приемниками/передатчиками адреса и данных (ЛИН УПР П/П А и Д), блок регистров (БЛ РЕГ), к входам/выходам которого подсоединены линии адреса и данных системного контроллера (ЛИН А и Д СИСТ К), а к выходам которого подсоединены входы блока управления прерываниями процессора (БЛ УПР ПРЕРЫВ ПРОЦЕС), выходы которого подсоединены к линиям прерываний процессора (ЛИН ПРЕРЫВ ПРОЦЕС), при этом входы/выходы блока управления шины VME подсоединены к входам/выходам блока управления локальной шины процессора и к входам/выходам блока регистров, снабжен блоком формирования адреса шины VME (БЛ ФОРМ А VME), входы которого подсоединены к выходам блока регистров (БЛ РЕГ), а выходы которого подсоединены к входам блока управления шиной УМЕ (БЛ УПР VME), и дешифратором адреса процессора (ДЕШИФ А ПРОЦЕС), входы которого подключены к линиям адреса процессора (ЛИН А ПРОЦЕС), а входы/выходы которого подсоединены к входам/выходам блока управления локальный шины процессора (БЛ УПР ЛОК Ш ПРОЦЕС) и к входам/выходам блока формирования адреса шины VME (БЛ ФОРМ A VME).

При работе процессора в реальном режиме формирование адреса на шине VME производится введенным в системный контроллер блоком формирования адреса шины VME (БЛ ФОРМ A VME). Данный блок позволяет процессору обращаться к ресурсам на шине VME во всем диапазоне адресов VME (4 Гбайта) через окно размером 64 Кбайта, которое отображается в область адресов процессора, доступных при работе в операционных системах MS-DOS и Windows. Факт обращения процессора в выделенное окно фиксируется введенным в системный контроллер дешифратором адреса процессора (ДЕШИФ А ПРОЦЕС). Обращения могут производиться в адресных пространствах VME A32, A24, A16.

В итоге контроллер приобретает системную функцию по расширению возможностей адресации процессора, что позволяет расширить круг используемого программного обеспечения.

Предлагаемое изобретение поясняется чертежом, где на фиг. 2 представлена блок-схема предлагаемого системного контроллера.

Системный контроллер содержит

1 - блок управления шиной VME,

2 - блок управления локальной шиной процессора,

3 - блок регистров,

4 - блок управления приемниками/передатчиками адреса и данных,

5 - блок управления прерываниями процессора,

6 - линии управления шины VME,

7 - линии управления локальной шины процессора,

8 - линии адреса и данных системного контроллера,

9 - линии управления приемниками/передатчиками адреса и данных,

10 - линии прерываний процессора,

11 - блок формирования адреса шины VME,

12 - дешифратор адреса процессора,

13 - линии адреса процессора.

Работа контроллера.

В 1996 г. в КБ Корунд-М был собран и испытан модуль БТ02-201, в состав которого входит предлагаемый системный контроллер. Модуль работает на базе микропроцессора i486DX, -DX2, -DX4. Системный контроллер реализован на базе программируемой пользователем микросхемы XC4005 (фирма XILINX) и программируемых логических матриц PAL22V10, MACH210A (фирма AMD). Блок управления шины VME выполняет следующие функции:

- запросчика прерывания шины VME (interrupter);

- обработчика прерывания шины VME (interrupt handler);

- формирования последовательной цепочки подтверждения запроса на прерывание шины VME (iack daisy-chain driver);

- запросчика шины VME (requester);

- арбитра шины VME (arbiter);

- формирователя последовательной цепочки подтверждения захвата шины (bus request daisy-chain driver);

- обеспечения режима ведущего (master);

- поддержки режима ведомого (slave).

Запросчик прерывания программируется вектором прерывания и уровнем линии прерывания, выставляемых модулем в цикле подтверждения прерывания шины VME.

Обработчик прерывания шины VME аппаратно обрабатывает запросы прерываний, выставленных на шине VME. Приоритет прерываний жестко задан.

Запросчик шины VME пытается захватить шину всякий раз, когда центральный процессор обращается к VME или когда происходит цикл обращения к ОЗУ при одновременном доступе со стороны VME.

Режим ведущего программируется адресными модификаторами, выставляемыми на VME.

Блок ведомого программируется адресными модификаторами и старшими разрядами линий адреса шины VME.

В свете выполнения задачи, решаемой изобретением, блок регистров 3 фиксирует факт работы процессора в реальном режиме и воздействует на блок формирования адреса шины VME 11. Дешифратор адреса процессора 12 дешифрирует значение адреса на линиях адреса процессора 13 и выдает воздействие на блок формирования адреса шины VME 11. В свою очередь, блок 11 формирует адрес, адресные модификаторы и выдает воздействие на блок управления шиной VME 1, который по линиям 6 выставляет сигналы управления на шину VME. Блок 6 воздействует на блок управления приемниками/передатчиками адреса и данных 4, который выставляет сигналы направления и разрешения передачи адреса и данных.

Результаты испытаний показали надежную работу системного контроллера при работе с операционными системами MS-DOS, Windows.

Использование в промышленных системах данного изобретения предоставит существенную возможность - доступ к устройствам на VME со стороны процессора, работающего в реальном режиме. Это позволяет использовать такие операционные системы, как MS-DOS, Windows и разработанное для них программное обеспечение, что принесет системным контроллерам этого типа коммерческий успех на рынке.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМНЫЙ КОНТРОЛЛЕР | 1996 |

|

RU2110834C1 |

| ПЕРЕПРОГРАММИРУЕМЫЙ ВЫЧИСЛИТЕЛЬ ДЛЯ СИСТЕМ ОБРАБОТКИ ИНФОРМАЦИИ | 1998 |

|

RU2146389C1 |

| ВЫЧИСЛИТЕЛЬ С ПЕРЕПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 1996 |

|

RU2115161C1 |

| ПРОГРАММИРУЕМЫЙ ЛОГИЧЕСКИЙ КОНТРОЛЛЕР | 1995 |

|

RU2101757C1 |

| Устройство приоритетного прерывания | 1990 |

|

SU1793440A1 |

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ ПОТОКОВ ДАННЫХ, СЧИТЫВАЕМЫХ ИЗ ОЗУ | 2011 |

|

RU2475817C1 |

| ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА И БЛОК ОБРАБОТКИ ВСТРЕЧНЫХ ЗАПРОСОВ | 2005 |

|

RU2308075C1 |

| УСТРОЙСТВО ОБРАБОТКИ ИНФОРМАЦИИ | 2011 |

|

RU2480820C1 |

| ПОДСИСТЕМА ПАМЯТИ ЯДРА МИКРОПРОЦЕССОРА | 2011 |

|

RU2475822C1 |

Изобретение относится к системным контроллерам. Техническим результатом является расширение возможностей адресации процессора в системе контроля и управления различными объектами промышленности в составе микропроцессорных вычислительных комплексов. Системный контроллер содержит блок управления шиной VME, блок управления локальной шиной процессора, блок регистров, блок управления приемниками/передатчиками адреса и данных, блок управления прерываниями процессора, линии управления шины VME, линии управления локальной шины процессора, линии адреса и данных системного контроллера, линии управления приемниками/передатчиками адреса и данных, линии прерываний процессора, блок формирования адреса шины VME, входы которого подсоединены к выходам блока регистров, а выходы - к входам блока управления шиной VME и дешифратора адреса процессора, входы которого подключены к линиям адреса процессора, а входы/выходы - к входам/выходам блока управления локальной шиной процессора и к входам/выходам блока формирования адреса шины VME. 2 ил.

Системный контроллер, содержащий блок управления шиной VME, к входам/выходам которого подсоединены входы/выходы линий управления шины VME, блок управления локальной шиной процессора, к входам/выходам которого подсоединены входы/выходы линий управления локальной шины процессора, а к выходам блока управления шиной VME и блока управления локальной шиной процессора подсоединены входы блока управления приемниками/передатчиками адреса и данных, выходы которого подсоединены к линиям управления приемниками/передатчиками адреса и данных, блок регистров, к входам/выходам которого подсоединены линии адреса и данных системного контроллера, а к выходам - входы блока управления прерываниями процессора, выходы которого подсоединены к линиям прерываний процессора, при этом входы/выходы блока управления шиной VME подсоединены к входам/выходам блока управления локальной шиной процессора и к входам/выходам блока регистров, отличающийся тем, что он снабжен блоком формирования адреса шины VME, входы которого подсоединены к выходам блока регистров, а выходы - к входам блока управления шиной VME и дешифратора адреса процессора, входы которого подключены к линиям адреса процессора, а входы/выходы - к входам/выходам блока управления локальной шиной процессора и к входам/выходам блока формирования адреса шины VME.

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

| Cypress Semiconductor | |||

| Data Book, BICMOS, CMOSS, 1992, p.11.1 - 11.26 | |||

| Устройство для контроля выполнения программ | 1988 |

|

SU1541618A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1543409A1 |

| US 4553204 A, 12.11.85 | |||

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

Авторы

Даты

1999-01-10—Публикация

1996-12-04—Подача