Изобретение относится к области коммутационных сред для вычислительных систем и может быть использовано как составная часть высокоскоростного последовательного мультиканального приемопередатчика.

Известен передатчик с обратной связью, состоящий из тактового генератора, мультиплексора, сдвигового регистра, регулятора импульсной характеристики, выходного буфера, источника стабильного тока, основного цифроаналогового преобразователя, связанного с контроллером, приемником и фазовой автоподстройкой частоты (Beukema Т., Soma M., Sekandr К.A 6.4-Gb/s CMOS serdes core with feed-forward and decision-feedback equalization. // IEEE Journal of Solid-State Circuits, vol. 40, pp.2633-2645, Dec. 2005.)

Недостатком описанного передатчика является достаточно большая потребляемая мощность, поскольку отсутствует зависимость размаха дифференциального напряжения выходного сигнала от текущей глубины коррекции межсимвольной интерференции.

Задачей изобретения является обеспечение работы устройства для мультиканальных приемопередающих систем, а также систем на кристалле.

Указанный задача решается тем, что передатчик со следящей обратной связью, состоящий из тактового генератора, мультиплексора, сдвигового регистра, регулятора импульсной характеристики, декодера регулятора импульсной характеристики, выходного буфера, источника стабильного тока, основного цифроаналогового преобразователя, связанного с контроллером, приемником и фазовой автоподстройкой частоты, согласно изобретению снабжен дополнительным цифроаналоговым преобразователем, связанным с выходным буфером, и декодером дополнительного цифроаналогового преобразователя, связанного с приемником, для обеспечения контроля минимально допустимого размаха дифференциального напряжения выходного сигнала передатчика от текущей глубины коррекции межсимвольной интерференции приемника.

Технический результат от использования изобретения состоит в уменьшении потребляемой мощности передатчика путем обеспечения работы устройства для мультиканальных приемопередающих систем, а также систем на кристалле.

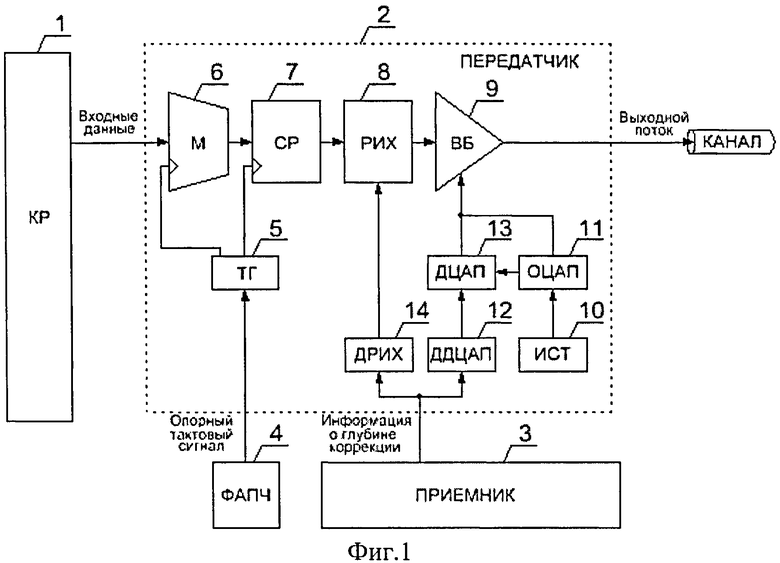

Изобретение поясняется чертежом, где изображена структурная схема передатчика со следящей обратной связью.

Устройство состоит из контроллера (КР) 1, передатчика (ПЕРЕДАТЧИК) 2, приемника (ПРИЕМНИК) 3, фазовой автоподстройки частоты (ФАПЧ) 4. Передатчик 2 состоит из тактового генератора (ТГ) 5, мультиплексора (М) 6, сдвигового регистра (СР) 7, регулятора импульсной характеристики (РИХ) 8, выходного буфера (ВБ) 9, источника стабильного тока (ИСТ) 10, основного цифроаналогового преобразователя (ОЦАП) 11, декодера дополнительного цифроаналогового преобразователя (ДДЦАП) 12, дополнительного цифроаналогового преобразователя (ДЦАП) 13, декодера регулятора импульсной характеристики (ДРИХ) 14.

Передатчик работает следующим образом. Тактовый генератор (ТГ) 5 формирует тактовые сигналы для мультиплексора (М) 6 и сдвигового регистра (СР) 7 из опорного сигнала, приходящего с фазовой автоподстройки частоты (ФАПЧ) 4. Блок мультиплексора (М) 6 осуществляет преобразование параллельной низкочастотной шины данных, поступающей из контроллера (КР) 1, в последовательный высокочастотный поток. Передавая эти данных по каналу, происходит ослабление, имеющее частотно-зависимый характер, что приводит к возникновению межсимвольной интерференции. Совокупность сдвигового регистра (СР) 7, регулятора импульсной характеристики (РИХ) 8 и выходного буфера выходного буфера (ВБ) 9 выполняет роль эквалайзера, необходимого для компенсации межсимвольной интерференции. Эквалайзер основан на принципе работы не рекурсивного фильтра с конечной импульсной характеристикой (КИХ).

С выхода мультиплексора (М) 6 поток подается на вход сдвигового регистра (СР) 7, выполняющего роль линии задержки. Количество элементов линии задержки определяется порядком реализуемого фильтра. Время задержки одного элемента в линии соответствует единичному интервалу обрабатываемого потока данных. Выходной сигнал сдвигового регистра (СР) 7 представляет собой совокупность последовательных потоков, где каждый последующий сдвинут относительно предыдущего на один единичный интервал. Задача регулятора импульсной характеристики (РИХ) 8 - размножить входные потоки, поступающие из сдвигового регистра (СР) 7 в пропорциях, соответствующих коэффициентам, сформированным на выходе декодера регулятора импульсной характеристики (ДРИХ) 14. Блок регулятора импульсной характеристики (РИХ) 8 реализован в виде дискретной многоканальной мультиплексирующей матрицы с цифровым управлением, в процессе работы перераспределяя вклад каждого входного потока в суммарный поток, формируемый на выходе выходного буфера (ВБ) 9.

Задача выходного буфера (ВБ) 9 заключается не только в том, чтобы выполнять роль сумматора конечной импульсной характеристики (КИХ) фильтра, но и обеспечить требуемые электрические характеристики выходного сигнала, поступающего в канал. Максимальный выходной размах на выходе выходного буфера (ВБ) 9 определяется суммой токов, поступающих с основного цифроаналогового преобразователя (ОЦАП) 11 и дополнительного цифроаналогового преобразователя (ДЦАП) 13. В отсутствии выходного тока с дополнительного цифроаналогового преобразователя (ДЦАП) 13 выходной ток основного цифроаналогового преобразователя (ОЦАП) 11 должен обеспечивать минимально допустимый размах дифференциального напряжения выходного сигнала выходного буфера (ВБ) 9, соответствующий требованиям спецификации. В процессе работы выходной ток основного цифроаналогового преобразователя (ОЦАП) 11 постоянен и работает от опорного тока сформированного источника стабильного тока (ИСТ) 10. Опорный ток для дополнительного цифроаналогового преобразователя (ДЦАП) 13 определяется как порция выходного тока основного цифроаналогового преобразователя (ОЦАП) 11.

Из блока приемника (ПРИЕМНИК) 3 на входы декодера регулятора импульсной характеристики (ДРИХ) 14 и декодера дополнительного цифроаналогового преобразователя (ДДЦАП) 12 поступает информация о глубине коррекции межсимвольной интерференции, которую должен сформировать передатчик (ПЕРЕДАТЧИК) 2. Если глубина коррекции равна нулю, на выходе декодера регулятора импульсной характеристики (ДРИХ) 14 будет сформирован логический код, при котором мультиплексирующая матрица регулятора импульсной характеристики (РИХ) 8 во всех разрядах пропускает поток, соответствующий нулевому порядку конечной импульсной характеристики (КИХ) фильтра. Другими словами, все коэффициенты фильтра за исключением коэффициента нулевого порядка равны нулю. При этом выходной управляющий сигнал декодера дополнительного цифроаналогового преобразователя (ДДЦАП) 12 соответствует нулевому току на выходе дополнительного цифроаналогового преобразователя (ДЦАП) 13. По мере увеличения глубины коррекции, код на выходе декодера регулятора импульсной характеристики (ДРИХ) 14 будет перераспределять выходные потоки регулятора импульсной характеристики (РИХ) 8, увеличивая коэффициенты не нулевых порядков конечной импульсной характеристики (КИХ) фильтра. Одновременно с увеличением глубины коррекции увеличивается ток на выходе дополнительного цифроаналогового преобразователя (ДЦАП) 13. Добавка к основному току основного цифроаналогового преобразователя (ОЦАП) 11 увеличивает максимальный размах выходного дифференциального сигнала на выходе выходного буфера (ВБ) 9 пропорционально увеличению глубины коррекции. Это означает, что минимально допустимый размах дифференциального напряжения на выходе выходного буфера (ВБ) 9 будет оставаться постоянным. Следовательно, с одной стороны выходной буфер (ВБ) 9 обеспечивает минимально допустимый размах дифференциального напряжения выходного сигнала, соответствующий требованиям спецификации, а с другой стороны потребляет минимально необходимую мощность для текущего значения глубины коррекции межсимвольной интерференции.

Таким образом, изобретение позволяет уменьшить потребляемую мощность передатчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИЕМНИК С ГИБРИДНЫМ ЭКВАЛАЙЗЕРОМ | 2013 |

|

RU2530219C1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| Устройство для адаптивного приема сигналов | 1974 |

|

SU518011A1 |

| Устройство преобразования сигналов для каналов тональной частоты | 1989 |

|

SU1709551A1 |

| СПОСОБ ЦИФРОАНАЛОГОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2156029C2 |

| ДУПЛЕКСНЫЙ МОДЕМ | 1998 |

|

RU2147791C1 |

| АВТОМАТИЗИРОВАННОЕ РАБОЧЕЕ МЕСТО ОПЕРАТОРА УПРАВЛЕНИЯ ВОЗДУШНЫМ ДВИЖЕНИЕМ | 2001 |

|

RU2219586C2 |

| ЛИНЕАРИЗОВАННАЯ ЦИФРОВАЯ АВТОМАТИЧЕСКАЯ РЕГУЛИРОВКА УСИЛЕНИЯ | 1996 |

|

RU2158474C2 |

| Способ борьбы с межсимвольными искажениями цифровых сигналов | 2018 |

|

RU2692429C1 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1256213A1 |

Изобретение относится к области коммутационных сред для вычислительных систем и может быть использовано как составная часть высокоскоростного последовательного мультиканального приемопередатчика. Технический результат заключается в уменьшении потребляемой мощности передатчика. Передатчик со следящей обратной связью содержит тактовый генератор, связанный с фазовой автоподстройкой частоты, мультиплексор, связанный с контроллером, сдвиговый регистр, регулятор импульсной характеристики, декодер регулятора импульсной характеристики, выходной буфер, источник стабильного тока, основной цифроаналоговый преобразователь, при этом снабжен дополнительным цифроаналоговым преобразователем и декодером дополнительного цифроаналогового преобразователя, связанным с приемником, для обеспечения контроля минимально допустимого размаха дифференциального напряжения выходного сигнала передатчика от текущей глубины коррекции межсимвольной интерференции приемника. 1 ил.

Передатчик со следящей обратной связью, состоящий из тактового генератора, связанного со сдвиговым регистром, фазовой автоподстройкой частоты и мультиплексором, связанным с контроллером и сдвиговым регистром, связанным с регулятором импульсной характеристики, связанным с выходным буфером и декодером регулятора импульсной характеристики, связанным с приемником, основного цифроаналогового преобразователя, связанного с источником стабильного тока и выходным буфером, отличающийся тем, что передатчик снабжен дополнительным цифроаналоговым преобразователем и декодером дополнительного цифроаналогового преобразователя, при этом дополнительный цифроаналоговый преобразователь связан с выходным буфером и основным цифроаналоговым преобразователем, а декодер дополнительного цифроаналогового преобразователя связан с приемником и дополнительным цифроаналоговым преобразователем для обеспечения контроля минимально допустимого размаха дифференциального напряжения выходного сигнала передатчика от текущей глубины коррекции межсимвольной интерференции приемника.

| Beukema Т., et al, "К.A 6.4-Gb/s CMOS SerDes Core With Feed-Forward and Decision-Feedback Equalization" | |||

| // IEEE Journal of Solid-State Circuits, vol | |||

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

| СВЯЗНОЙ ПРИЕМНИК С АДАПТИВНЫМ ЭКВАЛАЙЗЕРОМ, КОТОРЫЙ ИСПОЛЬЗУЕТ КАНАЛЬНУЮ ОЦЕНКУ | 2004 |

|

RU2345496C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ГИБРИДНОЙ КОРРЕКЦИИ С РЕШАЮЩЕЙ ОБРАТНОЙ СВЯЗЬЮ | 2005 |

|

RU2407197C2 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

Авторы

Даты

2015-08-10—Публикация

2013-06-18—Подача