Предложение относится к: средствам цифровой обработки сигналов, например цифровым фильтрам, и может найти применение в устройствах фильтрации, прогнозирования процессов, дифференцирования, управления и перспективных разработках больших и сверхбольших интегральных микросхем с гибкой архитектурой вычислений. Известен рекурсивный цифровой фильтр, в котором предусмотрена организация перестройки режима с помощью изменения коэффициентов фильтра [1].

Для этого память разбивается на n-зон, где n - число различных модификаций частотных характеристик цифрового фильтра, каждая из зон предназначена для хранения значений коэффициентов соответствующих тому или иному виду характеристики сигнала.

Известное устройство требует дополнительной памяти для параметров модели, что может оказаться критическим фактором при разработке или использовании сигнальных процессоров и однокристальных специализированных микроЭВМ.

Известно устройство для цифровой обработки сигналов, содержащее буферные регистры, тактовый генератор, ключи и волновую процессорную матрицу, которая состоит из блоков вычисления отсчетов сигналов. Первый из которых является ведущим [2]. Данное устройство выбрано в качестве прототипа.

В устройстве входной поток отсчетов распространяется вправо по волновой процессорной матрице, инициируя математические операции во всех блоках, образуя таким образом первый волновой фронт (первую рекурсию). Затем прошедшие цифровую обработку данные подаются в обратном направлении, образуя следующий волновой фронт (вторую рекурсию).

Такое управление потоком данных допускает использование более простого потокового языка. Однако в этой схеме требуется также память хранения постоянных коэффициентов. Поэтому применение волновых процессорных матриц для реализации рекурсивных фильтров с перестраиваемыми коэффициентами может вызвать определенные трудности как для потокового языка, так и получения высокого быстродействия. Например, при использовании цифрового фильтра с переменными коэффициентами, например, в синтезаторе речи по Шаферу.

Техническим результатом заявленного устройства является получение гибкой архитектуры вычислений, высокое распараллеливание алгоритмов обработки сигналов и простое программно-аппаратное исполнение.

Технический результат достигается тем, что в устройство, содержащее первый и второй буферные регистры, первую и вторую группу ключей, тактовый генератор и блоки вычисления отсчетов сигналов, введены кольцевые сдвиговые регистры и блок коэффициентов, выход первого буферного регистра соединен с первыми входами блоков вычисления отсчетов сигналов, вход является информационным входом устройства, выходы тактового генератора соединены с управляющими входами первого и второго кольцевых сдвиговых регистров, соответствующие выходы которых подключены к управляющим входам одноименных ключей соответственно первой и второй групп, выходы ключей первой группы соединены со вторыми входами одноименных блоков вычисления отсчетов сигналов, информационные выходы которых подключены ко входам одноименных ключей второй группы, выходы последних соединены со входом второго буферного регистра, выход которого является выходом устройства, и подключены ко входам ключей первой группы, соответствующие выходы блока ввода коэффициентов соединены с информационными входами соответственно третьего и четвертого кольцевых сдвиговых регистров, выходы которых подключены к первому и второму задающим входам первого блока вычисления отсчетов сигналов, первый и второй задающие выходы каждого предыдущего блока вычисления отсчетов сигналов подключены к одноименным задающим входам каждого последующего, первый и второй задающие выходы последнего соединены с управляющими входами соответственно третьего и четвертого кольцевых сдвиговых регистров.

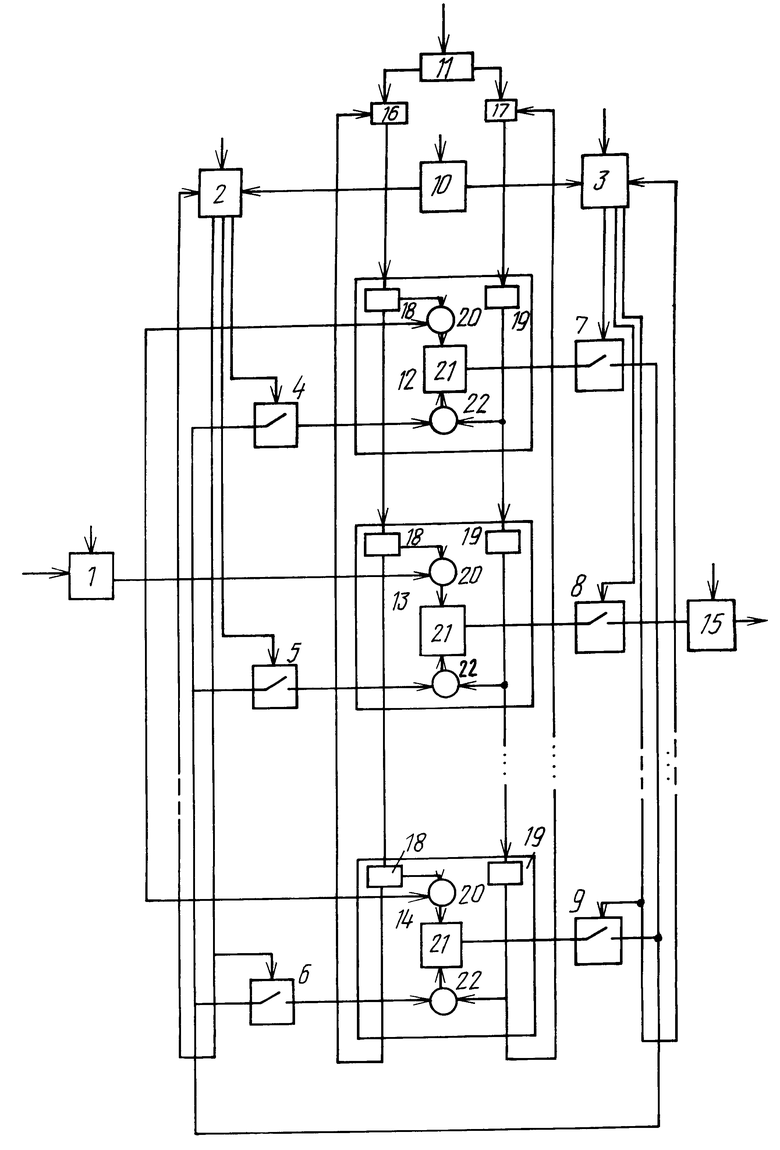

Функциональная схема устройства представлена на чертеже. Устройство содержит первый буферный регистр 1, первый и второй кольцевые сдвиговые регистры 2 и 3, первую группу ключей 4, 5, 6 и вторую группу ключей 7, 8, 9, тактовый генератор 10, блок 11 ввода коэффициентов, блоки 12, 13 и 14 вычисления отсчетов сигналов, второй буферный регистр 15 и третий и четвертый кольцевые сдвиговые регистры 16 и 17. Блок 11 ввода коэффициента имеет информационную шину для связи с внешними устройствами.

Каждый блок вычисления отсчетов сигналов, например, для рекурсивного фильтра состоит из элементов памяти коэффициентов соответственно 18 и 19, умножителя 20, сумматора 21 и умножителя 22. Блок синхронизации на чертеже не показан. Регистры 1, 2, 3, 15, 16 и 17 и тактовый генератор 10 могут управляться от блока синхронизации.

Устройство работает следующим образом.

Устройство цифровой обработки сигнала реализует вычислительный алгоритм дискретно-разностной формы

y(nT)=a0X(nT)+a1x[(n - 1)T]+ ... + arX[(n-k) T - b1Y[(n-1)T]-b2Y[(n-2)T] - ...-brY[(n-k)T]

где

x[(n-i)T] и Y[(n-i)T] - временные отсчеты в моменты времени t = (n-i)T соответственно входного сигнала и выходного обработанного сигнала. Для входных отсчетов i = 0,l, ..., k, для выходных отсчетов j = 1, 2,..., k; T - период дискретности; ai и bi -коэффициенты.

Подобным алгоритмом описываются процессы фильтрации, регулирования и другие.

Для реализации вычислительного алгоритма (1) используется смещенно-временной способ распараллеливания. Для предельного распараллеливания вводится k - блоков вычисления отсчетов сигналов, где k - показатель уравнения (1) (на чертеже представлен случай для k=3), блок имеет два элемента памяти 18 и 19 (например, регистры). Один для коэффициента ai, другой для bi.

Для функционирования устройства цифровой обработки сигнала необходимо обеспечить совмещение сигналов заданных временных отсчетов потока данных с пространственным перемещением коэффициентов внутри устройства. Причем это совмещение может быть как синхронным, так и асинхронным. В последнем случае необходимо до начала временного отсчета произвести перемещение коэффициентов в элементы памяти 18 и 19 каждого блока вычисления отсчетов сигналов посредством блока ввода коэффициентов 11 и регистров 16 и 17.

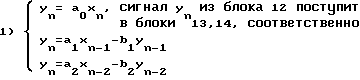

Рассмотрим работу устройства второго порядка

Yn = a0Xn + a1Xn-1 + a2Xn-2 - b1Yn-1 - b2Yn-2.

В этом случае в блок 12 записывают коэффициент a0. Далее соответственно в блок 13 коэффициенты a1, b1, в блок 14 коэффициенты a2, b2 в n-й момент времени входной сигнал xn из буферного регистра 1 поступает в блоки 12, 13 и 14 и инициирует вычислительный процесс, который будет выполняться по следующей схеме:

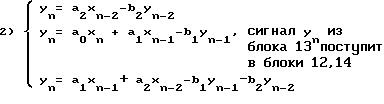

В следующий момент времени

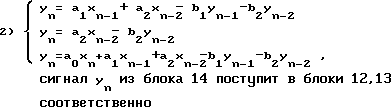

В следующий момент времени

Это происходит следующим образом.

Для первого этапа вычисленное в блоке 12 значение Yn = a0xn поступит на второй буферный регистр 15 и через открытые ключи 5 и 6 первой группы на вторые входы блоков 13 и 14, при этом ключ 4 будет закрыт сигналом управления с регистра 2.

В следующий момент времени обработку осуществляют в блоке 13 и соответственно вычисленный отсчет поступит через ключи 4 и 6 на вторые входы блоков 12 и 14, при этом ключ 5 будет закрыт.

Для третьего этапа обработку осуществляет блок 14 и вычисленные отсчеты поступают через открытые ключи 4 и 5 на вторые входы блоков 12 и 13, ключ 6 будет закрыт. Управление ключами производят посредством кольцевых сдвиговых регистров 2 и 3, однако они могут управляться и программно.

Таким образом, осуществляют параллельную цифровую обработку сигналов, например, для модели рекурсивного фильтра.

Число блоков вычисления отсчетов сигналов может быть изменено в зависимости от решаемых математических операций.

Источники информации

1. Цифровые процессоры обработки сигнала / Под ред. Остапенко А.Г. -М.: Радио и связь, 1994, с.70-73, рис. 2.24 и 2.26.

2. Сверхбольшие интегральные схемы и современная обработка сигналов / Под ред. Гуна С. , Уайтхауса X., Кайлата Т. -М.: Радио и связь, 1989, с. 140-141, рис. 7.4 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ | 1996 |

|

RU2105349C1 |

| СПОСОБ КОНТРОЛЯ ТОКОРАСПРЕДЕЛЕНИЯ ПО КОМПЛЕКТАМ ЩЕТОК УЗЛА ТОКОСЪЕМА ЭЛЕКТРИЧЕСКОЙ МАШИНЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2178609C2 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Устройство для ортогонального преобразования цифровых сигналов по функциям Хаара | 1983 |

|

SU1116435A1 |

| Устройство для выполнения обратного преобразования Хаара | 1983 |

|

SU1104528A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Хаару | 1982 |

|

SU1061150A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ СИТУАЦИЙ | 2000 |

|

RU2198426C2 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| Устройство для контроля изоляции цепей генераторного напряжения с непосредственным водяным охлаждением обмоток статора | 1991 |

|

SU1788481A1 |

Предложение относится к средствам цифровой обработки сигналов, например цифровым фильтрами может найти применение в устройствах фильтрации, прогнозирования процессов, дифференцирования, управления. Техническим результатом является получение гибкой архитектуры вычислений, высокое распараллеливание алгоритмов обработки сигналов и простота реализации и достигается тем, что блоки вычисления отсчетов соединены между собой и блоком ввода коэффициентов по кольцевой схеме, причем поскольку вычисления производят с разными коэффициентами, то ввод коэффициентов осуществляют посредством двух кольцевых сдвиговых регистров. Управление выбором блоков вычисления отсчетов сигналов осуществляют посредством ключей, управляемых кольцевыми сдвиговыми регистрами. 1 ил.

Устройство цифровой обработки сигналов, содержащее блоки вычисления отсчетов сигналов, отличающееся тем, что в устройство введены первый и второй буферные регистры, первую и вторую группы ключей, тактовый генератор, кольцевые сдвиговые регистры и блок ввода коэффициентов, выход первого буферного регистра соединен с первыми входами блоков вычисления отсчетов сигналов, вход является информационным входом устройства, выходы тактового генератора соединены с управляющими входами первого и второго кольцевых сдвиговых регистров, соответствующие выходы которых подключены к управляющим входам одноименных ключей соответственно первой и второй групп, выходы ключей первой группы соединены с вторыми входами одноименных блоков вычисления отсчетов сигналов, информационные выходы которых подключены к входам одноименных ключей второй группы, выходы последних соединены с входом второго буферного регистра, выход которого является выходом устройства, и подключены к входам ключей первой группы, соответствующие выходы блока ввода коэффициентов соединены с информационными входами соответственно третьего и четвертого кольцевых сдвиговых регистров, выходы которых подключены к первому и второму задающим входам первого блока вычисления отсчетов сигналов, первый и второй задающие выходы каждого предыдущего блока вычисления отсчетов сигналов подключены к одноименным задающим входам каждого последующего, первый и второй задающие выходы последнего соединены с управляющими входами соответственно третьего и четвертого кольцевых сдвиговых регистров.

| Сверхбольшие интегральные схемы и современная обработка сигналов /Под ред | |||

| С.Гуна и др | |||

| - М.: Радио и связь, 1989, с.140 - 141. |

Авторы

Даты

1998-07-10—Публикация

1996-06-10—Подача