Устройство относится к области цифровой обработки сигналов и может найти применение в устройствах цифровой фильтрации, прогнозирования различных процессов, дифференцирования, управления и в перспективных разработках и сверхбольших интегральных микросхем.

Известен цифровой фильтр к-го порядка с К параллельно работающими арифметическими устройствами, содержащий к умножителей, к сумматоров и (к+1) линий задержек с отводами [1].

Известный фильтр не обеспечивает параллельную обработку сигналов. Однако, если ввести буферные регистры в ключевые точки схемы, можно получить выходную последовательность с временной задержкой на один отсчет. Другим недостатком известного цифрового фильтра является то, что значения коэффициентов занесены в постоянную память, что нецелесообразно при изменении видов математических операций.

Наиболее близким по технической сущности к заявленному является устройство для цифровой обработки сигналов, содержащее первый буферный регистр, выход которого соединен с входами блоков вычисления отсчетов сигналов, каждый из которых состоит из элементов задержки, умножителя и сумматора [2].

Устройство работает следующим образом. Входной сигнал в каждый дискретный момент времени поступает на вход элемента задержки и умножителя первого блока вычисления отсчетов сигнала. Содержимое элементов задержки блоков вычисления отсчетов замещается следующим поступающим на вход сигналом, а предыдущее содержимое передается на элемент задержки следующего блока вычисления отсчетов по всей последовательно включенной цепи блоков вычисления отсчетов. Далее сигналы перемножаются на соответствующий коэффициент. После этого производят суммирование полученных произведений.

Данное устройство обрабатывает сигналы по формуле

где x[(n-i)] - входные отсчеты сигнала в моменты времени t = (n - i)т, i = 0, 1, 2,..., к;

y[пТ] - выходные отсчеты обработанного сигнала в момент времени t = nT;

T - период отсчета (дискретности).

Данное устройство цифровой обработки обрабатывает сигналы с задержкой на один отсчет. Однако при такой жесткой архитектуре вычислений возникает определенная сложность обработки сигнала в устройствах, когда при вычислениях выходных отсчетов требуется перестраивать коэффициенты. Например, в синтезаторе речи с линейным прогнозированием.

Техническим результатом заявленного устройства является получение гибкой архитектуры вычислений, высокого распараллеливания алгоритмов обработки сигналов и простого программно-аппаратурного исполнения.

Технический результат достигается тем, что в устройстве, содержащем первый буферный регистр, вход которого является информационным входом устройства, выход соединен с первыми входами блоков вычисления отсчетов сигналов, введены блок ввода коэффициентов, блок синхронизации и второй буферный регистр, выход которого является выходом устройства, выход блока ввода коэффициентов соединен с вторым входом первого блока вычисления отсчетов сигналов, управляющий выход каждого предыдущего блока вычисления отсчетов сигналов соединен с вторым входом каждого последующего, последний из которых соединен с управляющим входом блока ввода коэффициентов, информационные выходы блоков вычисления отсчетов сигналов подключены к входу второго буферного регистра, синхронизирующие входы соединены с соответствующими выходами блока синхронизации.

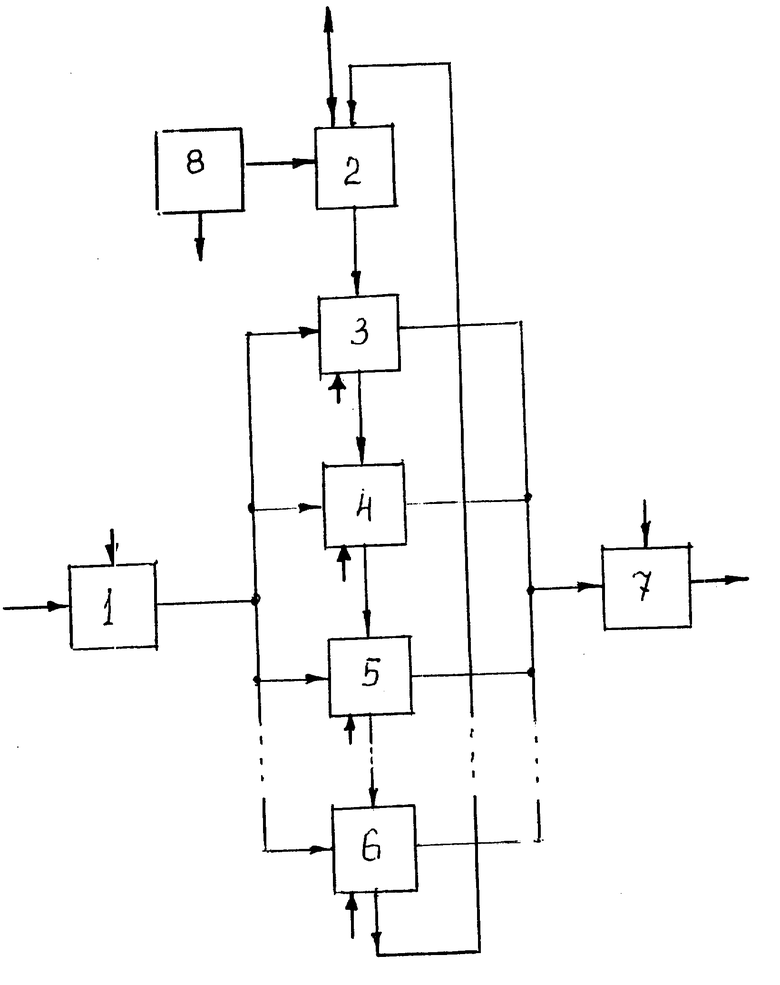

Функциональная схема устройства приведена на чертеже.

Устройство содержит первый буферный регистр 1, блок 2 ввода коэффициентов, блоки 3-6 вычисления отсчетов сигналов, второй буферный регистр 7 и блок синхронизации 8.

В представленном выполнении устройства вход первого буферного регистра 1 является информационным входом устройства, выход подключен к информационным входам всех блоков вычисления отсчетов сигналов, выход каждого предыдущего из которых подключен к задающему входу каждого последующего блока 3-6, выход последнего соединен с управляющим входом блока 2 ввода коэффициентов. Информационные выходы блоков 3-6 подключены к входу второго буферного регистра. Выходы блока синхронизации подключены к соответствующим входам всех блоков устройства. Блок 2 ввода коэффициентов имеет информационную шину для связи с внешними устройствами (на чертеже не показаны).

Устройство работает следующим образом. В устройстве организована кольцевая схема движения коэффициентов по аналогии с кольцевым регистром сдвига.

Входной сигнал в каждый дискретный момент времени поступает с регистра 1 на входы блоков 3- 5 вычисления отсчетов, которые осуществляют вычисления по формуле (1). Блоки 3-5 могут быть выполнены аналогично блокам вычисления отсчетов прототипа либо построены в соответствии с формулой многочлена уравнений, подлежащих вычислениям.

Каждый из блоков 3-5 является элементом кольцевой схемы движения коэффициентов, участвующих в вычислениях.

Блок 2 ввода коэффициентов может служить для связи устройства с внешними устройствами, например для ввода дополнительных коэффициентов при обработке сигналов в адаптивном режиме работы.

Если не требуется перестраивать коэффициенты, то блок 2 используется для начального ввода коэффициентов в структуру кольцевого регистра сдвига. Синхронизация работы устройства осуществляется посредством блока синхронизации или программными средствами. Для вычисления выходных отсчетов по формуле (1) можно на одном кристалле разместить необходимое число блоков вычисления отсчетов сигналов с двумя входами для входных отсчетов обрабатываемого сигнала и ввода значений соответствующих коэффициентов и двумя выходами для выходных отсчетов обработанного сигнала и вывода значений коэффициентов.

Предложенная конструкция позволяет обрабатывать сигналы с высокой степенью достоверности и практически в реальном масштабе времени.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ | 1996 |

|

RU2115164C1 |

| СПОСОБ КОНТРОЛЯ ТОКОРАСПРЕДЕЛЕНИЯ ПО КОМПЛЕКТАМ ЩЕТОК УЗЛА ТОКОСЪЕМА ЭЛЕКТРИЧЕСКОЙ МАШИНЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2178609C2 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Хаару | 1982 |

|

SU1061150A1 |

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

| Устройство для ортогонального преобразования цифровых сигналов по функциям Хаара | 1983 |

|

SU1116435A1 |

| Устройство для выполнения обратного преобразования Хаара | 1983 |

|

SU1104528A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ ТАБЛИЧНО-АЛГОРИТМИЧЕСКИМ МЕТОДОМ | 1996 |

|

RU2136041C1 |

| Устройство автоматического получения и обработки изображений | 2019 |

|

RU2707714C1 |

| УСТРОЙСТВО ДЛЯ ЭЛЕКТРОХИРУРГИЧЕСКИХ ИЗМЕРЕНИЙ | 1998 |

|

RU2139000C1 |

Изобретение относится к области цифровой обработки сигналов и может найти применение в устройствах цифровой фильтрации, в перспективных разработках больших и сверхбольших интегральных микросхем. Технический результат - получение гибкой архитектуры вычислений высокого распараллеливания алгоритмов обработки сигналов и простота программного обеспечения. Устройство содержит первый буферный регистр 1, блок 2 ввода коэффициентов, блоки 3-6 вычисления отсчетов сигналов, второй буферный регистр 7, блок синхронизации 8. 1 ил.

Устройство для цифровой обработки сигналов, содержащее первый буферный регистр, вход которого является информационным входом устройства, выход соединен с первыми входами блоков вычисления отсчетов сигналов, отличающееся тем, что в устройство введены блок ввода коэффициентов, блок синхронизации и второй буферный регистр, выход которого является выходом устройства, выход блока ввода коэффициентов соединены с вторым входом первого блока вычисления отсчетов сигналов, управляющий выход каждого предыдущего блока вычисления отсчетов сигналов соединен с вторым входом каждого последующего, последний из которых соединен с управляющим входом блока ввода коэффициентов, информационные выходы блоков вычисления отсчетов сигналов подключены к входу второго буферного регистра, синхронизирующие входы соединены с соответствующими выходами блока синхронизации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Рабинер А.Л., Гоулд Ю | |||

| Теория и применение цифровой обработки сигналов | |||

| - М.: Мир, 1979, с | |||

| ШПАЛОРЕЗНЫЙ СТАНОК | 1922 |

|

SU607A1 |

| Прибор, замыкающий сигнальную цепь при повышении температуры | 1918 |

|

SU99A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Сверхбольшие интегральные схемы и современная обработка сигналов | |||

| / Под ред | |||

| С.Гуна, Х.Уайтхауса | |||

| - М.: Радио и связь, 1989, с | |||

| ПАРОПЕРЕГРЕВАТЕЛЬ ДЛЯ ЛОКОМОБИЛЬНЫХ КОТЛОВ | 1912 |

|

SU277A1 |

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

Авторы

Даты

1998-02-20—Публикация

1996-06-10—Подача