Изобретение относится к технике связи и может использоваться при разработке аппаратуры передачи цифровой информации, представленной двухинтервальными БИ, ЧМ и ФМ канальными кодами.

Известны приемники двухинтервальных канальных кодов, сформированных с использованием только двух временных интервалов τ0 и τ0/2, где τ0 - длительность единичного сигнала данных, равная тактовому интервалу. Наиболее широко используемыми являются фазоманипулированный (ФМ) или манчестерский код (ГОСТ 26.765.52-87), биимпульсный (БИ) код (ГОСТ 27232-87) и частотноманипулированный (ЧМ) код.

К таким устройствам относится, например, "Декодер" [1], осуществляющий формирование тактовой частоты приема и декодирование информации, представленной двухинтервальными канальными кодами. Недостатками устройства являются прекращение формирования тактовой частоты при замираниях сигнала в линиях связи и, как следствие, сбой цикловой синхронизации аппаратуры передачи данных, а также работа только на одной скорости.

Указанных недостатков лишено "Устройство синхронизации и декодирования" [2], обеспечивающее автоподстройку и формирование тактовой частоты приема (в том числе при замираниях сигналов в линии связи), а также декодирование сигналов двухинтервальных канальных кодов. Недостаток устройства заключается в обязательном участии обслуживающего персонала для изменения скорости обмена данными. Это требует значительных затрат времени на формирование, передачу и прием соответствующего сообщения, что снижает производительность линии связи.

Наиболее близким к предлагаемому техническому решению является "Приемник цифровой информации" [3] , выбранный за прототип, в котором осуществляется автоматическая выработка кода скорости работы устройства.

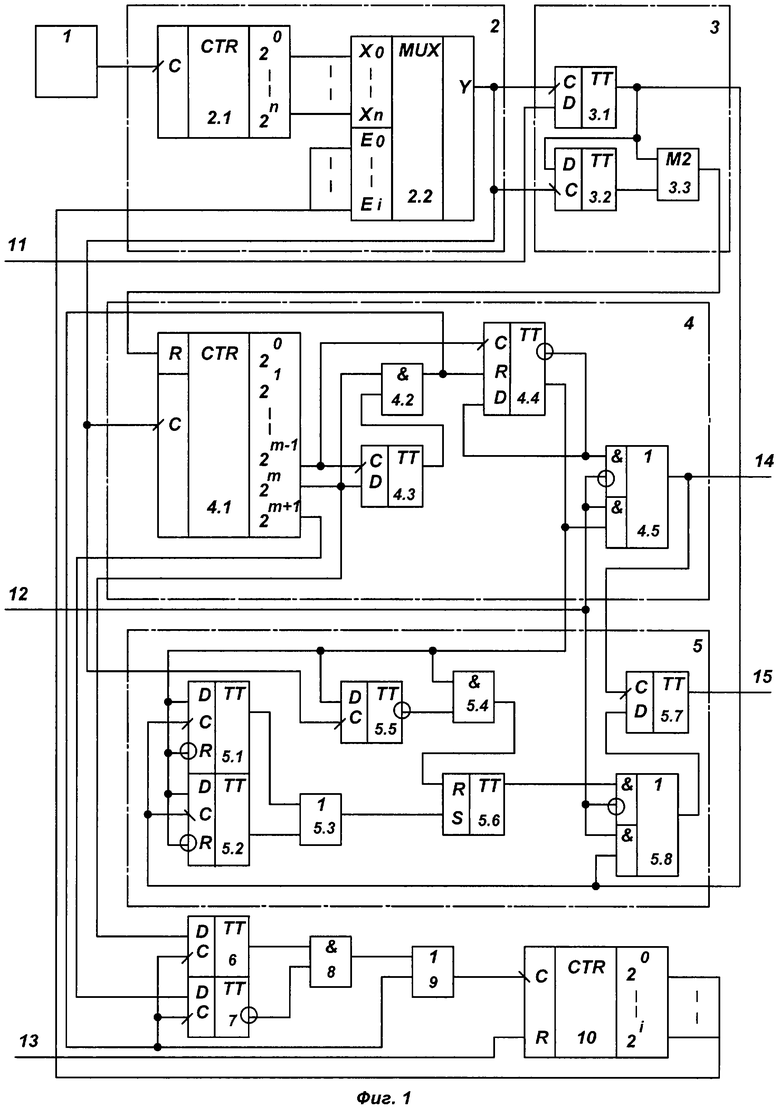

На фиг.1 представлена функциональная схема устройства-прототипа. Устройство содержит задающий генератор 1, формирователь опорной частоты 2, анализатор сигналов 3, формирователь тактовой частоты 4, декодер 5, первый 6 и второй 7 D-триггеры, элемент И 8, элемент ИЛИ 9 и двоичный счетчик 10, а также информационный 11, управляющий 12 и установочный 13 входы, тактовой 14 и информационный 15 выходы.

Устройство имеет следующие связи. Выход задающего генератора 1 через формирователь опорной частоты 2 подключен к первым входам анализатора сигналов 3 формирователя тактовой частоты 4 и декодера 5. Выход декодера 5 соединен с информационным 15 выходом устройства, информационный вход 11 которого подключен ко второму входу анализатора сигналов 3. Первый выход последнего соединен со вторым входом декодера 5, а второй - со вторым входом формирователя тактовой частоты 4, первый выход которого подключен к тактовому выходу 14 устройства и к третьему входу декодера 5, второй - к четвертому входу декодера, третий и четвертый - к информационным входам соответственно первого 6 и второго 7 D-триггеров, пятый - к тактовым входам первого 6 и второго 7 D-триггеров и к первому входу элемента ИЛИ 9. Прямой выход первого 6 D-триггера и инверсный выход второго 7 D-триггера соединены со входами элемента И 8, выход которого подключен ко второму входу элемента ИЛИ 9, соединенного выходом со счетным входом двоичного счетчика 10, вход установки в "0" которого подключен к установочному входу 13 устройства, а выход - ко второму входу формирователя опорной частоты 2. Управляющий 12 вход устройства подключен к объединенным третьему входу формирователя тактовой частоты 4 и пятому входу декодера 5.

Известное устройство работает следующим образом. На информационный вход 11 устройства поступают данные, кодированные одним из трех двухинтервальных канальных кодов (БИ, ЧМ, ФМ). На управляющий вход 12 устройства подается лог. "0", если поступающие из линии связи данные кодированы БИ и ЧМ двухинтервальными кодами и лог. "1", если данные кодированы ФМ двухинтервальным кодом.

Анализатором сигналов 3 производится выделение фронтов и спадов сигналов кодированной последовательности, поступающей на информационный вход 11 устройства. Каждым из этих импульсов приводится в исходное состояние счетчик 4.1 формирователя тактовой частоты 4. Счетчик выполняет функцию интегратора, который совместно со схемой выделения импульса коррекции (элементы 4.2 и 4.3) производит подстройку фазы делителя на 2, выполненного на D-триггере 4.4, который формирует тактовую частоту приема. При кодировании данных БИ-кодом импульсы коррекции вырабатываются при каждом переходе исходного сигнала из "1" в "0", при кодировании ЧМ-кодом - при каждом "0" в исходном сигнале, при кодировании ФМ-кодом - при каждом переходе исходного сигнала из "1" в "0" и из "0" в "1". Импульсы коррекции обеспечивают подтверждение или восстановление синфазности. Откорректированная частота подается на декодер 5. Последний содержит схему выделения "единиц" исходной последовательности из кодированных сигналов, выполненную на элементах 5.1-5.6, а также переключатель 5.8 и D-триггер 5.7. При декодировании БИ и ЧМ-кодов на выход переключателя 5.8 под действием сигнала управления поступают сигналы с выхода элемента 5.6 схемы выделения "единиц". Одновременно через переключатель 4.5 на тактовый вход D-триггера 5.7 выдается частота с инверсного выхода D-триггера 4.4, что обеспечивает наличие на тактовом 14 и информационном 15 выходах устройства тактовой частоты приема и синфазных с ней декодированных данных. Изложенное подробно поясняется временными диаграммами, приведенными на фиг. 2, 3 и 4 в [2].

Подстройка к требуемой скорости происходит следующим образом. На установочный 13 вход устройства подается сигнал, устанавливающий двоичный счетчик 10 в состояние "0", что соответствует подключению на выход мультиплексора 2.2 максимальной по величине опорной частоты, вследствие чего счетчик 4.1 формирователя тактовой частоты 4 переполняется и в его дополнительном разряде (2m+1) появляются "1". При появлении на выходе элемента 4.2 очередного импульса коррекции состояния старшего (2m+1) и дополнительного (2m+1) разрядов счетчика 4.1 фиксируются D-триггерами 6 и 7, при этом состояние "1" на прямых выходах этих триггеров свидетельствует о необходимости понижения значения опорной частоты и на выходе элемента И 8 появляется лог. "0", разрешающий прохождение импульсов коррекции на счетный вход двоичного счетчика 10. По каждому импульсу счетчик получает приращение формируемого им кода на единицу. Процесс продолжается до тех пор, пока D-триггеры 6 и 7 не зафиксируют состояние "1" и "0" соответственно, что сопровождается формированием на выходе элемента И 8 лог. "1", блокирующей прохождение через элемент ИЛИ 9 импульсов коррекции на счетный вход двоичного счетчика 10. В результате значение опорной частоты в дальнейшем не изменяется, что свидетельствует о завершении процесса адаптации устройства к скорости сигналов, поступающих из линии связи.

Из описания работы устройства-прототипа следует, что оно обеспечивает автоматическую подстройку скорости сигналов, поступающих из линии связи в том случае, если она ниже скорости работы приемника. В противном случае необходимо формирование внешнего сигнала установки, подаваемого на установочный 13 вход устройства. Это возможно либо вручную оператором, либо, например, путем подсчета ошибок в принимаемом сигнале на заданном интервале и т. д., что требует затрат времени и снижает производительность линии связи.

Задачей предлагаемого устройства является повышение производительности линии связи.

Технический результат, достигаемый устройством, заключается в автоматическом определении знака рассогласования скоростей передающей и приемной сторон и приведения их в соответствие путем выработки опорной частоты, обеспечивающей получение тактовой частоты приема, соответствующей значению скорости поступающей информации.

Признаками предлагаемого устройства, общими с прототипом, являются задающий генератор, формирователь опорной частоты, анализатор сигналов, формирователь тактовой частоты, декодер, двоичный счетчик, первый и второй D-триггеры, первый элемент И, первый элемент ИЛИ, информационный и управляющие входы, тактовый и информационный выходы. При этом выход задающего генератора через формирователь опорной частоты подключен к первым входам анализатора сигналов, формирователя тактовой частоты и декодера, выход которого соединен с информационным выходом устройства, информационный вход которого подключен ко второму входу анализатора сигналов, первый выход которого соединен со вторым входом декодера, а второй - со вторым входом формирователя тактовой частоты, первый выход которого подключен к тактовому выходу устройства и к третьему входу декодера, второй - к четвертому входу декодера, третий и четвертый - к информационным входам соответственно первого и второго D-триггеров, пятый - к тактовым входам первого и второго D-триггеров, выход первого элемента ИЛИ соединен со счетным входом двоичного счетчика, а третий вход формирователя тактовой частоты объединен с пятым входом декодера и подключен к управляющему входу устройства.

Признаками предлагаемого устройства, отличными от признаков устройства-прототипа, являются реверсивный счетчик, регистр сдвига, третий, четвертый, пятый и шестой D-триггеры, второй и третий элементы И, второй элемент ИЛИ, элемент ИЛИ - НЕ, элемент И - НЕ.

При этом выход задающего генератора подключен к тактовым входам четвертого, пятого и шестого D-триггеров, выход формирователя опорной частоты - к первому входу первого элемента ИЛИ, второй выход анализатора сигналов - к первому входу первого элемента И и к тактовому входу регистра сдвига, пятый выход формирователя тактовой частоты - к информационному входу пятого D-триггера, выход которого через последовательно соединенные третий элемент И и второй элемент ИЛИ подключен к счетному входу реверсивного счетчика, выход которого соединен со вторым входом формирователя опорной частоты.

Прямой выход первого D-триггера и инверсный выход второго D-триггера через элемент И - НЕ подключены ко второму входу третьего элемента И, выход первого элемента И - к первому входу элемента ИЛИ - НЕ и к информационному входу четвертого D-триггера, инверсный выход которого соединен со вторым входом элемента ИЛИ - НЕ, выход которого подключен ко входам установки в "0" третьего D-триггера и двоичного счетчика. Младший из трех последних разрядов двоичного счетчика подключен к тактовому входу, а предпоследний и последний через второй элемент И - к информационному входу третьего D-триггера, инверсный выход которого соединен с информационным входом регистра сдвига, а прямой - со вторыми входами первого элемента ИЛИ и первого элемента И и входом установки в "0" регистра сдвига, выход которого подключен к управляющему входу реверсивного счетчика и к информационному входу шестого D-триггера, выходом соединенного со вторым входом второго элемента ИЛИ.

Сущность предлагаемого технического решения заключается в подсчете знакоперемен на заданном интервале. При согласованных скоростях передачи и приема их должно быть не более одной, а при превышении скорости передачи над скоростью приема - не менее двух. В этом случае устройство формирует сигнал управления реверсивным счетчиком, соответствующий режиму вычитания и его фронтом, поступающим на счетный вход реверсивного счетчика, формируется новый код скорости, обеспечивающий повышение номинала опорной частоты, а следовательно, и тактовой частоты приема.

На фиг.1 приведена функциональная схема устройства-прототипа.

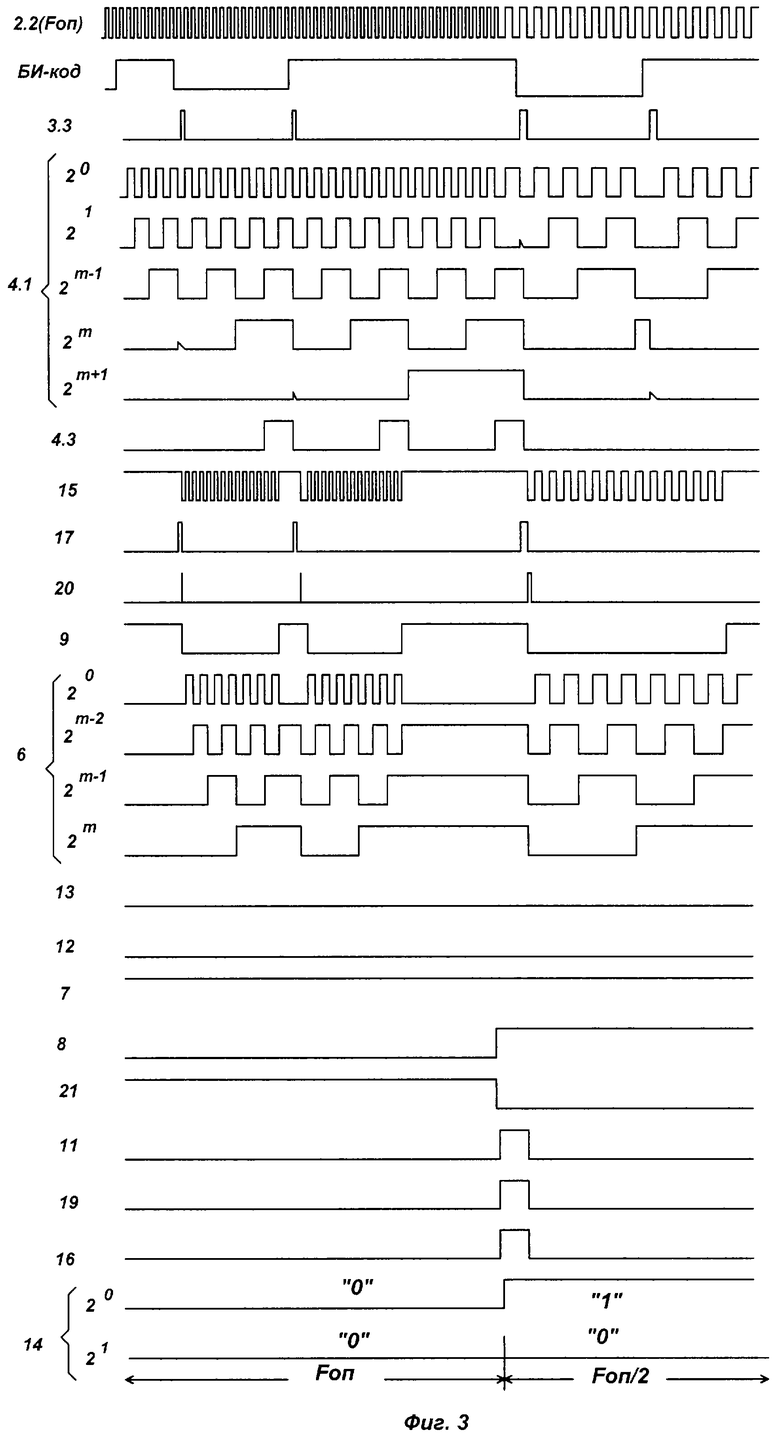

На фиг.2 представлена функциональная схема предлагаемого устройства.

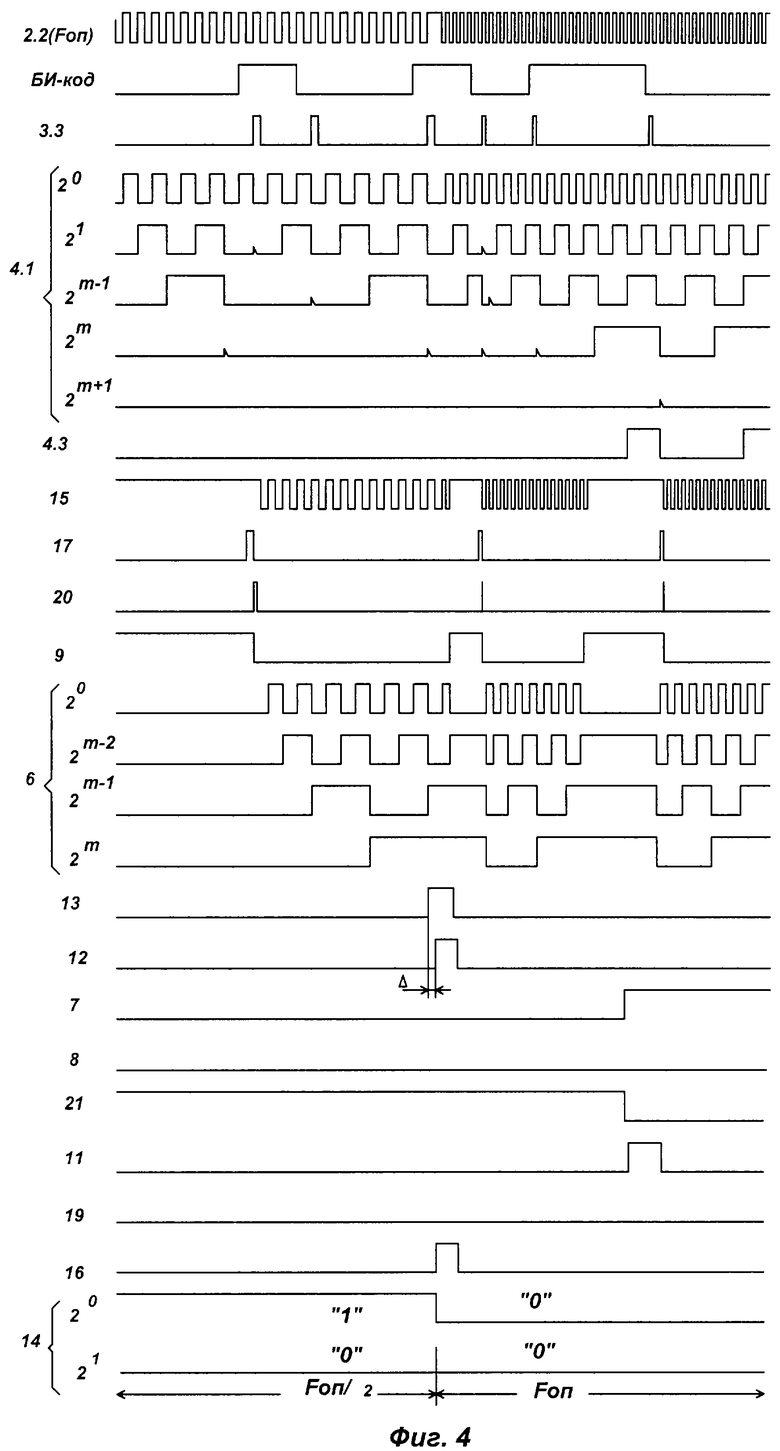

На фиг. 3 изображены временные диаграммы, поясняющие работу устройства при повышении скорости приема над скоростью передачи.

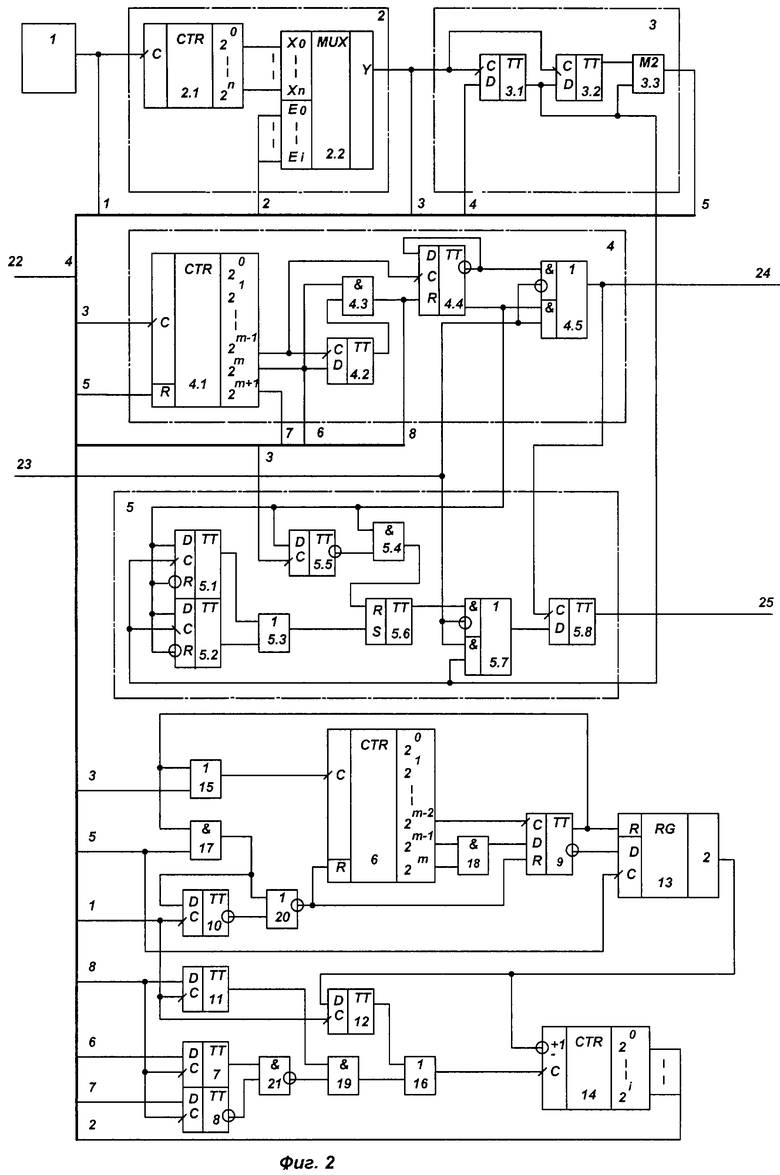

На фиг.4 приведены временные диаграммы, поясняющие работу устройства при превышении скорости передачи над скоростью приема.

Предлагаемое устройство (фиг.2) содержит задающий генератор 1, формирователь опорной частоты 2, анализатор сигналов 3, формирователь тактовой частоты 4, декодер 5, двоичный счетчик 6, первый 7, второй 8, третий 9, четвертый 10, пятый 11 и шестой 12 D-триггеры, регистр сдвига 13, реверсивный счетчик 14, первый 15 и второй 16 элементы ИЛИ, первый 17, второй 18 и третий 19 элементы И, элемент ИЛИ - НЕ 20, элемент И - НЕ 21, информационный 22 и управляющий 23 входы, тактовый 24 и информационный 25 выходы.

Устройство имеет следующие связи. Выход задающего генератора 1 через формирователь опорной частоты 2 подключен к первым входам анализатора сигналов 3, формирователя тактовой частоты 4 и декодера 5. Выход декодера 5 соединен с информационным 25 выходом устройства, информационный вход 22 которого подключен ко второму входу анализатора сигналов 3. Первый выход последнего соединен со вторым входом декодера 5, а второй - со вторым входом формирователя тактовой частоты 4. Первый выход формирователя тактовой частоты 4 подключен к тактовому 24 выходу устройства и к третьему входу декодера 5, второй - к четвертому входу декодера 5, третий и четвертый - к информационным входам соответственно первого 7 и второго 8 D-триггеров, пятый - к тактовым входам первого 7 и второго 8 D-триггеров. Выход задающего генератора 1 дополнительно подключен к тактовым входам четвертого 4, пятого 5 и шестого 6 D-триггеров, выход формирователя опорной частоты 2 через первый 15 элемент ИЛИ - к счетному входу двоичного счетчика 6, второй выход анализатора сигналов 3 - к первому входу первого 17 элемента И и к тактовому входу регистра сдвига 13, пятый выход формирователя тактовой частоты 4 - к информационному входу пятого 11 D-триггера, выход которого через последовательно соединенные третий 19 элемент И и второй 16 элемент ИЛИ подключен к счетному входу реверсивного счетчика 14. Выход реверсивного счетчика 14 соединен со вторым входом формирователя опорной частоты 2. Прямой выход первого 7 и инверсный выход второго 8 D-триггеров через элемент И - НЕ 21 подключены ко второму входу третьего 19 элемента И, выход первого 17 элемента И - к первому входу элемента ИЛИ - НЕ 20 и к информационному входу четвертого 10 D-триггера, инверсный выход которого соединен со вторым входом элемента ИЛИ - НЕ 20, выход которого подключен ко входам установки в "0" третьего 9 D-триггера и двоичного счетчика 6. Младший из трех последних разрядов двоичного счетчика 6 подключен к тактовому входу, а предпоследний и последний через второй 18 элемент И - к информационному входу третьего 9 D-триггера, инверсный выход которого соединен с информационным входом регистра сдвига 13, а прямой - со вторыми входами первого 15 элемента ИЛИ, первого 17 элемента И и входом установки в "0" регистра сдвига 13, выход которого подключен к управляющему входу реверсивного счетчика 14 и к информационному входу шестого 12 D-триггера, выходом соединенного со вторым входом второго 16 элемента ИЛИ. Третий вход формирователя тактовой частоты 4 объединен с пятым входом декодера 5 и подключен к управляющему 23 входу устройства.

Предлагаемое устройство осуществляет анализ поступающих сигналов, автоподстройку тактовой частоты и декодирование информации аналогично устройству-прототипу. Автоматическое согласование скоростей при превышении скорости приема над скоростью передачи и при превышении скорости передачи над скоростью приема происходит следующим образом.

При включении электропитания элементы памяти устройства могут находиться в произвольном состоянии, при этом третий 9 D-триггер, если он находится в состоянии "0" по прямому выходу, по истечении переходного периода установится в состояние "1" сигналом с выхода второго 18 элемента И, выделяемого при работе двоичного счетчика 6, на счетный вход которого через первый 15 элемент ИЛИ поступают импульсы опорной частоты Fоп с выхода мультиплексора 2.2. Сигналом лог. "1", поступающим с прямого выхода третьего 9 D-триггера на вход установки в "0" регистра сдвига 13, реверсивный счетчик 14 по входу управления (±1) устанавливается в режим суммирования.

На выходе узла формирования опорной частоты 2 значение опорной частоты может быть равным, а также большим или меньшим требуемой величины.

При установке опорной частоты приема, соответствующей согласованной работе передающей стороны с приемной, в момент появления переднего фронта очередного импульса коррекции с выхода элемента И 4.3 на прямых выходах первого 7 и второго 8 D-триггеров устанавливается комбинация "10", в результате чего на выходе элемента И - НЕ 21 имеет место лог. "0", блокирующий прохождение импульса коррекции через третий 19 элемент И и второй 16 элемент ИЛИ на счетный вход реверсивного счетчика 14. Благодаря этому состояние реверсивного счетчика не изменяется и, следовательно, не изменяется код скорости, определяющий номинал опорной частоты.

Если значение опорной частоты приема выше требуемой (фиг.3), то в момент появления очередного импульса коррекции с выхода элемента 4.3 последний (2m) и дополнительный (2m+1) разряды двоичного счетчика 4.1 устанавливаются в "1". По переднему фронту импульса коррекции первый 7 и второй 8 D-триггеры устанавливаются в состояние "1" и на выходе элемента И - НЕ 21 появляется лог. "1", разрешающая прохождение импульса коррекции через третий 19 элемент И и второй 16 элемент ИЛИ на счетный вход реверсивного счетчика 14, находящегося, как об этом говорилось выше, по входу управления в режиме суммирования. В результате состояние реверсивного счетчика увеличивается на единицу, что обеспечивает понижение опорной частоты. Процесс продолжается до получения требуемого значения опорной частоты.

Если опорная частота приема ниже требуемой (фиг.4), то согласование осуществляется с помощью элементов 6, 9, 10, 12, 13, 15, 17, 18 и 20 следующим образом. С помощью двоичного счетчика 6 и второго 18 элемента И на выходе третьего 9 D-триггера формируется временной интервал, величина которого, выраженная в периодах опорной частоты, определяется как

N=7•2m-3,

где m≥3 - число разрядов двоичного счетчика 6.

Формирование интервала (N) начинается с момента поступления на вход первого 17 элемента И импульса с выхода элемента 3.3, появляющегося при каждой знакоперемене (при переходе из "1" в "0" или из "0" в "1") во входной последовательности на информационном входе 22 устройства. С помощью схемы, выполненной на четвертом 10 D-триггере и элементе ИЛИ - НЕ 20, формируется короткий импульс, устанавливающий в "0" двоичный счетчик 6 и третий 9 D-триггер. В результате этого регистр сдвига 13 получает возможность продвижения "1", поступающей с инверсного выхода третьего 9 D-триггера импульсами знакоперемен с выхода элемента 3.3. В рассматриваемом случае, когда опорная частота приема ниже требуемой, на тактовый вход регистра сдвига 13 в течение времени формирования интервала поступает не менее двух импульсов и на выходе регистра сдвига 13 появляется "I", которая переводит реверсивный счетчик 14 по входу управления (±1) в режим вычитания, а через небольшую задержку, создаваемую шестым 12 D-триггером, поступает через второй 16 элемент ИЛИ на счетный вход реверсивного счетчика 14, переводя его в предыдущее состояние, соответствующее более высокому значению опорной частоты. Процесс продолжается до появления на выходе реверсивного счетчика 14 требуемого кода скорости, а на выходе формирователя опорной частоты 2 требуемого значения опорной частоты.

Таким образом, предлагаемое техническое решение обеспечивает автоматическое согласование скоростей передающей и приемной сторон без внешних сигналов управления (исключая управление выбором разновидности используемого двухинтервального канального кода), что повышает производительность линии связи.

Источники литературы

1. Князькин B. C. , Пресняков Ю.В., Трошанов В.А. Декодер. Патент RU 2088044, М. Кл. Н 03 М 5/22.

2. Горюнов В.А., Колесников А.В., Котов В.И., Трошанов В.А. Устройство синхронизации и декодирования. Свидетельство на полезную модель 16809, М. Кл. Н 03 М 5/22.

3. Горюнов В.А., Колесников А.В., Котов В.И., Овчинкин Г.М., Трошанов В. А. Приемник цифровой информации. Заявка на полезную модель 2000131122 от 13.12.2000 г., М. Кл. Н 03 М 5/22.

Положительное решение ФИПС от 12.03.2001 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИЕМНИК ДИСКРЕТНОЙ ИНФОРМАЦИИ С АВТОМАТИЧЕСКИМ СОГЛАСОВАНИЕМ СКОРОСТЕЙ ПЕРЕДАЧИ И ПРИЕМА | 2003 |

|

RU2249919C2 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИЕМОПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2209524C2 |

| ДЕКОДЕР | 1993 |

|

RU2088044C1 |

| УСТРОЙСТВО ВВОДА И ХРАНЕНИЯ КЛЮЧЕВОЙ ИНФОРМАЦИИ | 2000 |

|

RU2175775C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

Изобретение относится к технике связи и может использоваться при разработке аппаратуры передачи цифровой информации, представленной двухинтервальными БИ, ЧМ и ФМ канальными кодами. Технический результат - автоматическое определение знака рассогласования скоростей передающей и приемной сторон и приведение их в соответствие путем выработки опорной частоты, обеспечивающей получение тактовой частоты приема, соответствующей значению скорости поступающей информации. Устройство содержит задающий генератор, формирователь опорной частоты, анализатор сигналов, формирователь тактовой частоты, декодер и формирователь кода скорости. Из поступающих на информационный вход устройства сигналов, представленных двухинтервальными канальными кодами, выделяются фронты и спады, используемые в качестве временных меток при формировании тактовой частоты приема и знака рассогласования скоростей передающей и приемной сторон, после чего вырабатываются импульсы, под воздействием которых изменяется номинал опорной частоты, обеспечивающей в конечном итоге получение тактовой частоты приема, соответствующей скорости сигналов, поступающих на информационный вход устройства. 4 ил.

Устройство приема дискретной информации, содержащее задающий генератор, формирователь опорной частоты, анализатор сигналов, формирователь тактовой частоты, декодер, двоичный счетчик, первый и второй D-триггеры, первый элемент И, первый элемент ИЛИ, информационный и управляющий входы, тактовый и информационный выходы, при этом выход задающего генератора через формирователь опорной частоты подключен к первым входам анализатора сигналов, формирователя тактовой частоты и декодера, выход которого соединен с информационным выходом устройства, информационный вход которого подключен ко второму входу анализатора сигналов, первый выход которого соединен со вторым входом декодера, а второй - со вторым входом формирователя тактовой частоты, первый выход которого подключен к тактовому выходу устройства и к третьему входу декодера, а второй - к четвертому входу декодера, третий и четвертый - к информационным входам соответственно первого и второго D-триггеров, пятый - к тактовым входам первого и второго D-триггеров, выход первого элемента ИЛИ соединен со счетным входом двоичного счетчика, а третий вход формирователя тактовой частоты объединен с пятым входом декодера и подключен к управляющему входу устройства, отличающееся тем, что в него введены реверсивный счетчик, регистр сдвига, третий, четвертый, пятый и шестой D-триггеры, второй и третий элементы И, второй элемент ИЛИ, элемент ИЛИ-НЕ и элемент И-НЕ, при этом выход задающего генератора подключен к тактовым входам четвертого, пятого и шестого D-триггеров, выход формирователя опорной частоты - к первому входу первого элемента ИЛИ, второй выход анализатора сигналов - к первому входу первого элемента И и к тактовому входу регистра сдвига, пятый выход формирователя тактовой частоты - к информационному входу пятого D-тригера, выход которого через последовательно соединенные третий элемент И и второй элемент ИЛИ подключен к счетному входу реверсивного счетчика, выход которого соединен со вторым входом формирователя опорной частоты, прямой выход первого D-триггера и инверсный выход второго D-триггера через элемент И - НЕ подключены ко второму входу третьего элемента И, выход первого элемента И подключен к первому входу элемента ИЛИ - НЕ и к информационному входу четвертого D-триггера, инверсный выход которого соединен с вторым входом элемента ИЛИ-НЕ, выход которого подключен ко входам установки в "0" третьего D-триггера и двоичного счетчика, младший из трех последних разрядов которого подключен к тактовому входу, а предпоследний и последний через второй элемент И - к информационному входу третьего D-триггера, инверсный выход которого соединен с информационным входом регистра сдвига, а прямой - со вторыми входами первого элемента ИЛИ, первого элемента И и входом установки в "0" регистра сдвига, выход которого подключен к управляющему входу реверсивного счетчика и к информационному входу шестого D-триггера, выходом соединенного со вторым входом второго элемента ИЛИ.

| Ветряный винтовой двигатель с трубчатым поворотным кожухом | 1927 |

|

SU18331A1 |

| Конденсационная установка к углевыжигательным печам | 1927 |

|

SU16809A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2022479C1 |

| ДЕКОДЕР | 1993 |

|

RU2088044C1 |

| Преобразователь биимпульсного двоичного сигнала в бинарный сигнал | 1983 |

|

SU1200426A1 |

| Декодер | 1984 |

|

SU1236615A1 |

Авторы

Даты

2003-06-20—Публикация

2001-06-13—Подача