us.1

Изобретение относится к вычислительной технике и технике связи и может быть использовано в скоростных системах передачи цифровой информации. .

Цель изобретения - повышение достоверности передаваемой информации и скорости ее передачи.

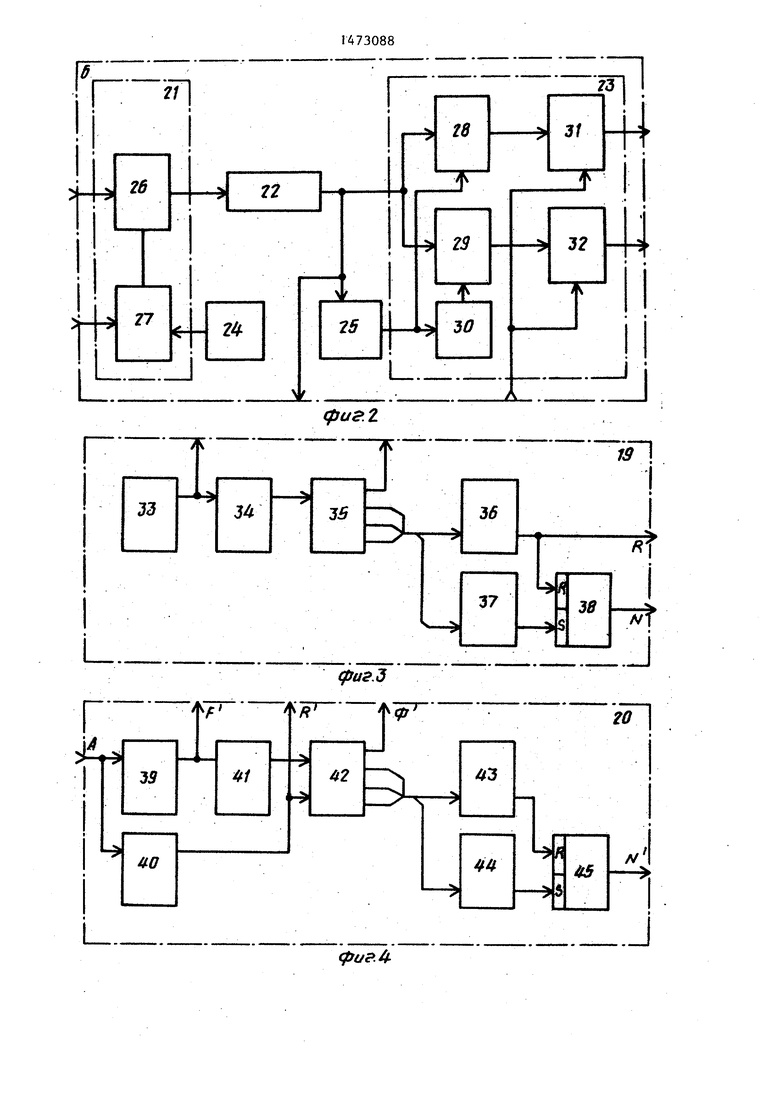

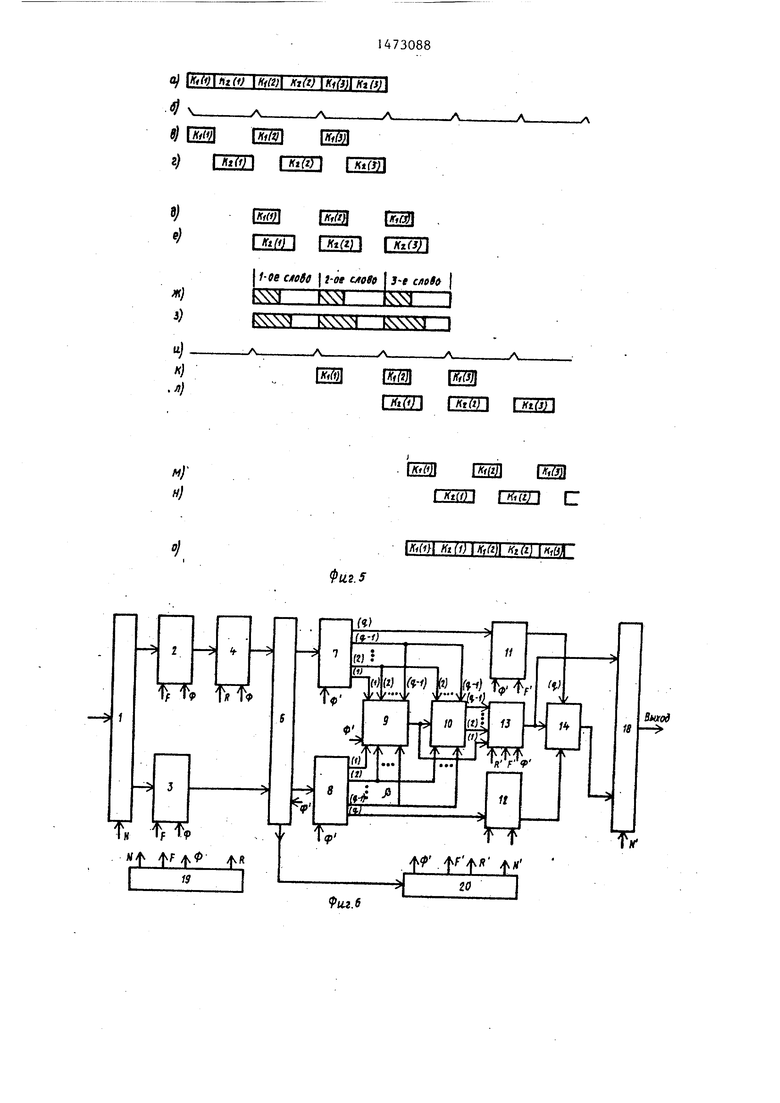

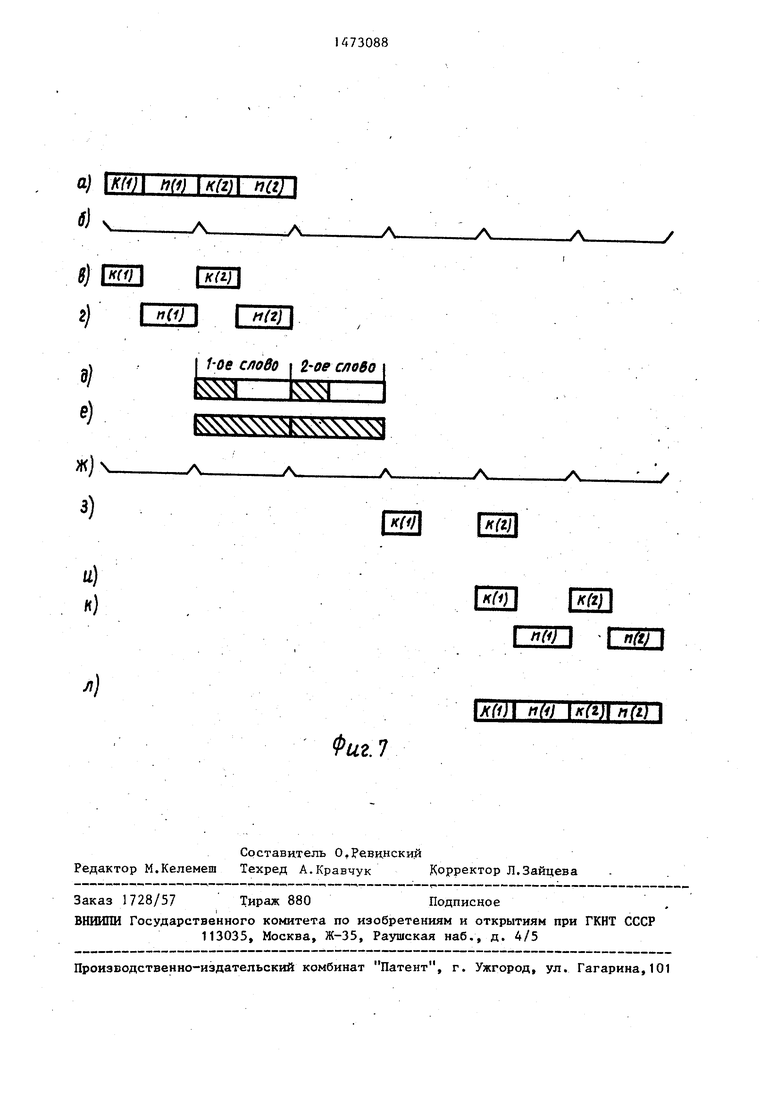

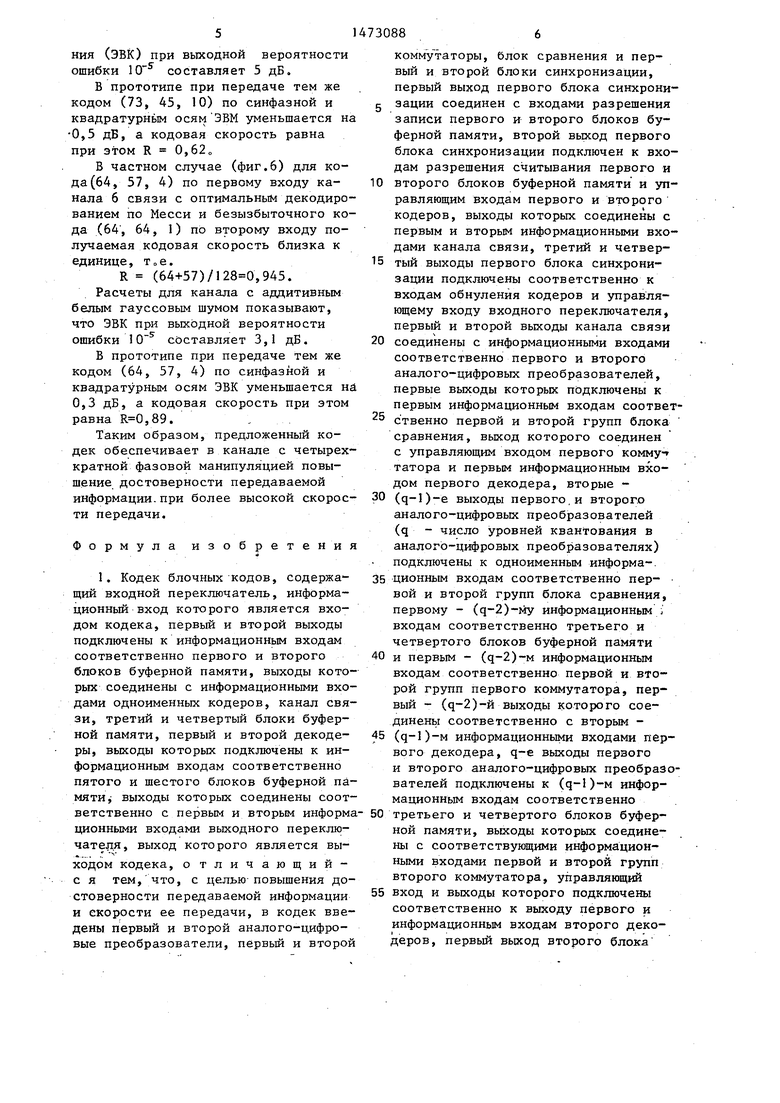

На фиго приведена блок-схема ко- дека; на фиг.2 - 4 - примеры реализации соответственно канала связи и первого и второго блоков синхронизации; на фиг.5 - временная структура сигналов; на фиг.6 - пример ко- дека для частного случая; на фиг.7 - временная структура сигналов кодека согласно фиг.6.

Кодек блочных кодов содержит (фиг.1) входной переключатель 1, пер вый и второй блоки 2, 3 буферной памяти, первый и второй кодеры 4, 5, канал 6 связи, первый и второй аналого-цифровые преобразователи (АЦП) 7, 8, блок 9 сравнения, первый комму- татор 10, третий и четвертый блоки 11, 12 буферной памяти, первый декодер 13, второй коммутатор 14, второй декодер 15, пятый и шестой блоки 16, 17 буферной памяти, выходной переклю чатель 18, первый и второй блоки 19, 20 синхронизации.

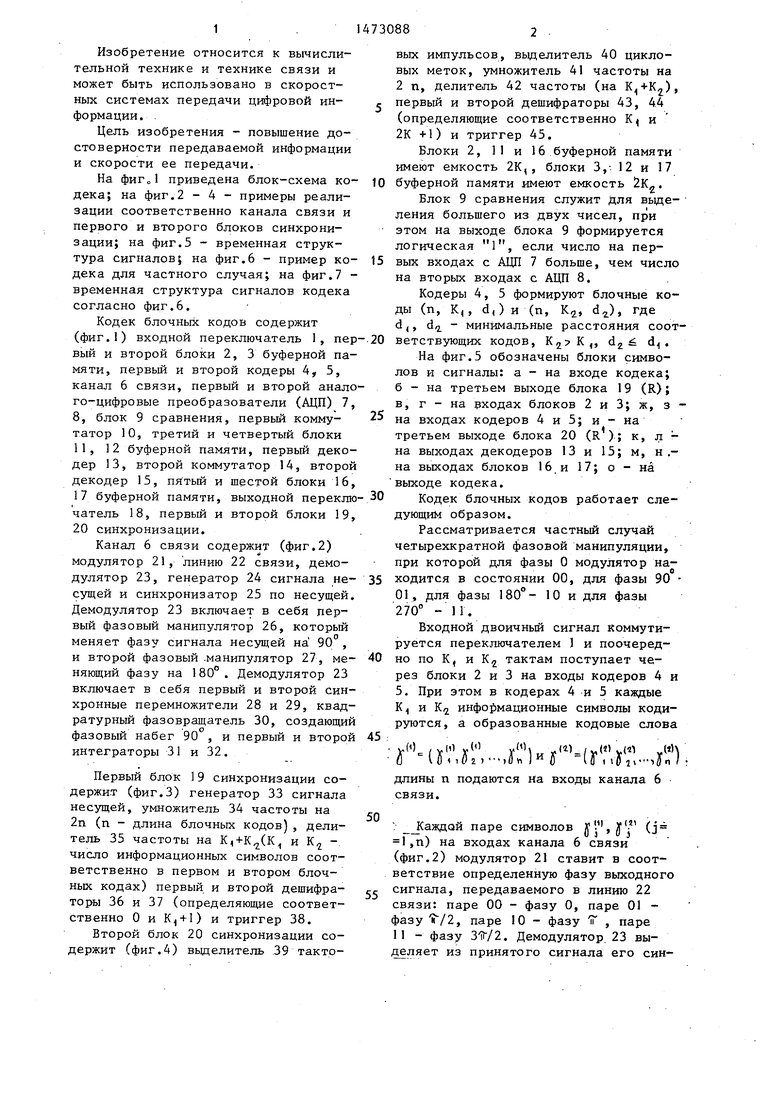

Канал 6 связи содержит (фиг.2) модулятор 21, линию 22 связи, демодулятор 23, генератор 24 сигнала не- сущей и синхронизатор 25 по несущей. Демодулятор 23 включает в себя первый фазовый манипулятор 26, который

дО

меняет фазу сигнала несущей на 90 и второй фазовый .манипулятор 27, меняющий фазу на 180°. Демодулятор 23 включает в себя первый и второй синхронные перемножители 28 и 29, квадратурный фазовращатель 30, создающий фазовый набег 90°, и первый и второй интеграторы 31 и 32.

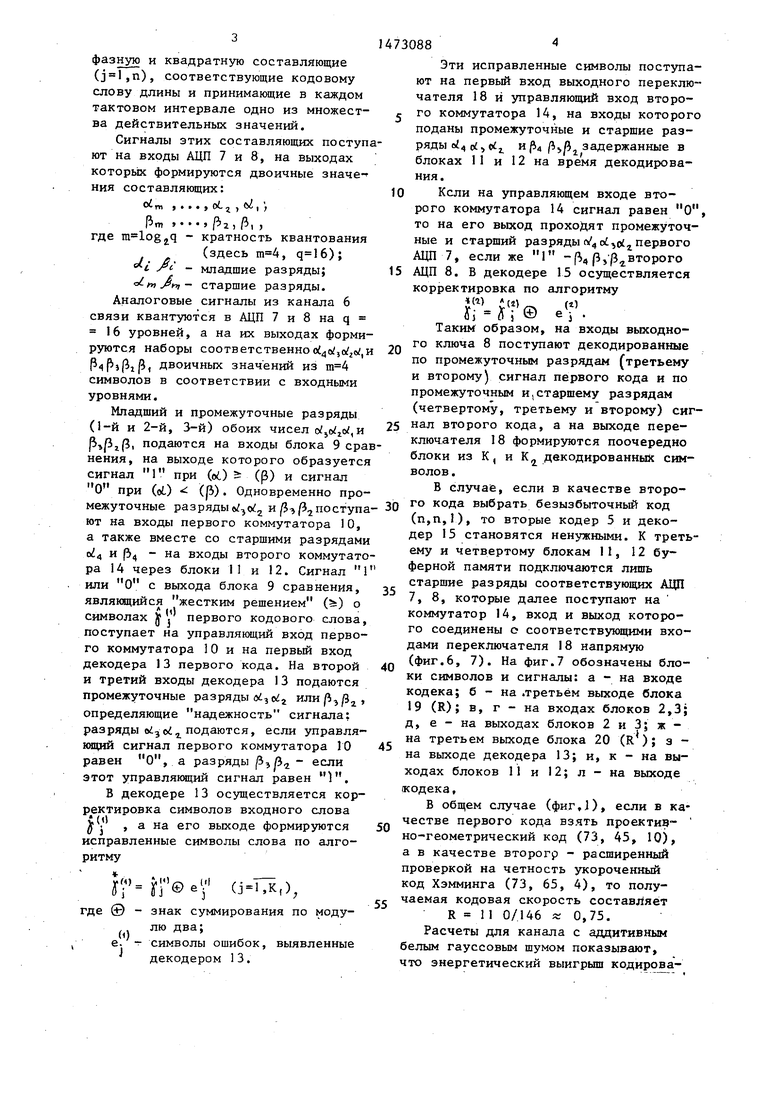

Первый блок 19 синхронизации содержит (фиг.З) генератор 33 сигнала несущей, умножитель 34 частоты на 2п (п - длина блочных кодов), делитель 35 частоты на К,+К(К и К - число информационных символов соответственно в первом и втором блочных кодах) первый и второй дешифраторы 36 и 37 (определяющие соответственно О и К., + 1) и триггер 38.

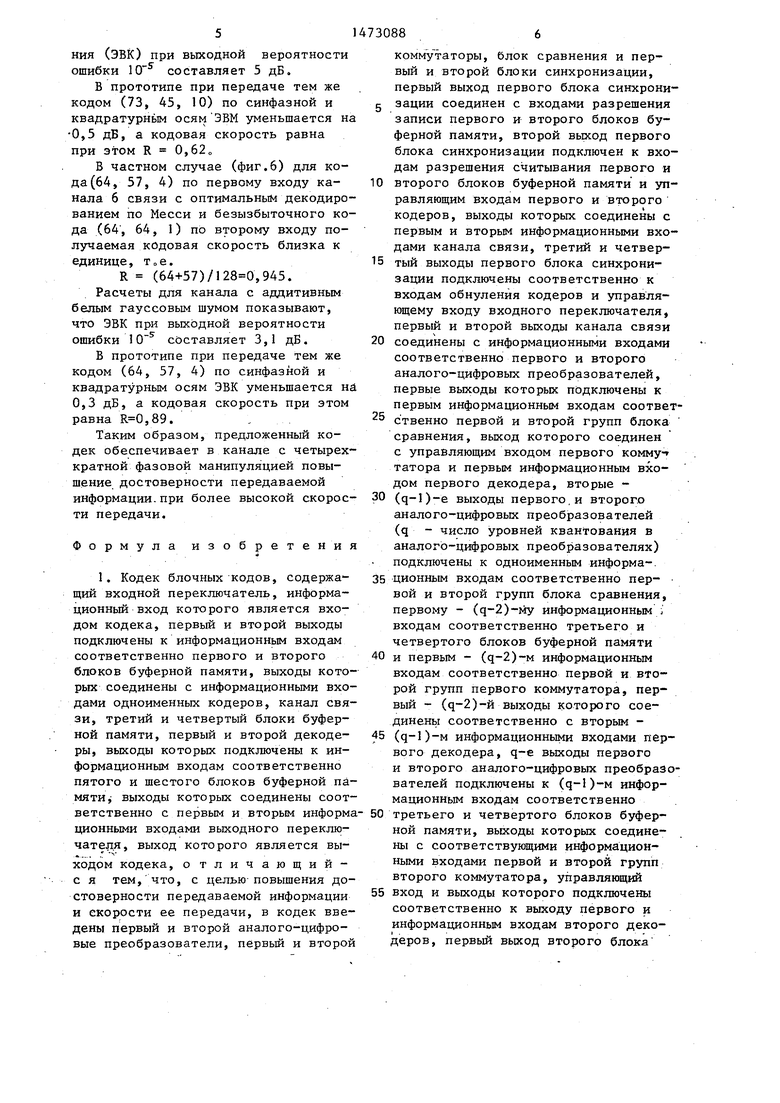

Второй блок 20 синхронизации содержит (фиг.4) вьщелитель 39 такто

5

0 5 0

5

0

5

вых импульсов, выделитель 40 цикловых меток, умножитель 41 частоты на 2 п, делитель 42 частоты (на ), первый и второй дешифраторы 43, 44 (определяющие соответственно К и 2К +1) и триггер 45.

Блоки 2, 11 и 16 буферной памяти имеют емкость 2К,, блоки 3,- 12 и 17 буферной памяти имеют емкость 2К-.

Блок 9 сравнения служит для выде- ления большего из двух чисел, при этом на выходе блока 9 формируется логическая 1, если число на первых входах с АЦП 7 больше, чем число на вторых входах с АЦП 8.

Кодеры 4, 5 формируют блочные коды (п. К,, а,)и (п, к, d.2.) где

d,, d - минимальные расстояния соответствующих кодов, KjpK,, d2 d .

На фиг.5 обозначены блоки символов и сигналы: а - на входе кодека; б - на третьем выходе блока 19 (R); в, г-на входах блоков 2 и 3; ж, з - на входах кодеров 4 и 5; и - на третьем выходе блока 20 (R ); к, л - на выходах декодеров 13 и 15; м, и .- на выходах блоков 16 и 17; о - на выходе кодека.

Кодек блочных кодов работает следующим образом.

Рассматривается частный случай четырехкратной фазовой манипуляции, при которой для фазы О модулятор находится в состоянии 00, для фазы 90 01, для фазы 180°- 10 и для фазы 270 - П.

Входной двоичньш сигнал коммутируется переключателем 1 и поочередно по К, и К тактам поступает через блоки 2 и 3 на входы кодеров 4 и 5. При этом в кодерах 4 и 5 каждые К и К информационные символы кодируются, а образованные кодовые слова

(Х Х )

и io I/ ) 1 ff If 1 гУц-чУп I r

на входы канала 6

длины n подаются связи.

,(t

(j

Каждой паре символов J- ,

1,п) на входах канала 6 связи (фиг.2) модулятор 21 ставит в соответствие определенную фазу выходного сигнала, передаваемого в линию 22 связи: паре 00 - фазу О, паре 01 - фазу /2, паре 10 - фазу Т , паре 11 - фазу 3 ;Г /2. Демодулятор, 23 выделяет из принятого сигнала его син-

фазную и квадратную составляющие (), соответствующие кодовому слову длины и принимающие в каждом тактовом интервале одно из множества действительных значений.

Сигналы этих составляющих поступют на входы АЦП 7 и 8, на выходах которьЬс формируются двоичные значе-- ния составляющих:

oim ,...,oi,,oZ,,

Pm J , /i, , где ,q - кратность квантования

(здесь , ); - младшие разряды; ,- старшие разряды. Аналоговые сигналы из канала 6 связи квантуются в АЦП 7 и 8 на q 16 уровней, а на их выходах формируются наборы cooTBeTCTBeHHood o jo zo iK , двоичных значений из символов в соответствии с входными уровнями.

Младший и промежуточные разряды (1-й и 2-й, 3-й) обоих чисел |5гр(3, подаются на входы блока 9 сранения, на выходе которого образуется

сигнал пя

1 при (oi) i ((3) и сигнал О при (о1) - (р). Одновременно промежуточные разряды и ,2 поступают на входы первого коммутатора 10, а также вместе со старшими разрядами и (1 - на входы второго коммутатора 14 через блоки II и 12. Сигнал или О с выхода блока 9 сравнения, являющийся жестким решением () о символах Jj первого кодового слова, поступает на управляющий вход первого коммутатора 10 и на первый вход декодера 13 первого кода. На второй и третий входы декодера 13 подаются промежуточные разряды или/,/3,, определяющие надежность сигнала: разряды подаются, если управля- кяций сигнал первого коммутатора 10 равен О, а разряды если этот управлякнций сигнал равен 1.

В декодере 13 осуществляется корректировка символов входного слова J I , а на его выходе формируются исправленные символы слова по алгоритму

Г ГГ©-Г (J .); где © - знак суммирования по модулю два;

е. -г символы ошибок, выявленные декодером 1 3.

4730884

Эти исправленные символы поступают на первый вход выходного переключателя 18 и управляющий вход второ- го коммутатора 14, на входы которого поданы промежуточные и старшие разряды oL и /i., задержанные в блоках 11 и 12 на время декодирования.

10 Ксли на управляющем входе второго коммутатора 14 сигнал равен О, то на его выход прохоДят промежуточные и старший разряды первого АЦП 7, если же 1 -р,/З, /,второго

15 АЦП 8. В декодере 15 осуществляется корректировка по алгоритму i() (i1

20

u /ifi i © e . Таким образом, на входы выходного ключа 8 поступают декодированные

35

по промежуточным разрядам (третьему и второму) сигнал первого кода и по промежуточным и,старшему разрядам (четвертому, третьему и второму) сиг- 25 нал второго кода, а на выходе переключателя 18 формируются поочередно блоки из К, и К 2 декодированных символов .

В случа1е, если в качестве второ- 30 го кода выбрать безызбыточный код (п,п,}), то вторые кодер 5 и декодер 15 становятся ненужными. К третьему и четвертому блокам П, 12 буферной памяти подключаются лишь старшие разряды соответствующих АЦП 7, 8, которые далее поступают на коммутатор 14, вход и выход которого соединены о соответствующими входами переключателя 18 напрямую Q (фиг.6, 7). На фиг.7 обозначены блоки символов и сигналы: а - на входе кодека; б - на .третьем выходе блока 19 (R); в, г-на входах блоков 2,3; д, е - на выходах блоков 2 и 3; ж - на третьем выходе блока 20 (R); з - на выходе декодера 13; и, к - на выходах блоков 11 и 12; л - на выходе кодека,

В общем случае (фиг,J), если в ка- д честве первого кода взять проектив- но-геометрический код (73, 45, 10), а в качестве второгр - расширенный проверкой на четность укороченный код Хэмминга (73, 65, 4), то полу- J чаемая кодовая скорость составляет

R 11 0/146 « 0,75. Расчеты для канала с аддитивным белым гауссовым шумом показывают, что энергетический выигрыш кодирова5

ния (ЭВК) при выходной вероятности ошибки 10 составляет 5 дБ.

В прототипе при передаче тем же кодом (73, 45, 10) по синфазной и квадратурнь1М осям ЭВМ уменьшается на -0,5 дБ, а кодовая скорость равна при этом R 0,62о

В частном случае (фиг.6) для кода (64, 57, 4) по первому входу канала 6 связи с оптимальным декодированием по Месси и безызбыточного кода (64, 64, 1) по второму входу получаемая кодовая скорость близка к единице, .

R (64+57),945.

Расчеты для канала с аддитивным белым гауссовьш шумом показывают, что ЭВК при выходной вероятности ошибки 10 составляет 3,1 дБ.

В прототипе при передаче тем же кодом (64, 57, 4) по синфазной и квадратурным осям ЭВК уменьшается на 0,3 дБ, а кодовая скорость при этом равна ,89.

Таким образом, предложенный кодек обеспечивает в канале с четырехкратной фазовой манипуляцией повышение достоверности передаваемой информации.при более высокой скорости передачи.

Формула изобретения

1. Кодек блочных кодов, содержащий входной переключатель, информационный вход которого является входом кодека, первый и второй выходы подключены к информационным входам соответственно первого и второго блоков буферной памяти, выходы которых соединены с информационными входами одноименных кодеров, канал связи, третий и четвертый блоки буферной памяти, первый и второй декодеры, выходы которых подключены к информационным входам соответственно пятого и шестого блоков буферной памяти j выходы которых соединены соот

коммутаторы, блок сравнения и первый и второй блоки синхронизации, первый выход первого блока синхронизации соединен с входами разрешения записи первого и второго блоков буферной памяти, второй вьрсод первого блока синхронизации подключен к входам разрешения считывания первого и

второго блоков буферной памяти и управляющим входам первого и второго кодеров, выходы которых соединены с первым и вторым информационными входами канала связи, третий и четвертый выходы первого блока синхронизации подключены соответственно к входам обнуления кодеров и управляющему входу входного переключателя, первый и второй выходы канала связи

соединены с информационными входами соответственно первого и второго аналого-цифровых преобразователей, первые выходы которых подключены к первым информационным входам соответственно первой и второй групп блока сравнения, выход которого соединен с управляющим входом первого комму- татора и первым информационным входом первого декодера, вторые (q-l)-e выходы первого,и второго аналого-цифровых преобразователей (q - число уровней квантования в аналого-цифровых преобразователях) подключены к одноименным информа-.

ционным входам соответственно первой и второй групп блока сравнения, первому - (q-2)-My информационным J входам соответственно третьего и четвертого блоков буферной памяти

и первым - (q-2)-M информационным входам соответственно первой и второй групп первого коммутатора, первый - (q-2)-и выходы которого соединены соответственно с вторым (q-l)-M информационными входами первого декодера, q-e выходы первого и второго аналого-цифровых преобразователей подключены к (q-l)-M инфор- мационньм входам соответственно

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек двоичных блочных кодов | 1986 |

|

SU1408532A1 |

| Система для передачи информации с двукратной фазовой манипуляцией сверточным кодом | 1982 |

|

SU1027748A1 |

| Кодек блочных кодов | 1984 |

|

SU1270899A1 |

| Кодек блочных кодов | 1988 |

|

SU1640829A1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Кодек для системы связи с многократной фазовой модуляцией | 1987 |

|

SU1629992A1 |

| ЦИФРОВОЙ МОДЕМ ИНФОРМАЦИОННОЙ РАДИОЛИНИИ ЦМ ИРЛ | 2013 |

|

RU2583715C2 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

Изобретение относится к вычислительной технике и технике связи. Цель изобретения - повышение достоверности передаваемой информации и скорости ее передачи. Кодек содержит входной переключатель 1, блоки 2,3,11,12,16,17 буферной памяти, кодеры 4,5, канал 6 связи, декодеры 13,15 и выходной переключатель 18. Благодаря введению аналого-цифровых преобразователей 7,8, блока 9 сравнения и коммутаторов 10,14, а также блоков 19,20 синхронизации поставленная цель обеспечивается как в случае использования двух блочных кодов одинаковой длины, так и в случае использования одного блочного кода и безызбыточного кода одинаковой длины. 3 з.п. ф-лы, 7 ил.

ветственно с первым и вторьм информа- 50 третьего и четвертого блоков буферной памяти, выходы которых соединены с соответствующими информационными входами первой и второй групп второго коммутатора, управляющий 55 вход и выходы которого подключены соответственно к выходу первого и информационным входам второго декодеров, первый выход второго блока

ционными входами выходного переключателя, выход которого является вы

ХОДОМ кодека, о тличающий- с я тем, что, с целью повышения достоверности передаваемой информации и скорости ее передачи, в кодек введены первый и второй аналого-цифровые преобразователи, первый и второй

синхронизации соединен с входами разрешения считывания третьего - ще- стого блЛсов буферной памяти, второй выход второго блока синхронизации подключен к входам разрешения записи третьего - шестого блоков буферной памяти, управляющим входам декодеров, аналого-цифровых преобразователей, блока сравнения и канала связи, третий выход которого соеди- нен с входом второго блока синхронизации, третий и четвертый выходы которого подключены соответственно к входам обнуления декодеров и управляющему входу выходного переключателя.

2 о Кодек поп.1,отличаю- щ и и с я тем, что канал связи содержит генератор сигнала несущей, модулятор, включающий в себя первый и второй фазовые манипуляторы, линию связи, синхронизатор по несущей и демодулятор, включающий в себя первый и второй синхронные перемножители, квадратурный фазовращатель и первый и второй интеграторы, выходы которьк являются первым и вторым выходами канала, первые входы первого и второго фазовых манипуляторов модулятора являются соответственно пер- вьм и вторым информационными входа- ми канала, выход генератора сигнала несущей соединен с вторым входом второго фазового манипулятора модулятора, выход которого подключен к второму входу первого фазового манипулятора одулятора, выход которого через линию связи соединен с входом синхронизатора по несущей, первыми входами синхронных перемнржителей емодулятора и явлйется третьим выодом канала, выход синхронизатора о несущей непосредственно и через вадратурный фазовращатель демодуятора подключен к вторым входам сответственно первого и второго синронных перемножителей демодулятора, ыходы которых соединены с информационными входами одноименных интеграторов демодулятора, управляющие входы которых объединены и являются J управляющим входом канала.

дешифраторы, триггер и генератор тактовых импульсов, выход которого соединен с входом умножителя частоты и является первым выходом блока, выход t5 переполнения делителя частоты является рторым выходом блока, выходы разрядов делителя частотц соединены с входами дешифраторов, выход первого дешифратора подключен к R-входу триг- 0 гера и является третьим выходом блока, выход второго дешифратора соединен с S-входом триггера, выход ко- то.рого является четвертым выходом блокао .

5 4. Кодек поп.1,отличаю- щ и и с я тем, что второй блок синхронизации содержит вьделитель тактовых импульсов, умножитель частоты, делитель частоты, первый и второй 0 дешифраторы, триггер и выделитель цикловых меток, вход которого объединен с входом вьщелителя тактовых импульсов и является входом блока, выход выделителя тактовых импульсов 5 соединен с входом умножителя частоты и является первым выходом блока, выход умножителя частоты соединен с счетным входом делителя частоты, выход переполнения которого является 0 вторым вьгходом блока, выход выделителя цикловых меток.подключен к входу обнуления делителя частоты и является третьим выходом блока, выходы разрядов делителя частоты соединены 5 с входами первого и второго дешифраторов, выходы которых подключены соответственно к R- и S-входам триг- гера, выход которого является четвертым выходом блока.

фиг.г

ъъ

J4t

L..

(fJus.

l.

(

..

36

3

N

J

Й

V I Чг (1) Н((2) Ki(Z} Ki{i) Kt (t) I /V

РШТ

nr/vT

/rw

ПгГТгТ

11-oe CM8C I -of wyg { 3-е c/iefo

мГ )

°)

шш

I /Tzf/l

Ki{i} K,(t Ki(i Hiti

-1 w

Btarog

Фиг. 1

f I -I fffzj

J((1} H(4) l/ffZJI nfin

| IEEE Transactions on Information -Theory | |||

| V | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Кодек мажоритарного блочного кода | 1981 |

|

SU965000A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-04-15—Публикация

1987-08-27—Подача