(21)4240321/24-24

(22)05.05.87

(46) 23.04.89. Бюл. № 15

(71)Ленинградский электротехнический институт связи им. проф.М.А.Еонч-Бру- евича

(72)А.Ю.Бухинник, Б.Е„Трофимов и П.Е.Щербатьй

(53)621.376.56(088.8)

(56)Авторское свидетельство СССР № 349080, кл. Н 03 М 3/02, 1970.

Электросвязь, 1979, № 11, с. 38-40, рис. 1.

Авторское свидетельство СССР № 1129732, кл. Н 03 М 3/02, 1983.

(54)ДЕЛЬТА-МОДУЛЯТОР

(57)Изобретение относится к автоматике и технике связи. Его использова/5

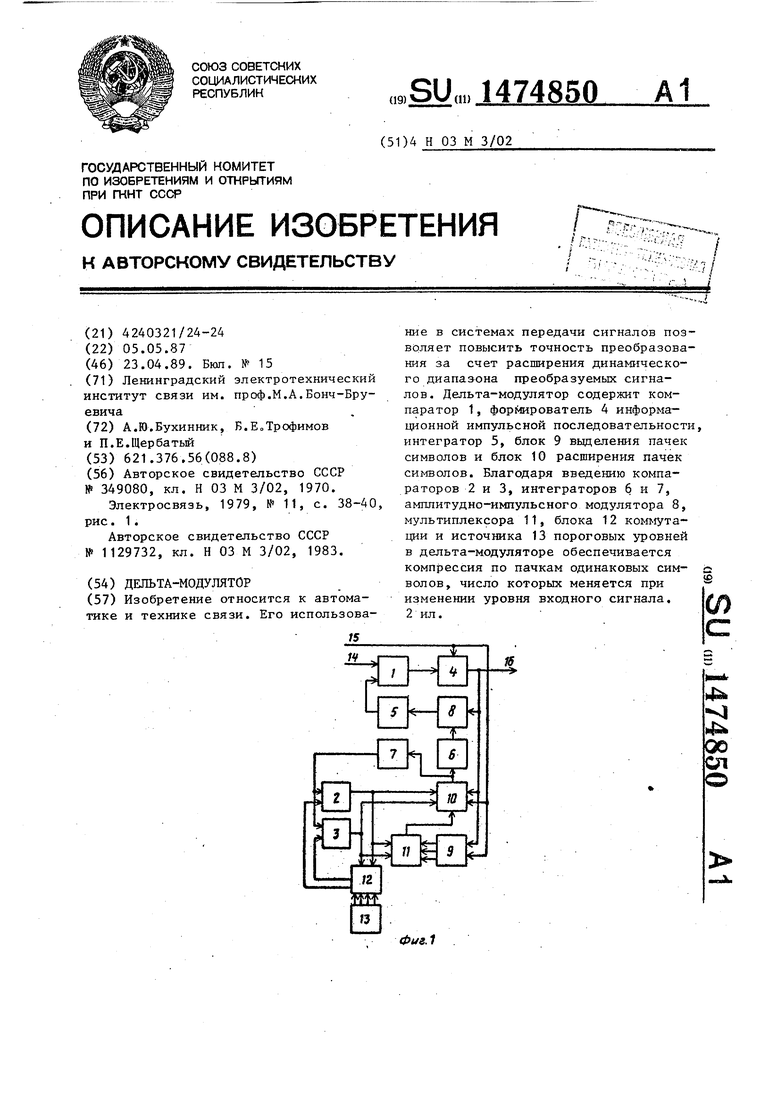

ние в системах передачи сигналов позволяет повысить точность преобразования за счет расширения динамического диапазона преобразуемых сигналов. Дельта-модулятор содержит компаратор 1, формирователь 4 информационной импульсной последовательности, интегратор 5, блок 9 выделения пачек символов и блок 10 расширения пачек символов. Благодаря введению компараторов 2 и 3, интеграторов 6 и 7, амплитудно-импульсного модулятора 8, мультиплексора 11, блока 12 коммутации и источника 13 пороговых уровней в дельта-модуляторе обеспечивается компрессия по пачкам одинаковых символов, число которых меняется при изменении уровня входного сигнала. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор для передачи речевых сигналов | 1990 |

|

SU1795554A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| Устройство конференц-связи для систем с дельта-модуляцией | 1986 |

|

SU1418926A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Дельта-модулятор | 1983 |

|

SU1129732A1 |

| СПОСОБ ВОССТАНОВЛЕНИЯ ИСХОДНОГО СИГНАЛА ПРИ ДЕЛЬТА-МОДУЛЯЦИИ И УСТРОЙСТВО ДЛЯ ДЕЛЬТА-ДЕМОДУЛЯЦИИ | 1994 |

|

RU2129333C1 |

| Кодек адаптивного дельта-модулятора | 1986 |

|

SU1378063A1 |

| Устройство конференц-связи | 1977 |

|

SU655091A1 |

Изобретение относится к автоматике и технике связи. Его использование в системах передачи сигналов позволяет повысить точность преобразования за счет расширения динамического диапазона преобразуемых сигналов. Дельта-модулятор содержит компаратор 1, формирователь 4 информационной импульсной последовательности, интегратор 5, блок 9 выделения пачек символов и блок 10 расширения пачек символов. Благодаря введению компараторов 2,3, интеграторов 6,7, амплитудно-импульсного модулятора 8, мультиплексора 11, блока 12 коммутации и источника 13 пороговых уровней в дельта-модуляторе обеспечивается компрессия по пачкам одинаковых символов,число которых меняется при изменении уровня входного сигнала. 2 ил.

4ь

4

Јь

00 От

114

Изобретение относится к автоматике и технике связи и может быть использовано в системах передачи сигналов.

Цель изобретения - повышение точности преобразования за счет расширения динамического диапазона преобразуемых сигналов.

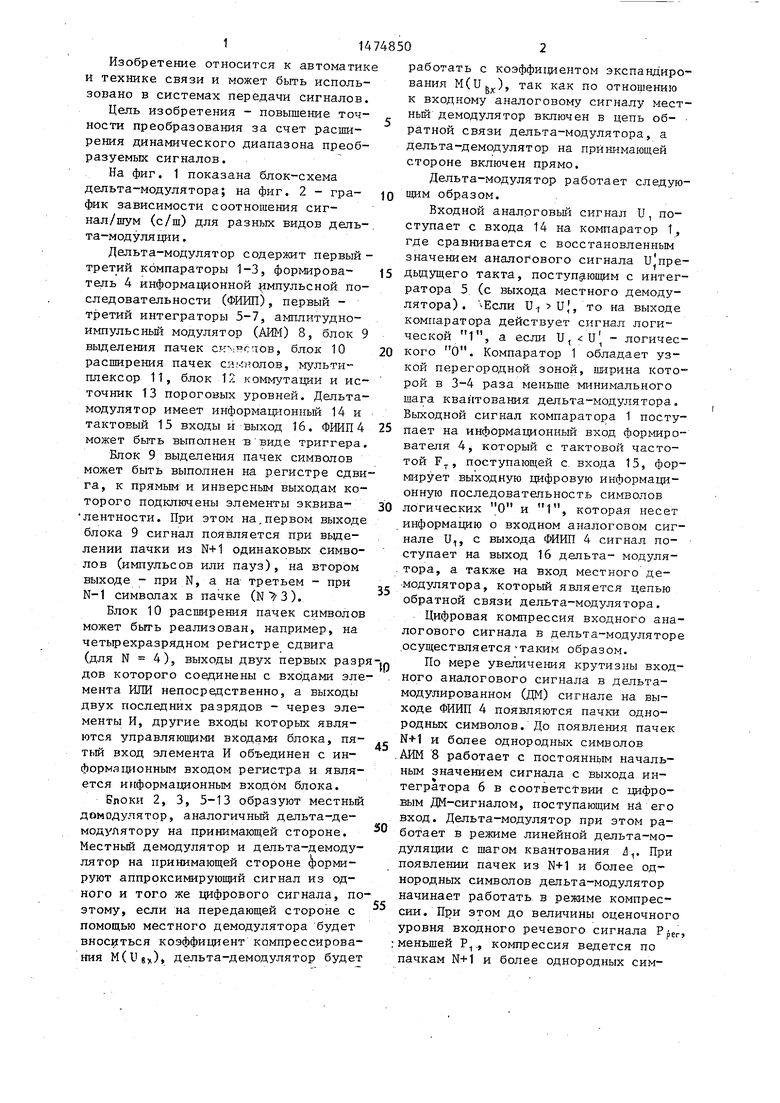

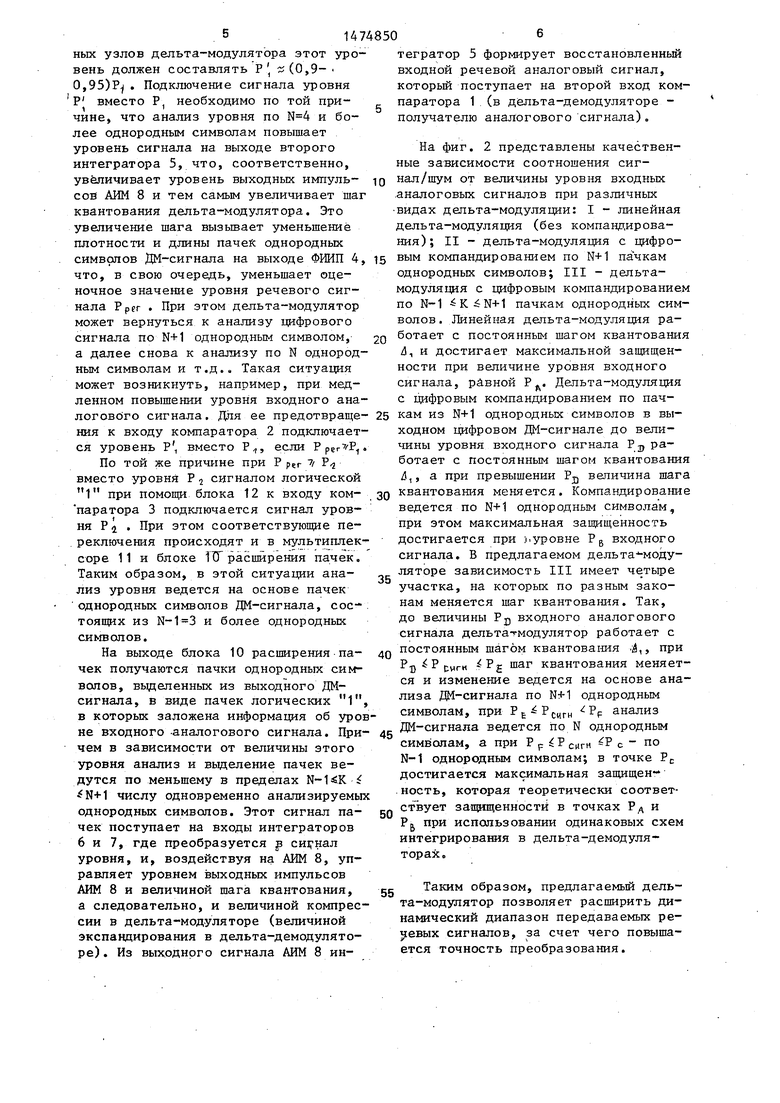

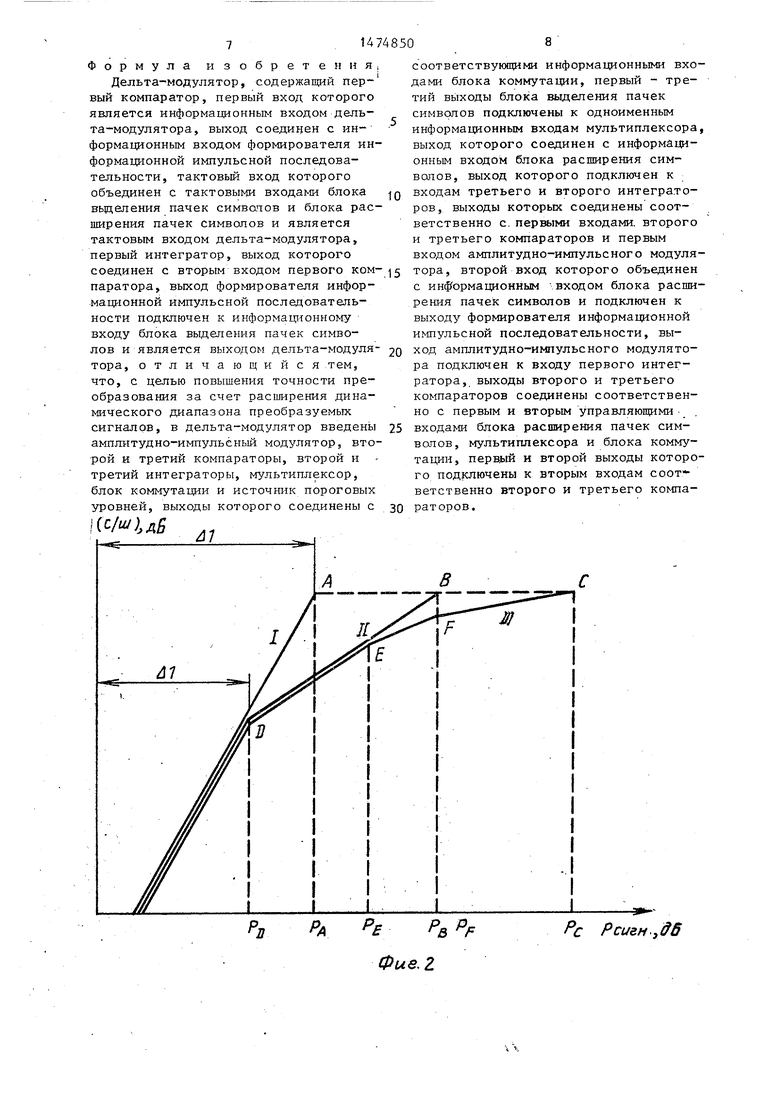

На фиг. 1 показана блок-схема дельта-модулятора; на фиг. 2 - график зависимости соотношения сигнал/шум (с/ш) для разных видов дельта-модуляции .

Дельта-модулятор содержит первый - третий компараторы 1-3, формирователь 4 информационной импульсной последовательности (ФИИП), первый - третий интеграторы 5-7, амплитудно- импульсный модулятор (АИМ) 8, блок 9 выделения пачек , блок 10 расширения пачек елФРОЛОВ, мультиплексор 11, блок 12 коммутации и источник 13 пороговых уровней. Дельта- модулятор имеет информационный 14 и тактовый 15 входы и выход 16. ФИИП4 может быть выполнен в виде триггера.

Блок 9 выделения пачек символов может быть выполнен на регистре сдвига, к прямым и инверсным выходам которого подключены элементы эквива- лентности. При этом на,первом выходе блока 9 сигнал появляется при выделении пачки из N+1 одинаковых символов (импульсов или пауз), на втором выходе - при N, а на третьем - при N-1 символах в пачке (ЮЗ).

Блок 10 расширения пачек символов может быть реализован, например, на четырехразрядном регистре сдвига (для N 4), выходы двух первых разр дов которого соединены с входами элемента ИЛИ непосредственно, а выходы двух последних разрядов - через элементы И, другие входы которых являются управляющими входами блока, пятый вход элемента И объединен с информационным входом регистра и является информационным входом блока.

Блоки 2, 3, 5-13 образуют местный демодулятор, аналогичный дельта-демодулятору на принимающей стороне. Местный демодулятор и дельта-демодулятор на принимающей стороне формируют аппроксимирующий сигнал из одного и того же цифрового сигнала, поэтому, если на передающей стороне с помощью местного демодулятора будет вноситься коэффициент компрессирования М(и8), дельта-демодулятор будет

работать с коэффициентом экспандиро- вания M(U6x), так как по отношению к входному аналоговому сигналу местный демодулятор включен в цепь обратной связи дельта-модулятора, а дельта-демодулятор на принимающей стороне включен прямо.

Дельта-модулятор работает следующим образом.

Входной аналоговый сигнал U, поступает с входа 14 на компаратор 1, где сравнивается с восстановленным значением аналогового сигнала и пре- дыдущего такта, поступающим с интегратора 5 (с выхода местного демодулятора) . Если ,, то на выходе компаратора действует сигнал логической 1

а если

U, 1 - логичес0 кого О. Компаратор 1 обладает узкой перегородкой зоной, ширина которой в 3-4 раза меньше минимального шага квантования дельта-модулятора. Выходной сигнал компаратора 1 посту5 пает на информационный вход формирователя 4, который с тактовой частотой FT, поступающей с входа 15, формирует выходную цифровую информаци

онную последовательность символов логических О и 1,

которая несет

информацию о входном аналоговом сигнале U1, с выхода ФИИП 4 сигнал поступает на выход 16 дельта- модулятора, а также на вход местного демодулятора, который является цепью обратной связи дельта-модулятора.

Цифровая компрессия входного аналогового сигнала в дельта-модуляторе осуществляется-таким образом.

По мере увеличения крутизны входного аналогового сигнала в дельта- модулированном (ДМ) сигнале на выходе ФИИП 4 появляются пачки однородных символов. До появления пачек N+1 и более однородных символов АИМ 8 работает с постоянным начальным значением сигнала с выхода интегратора 6 в соответствии с цифровым ДМ-сигналом, поступающим на его вход. Дельта-модулятор при этом работает в режиме линейной дельта-модуляции с шагом квантования d,. При появлении пачек из N+1 и более однородных символов дельта-модулятор начинает работать в режиме компрессии. При этом до величины оценочного уровня входного речевого сигнала , ;меньшей Р1, компрессия ведется по пачкам N+1 и более однородных символов, при Р1 Р per Ј Р2 компрессия ведется по пачкам из N и более однородных СИМВОЛОВ И При Ррег7/ Р КОМпрессия ведется по пачкам из N-1 и более однородных символов.

Управление шагом квантования дель та-модулятора в зависимости от оценочного уровня входных речевых сигналов осуществляется с помощью блоков 2, 3, 7, 9-13. При этом интегратор 7 может быть как аналоговым, так и цифровым. В зависимости от этого соответственно компараторы 2 и 3 должны быть аналоговыми либо цифровыми. В последнем случае число разрядов компаратора соответствует разрядности цифрового интегратора 7. Источник 13 должен формировать четыре уровня Р,, Р т, Р2|рЈв аналоговом или в цифровом виде. Соответственно и блок 12 коммутации должен содержать либо цифровые соответствующей разрядности двухканалыше коммутаторы, либо аналоговые.

Рассмотрим пример с аналоговым формированием оценочных значений уровня сигнала. Тогда интегратор 7 выполняется в виде двойного интегратора, на котором из пачек однородных символов, выделенных блоком 10 из выходного ДМ-сигнала, формируется оценочное значение уровня входного аналогового сигнала.

Рассмотрим процесс адаптации шага квантования в дельта-модуляторе под величину уровня входного аналогового сигнала. При повышении уровня этого сигнала на выходе ФИШ 4 в ДМ- сигнале появляются пачки однородных символом. ДМ-сигнал поступает в блок 9 выделения пачек символов, где подается на информационный вход пятиразрядного регистра сдвига. До величины оценочного уровня входного сигнала, равной Р, , блок 9 работает на выделение пачек из и более символов. На пятом такте после поступ- ления пачки из пяти однородных символов на пяти разрядах регистра появляются одинаковые логические символы При этом на выходе соответствующего элемента эквивалентности блока 9 появляется сигнал. Таким образом выдел ются пачки однородных символов, однако при этом сокращается длительность выделенных пачек до одного такта. Суммарный поток сигналов, соответствующих пачкам из N+1 однородных

0

5

0

5

0

5

0

5

0

5

символов, поступает на мультиплексор 11, которым управляют сигналы с выходов компараторов 2 и 3.

Компаратор 2 сравнивает оценочное значение уровня входного аналогового сигнала с уровнем Р,, а компаратор 3-е уровнем Рг до тех пор, пока Р per -- Р Р. Если Ррег7, pf, на выходе компаратора 2 появляется сигнал логической 1, который, управляя блоком 12 коммутации, подключает к входу компаратора 2 сигнал Р , от источника 13.

Таким образом, если Р рег , Рг, на выходе компаратора 3 появляется сигнал логической 1, который, управляя блоком 12 коммутации, подключает к входу компаратора 3 сигнал Р а . Так как в указанной ситуации Р per , на выходах компараторов 2 и 3 действуют сигналы логического О. Поступая на управляющие входы мультиплексора 11, они управляют подключением сигнала с первого выхода блока 9 к бтоку 10 расширения пачек символов. При этом сигнал логического О компараторов 2 и 3, поступая на управляющие входы блока 10, разрешает прохождение символов со всех разрядов его регистра сдвига на элемент ИЛИ, в результате чего на выходе последнего, т.е. на выходе блока 10, восстанавливается начальная длительность пачки из однородных символов.

При дальнейшем увеличении уровня входного аналогового сигнала число и длительность пачек увеличиваются, а следовательно, увеличивается оценочное значение уровня Р рег , формируемое интегратором 7. Если Р per Р,, то на выходе компаратора 2 появляется сигнал логической 1. Этот сигнал подключает второй выход блока 9 (пачки из символов) к информационному входу блока 10, в котором от элемента ИЛИ отключается выход последнего разряда регистра сдвига. При этом блок 10 восстанавливает начальную длительность лишь пачек, состоящих из однородных символов. Сигнал логической 1 с выхода компаратора 2 поступает в блок 12 коммутации и подключает к входу компаратора 2 сигнал уровня Pi, , сформированный источником 13. В зависимости от начального шага квантования, частоты тактирования и особенностей схемного решения отдель-

ных узлов дельта-модулятора этот уровень должен составлять Р 2(0,9- 0,95)Р . Подключение сигнала уровня Р вместо Р, необходимо по той причине, что анализ уровня по и более однородным символам повышает уровень сигнала на выходе второго интегратора 5, что, соответственно, увеличивает уровень выходных импуль- cos АИМ 8 и тем самым увеличивает шаг квантования дельта-модулятора. Это увеличение шага вызывает уменьшение плотности и длины пачек однородных

симврлов ДМ-сигнала на выходе ФИИП 4, 15 вым компандированием по N+1 пачкам

что, в свою очередь, уменьшает оценочное значение уровня речевого сигнала Ррег . При этом дельта-модулятор может вернуться к анализу цифрового сигнала по N+1 однородным символом, а далее снова к анализу по N однородным символам и т.д.. Такая ситуация может возникнуть, например, при медоднородных символов; III - дельта- модуляция с цифровым компандированием по N-1 KiN+1 пачкам однородных символов. Линейная дельта-модуляция работает с постоянным шагом квантования Лл и достигает максимальной защищенности при величине уровня входного сигнала, равной Pft. Дельта-модуляция с цифровым компандированием по пачленном повышении уровня входного аналогового сигнала. Для ее предотвраще- 25 кам из N+1 однородных символов в вы- ния к входу компаратора 2 подключает- ходном цифровом ДМ-сигнале до велися уровень Р , вместо Р,,, если ,.

По той же причине при Р ftr i P вместо уровня Р 2 сигналом логической 1 при помощи блока 12 к входу ком- паратора 3 подключается сигнал уровня Р i . При этом соответствующие переключения происходят и в мультиплексоре 11 и блоке 11T расширения пачек. Таким образом, в этой ситуации анализ уровня ведется на основе пачек однородных символов ДМ-сигнала, состоящих из и более однородных символов.

На выходе блока 10 расширения пачек получаются пачки однородных символов, выделенных из выходного ДМ- сигнала, в виде пачек логических 1,

ся и изменение ведется на основе ан лиза ДМ-сигнала по N+1 однородным символам, при РЕ РСИГН Рр анализ

50

в которых заложена информация об уровне входного аналогового сигнала. При- 45 да-сигнала ведется по N однородным чем в зависимости от величины этогосимволам, а при Р сЈ Р гигн Р с - по

уровня анализ и выделение пачек ведутся по меньшему в пределах N-14K Ј N+1 числу одновременно анализируемых однородных символов. Этот сигнал пачек поступает на входы интеграторов 6 и 7, где преобразуется в сигнал уровня, и, воздействуя на АИМ 8, управляет уровнем выходных импульсов АИМ 8 и величиной шага квантования, а следовательно, и величиной компрессии в дельта-модуляторе (величиной экспандирования в дельта-демодуляторе) . Из выходного сигнала АИМ 8 ина при Рр ЈРСцГН г с N-1 однородным символам; в точке Р достигается максимальная защищенность, которая теоретически соответ ствует защищенности в точках Рл и РЬ при использовании одинаковых схе интегрирования в дельта-демодулятор ах.

5,- Таким образом, предлагаемый дель та-модулятор позволяет расширить ди намический диапазон передаваемых ре чевых сигналов, за счет чего повыша ется точность преобразования.

тегратор 5 формирует восстановленный входной речевой аналоговый сигнал, который поступает на второй вход компаратора 1 (в дельта-демодуляторе - получателю аналогового сигнала)„

На фиг. 2 представлены качественные зависимости соотношения сиг- 0 нал/шум от величины уровня входных аналоговых сигналов при различных видах дельта-модуляции: I - линейная дельта-модуляция (без компандирова- ния); II - дельта-модуляция с цифро

однородных символов; III - дельта- модуляция с цифровым компандированием по N-1 KiN+1 пачкам однородных символов. Линейная дельта-модуляция работает с постоянным шагом квантования Лл и достигает максимальной защищенности при величине уровня входного сигнала, равной Pft. Дельта-модуляция с цифровым компандированием по пачкам из N+1 однородных символов в вы- ходном цифровом ДМ-сигнале до величины уровня входного сигнала 7 э работает с постоянным шагом квантования Л,, а при превышении P.Q величина шага квантования меняется. Компандирование ведется по N+1 однородным символам, при этом максимальная защищенность достигается при (.уровне Рв входного сигнала. В предлагаемом дельта- -моду- ляторе зависимость III имеет четыре участка, на которых по разным законам меняется шаг квантования. Так, до величины PJJ входного аналогового сигнала дельта- модулятор работает с постоянным шагом квантования .&., при

PD P CWI-H

Pg шаг квантования меняется и изменение ведется на основе анализа ДМ-сигнала по N+1 однородным символам, при РЕ РСИГН Рр анализ

да-сигнала ведется по N однородным символам, а при Р сЈ Р гигн Р с - по

да-сигнала ведется по N однородным символам, а при Р сЈ Р гигн Р с - по

а при Рр ЈРСцГН г с N-1 однородным символам; в точке Рс достигается максимальная защищенность, которая теоретически соответствует защищенности в точках Рл и РЬ при использовании одинаковых схем интегрирования в дельта-демодулятор ах.

Таким образом, предлагаемый дельта-модулятор позволяет расширить ди- намический диапазон передаваемых речевых сигналов, за счет чего повышается точность преобразования.

Формула изобретения, Дельта-модулятор, содержащий пер- вый компаратор, первый вход которого является информационным входом дельта-модулятора, выход соединен с информационным входом формирователя информационной импульсной последовательности, тактовый вход которого объединен с тактовыми входами блока выделения пачек символов и блока расширения пачек символов и является тактовым входом дельта-модулятора, первый интегратор, выход которого соединен с вторым входом первого ком- паратора, выход формирователя информационной импульсной последовательности подключен к информационному входу блока выделения пачек символов и является выходом дельта-модуля

тора, отличающийся тем, что, с целью повышения точности преобразования за счет расширения динамического диапазона преобразуемых сигналов, в дельта-модулятор введены амплитудно-импульсный модулятор, второй и третий компараторы, второй и третий интеграторы, мультиплексор, блок коммутации и источник пороговых уровней, выходы которого соединены с

РА

Q

0

5

соответствующими информационными входами блока коммутации, первый - третий выходы блока выделения пачек символов подключены к одноименным информационным входам мультиплексора, выход которого соединен с информационным входом блока расширения символов, выход которого подключен к входам третьего и второго интеграторов, выходы которых соединены соответственно с первыми входами, второго и третьего компараторов и первым входом амплитудно-импульсного модулятора, второй вход которого объединен с информационным входом блока расширения пачек символов и подключен к выходу формирователя информационной импульсной последовательности, выход амплитудно-импульсного модулятора подключен к входу первого интегратора, выходы второго и третьего компараторов соединены соответственно с первым и вторым управляющими входами блока расширения пачек символов, мультиплексора и блока коммутации, первый и второй выходы которого подключены к вторым входам ветственно второго и третьего компараторов.

PC Рсигн,30б

Авторы

Даты

1989-04-23—Публикация

1987-05-05—Подача