Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении универсальных и специализированных управляющих устройств, а также вычислительных устройств.

Известны вычислительные устройства, например:

"Параллельный сумматор" (авторское свидетельство СССР N 1594523, кл. G 06 F 7/49, 1990). Он содержит блок формирования отрицательной суммы, блок формирования положительного переноса, первый элемент И-НЕ, второй элемент И-НЕ, первый элемент ИЛИ-НЕ, второй элемент ИЛИ-НЕ, первый и второй триггер. Может быть использовано в множительных устройствах, работающих в избыточной системе считывания. Недостатком данного устройства является ограниченная область применения.

"Сумматор-вычислитель" (авторское свидетельство СССР N 1536373, кл. G 06 F 7/49, 1990). Он содержит блок поразрядного сложения, блок поразрядной коррекции, два элемента "ИЛИ", пять элементов "И". Может быть использован в вычислительных машинах, работающих в произвольных системах счисления. Недостатком данного устройства является ограниченная область применения.

Наиболее близким по технической сущности к предлагаемому вычислительному устройству является вычислительное устройство (см. авторское свидетельство СССР N 1517024, кл. G 06 F 7/50), содержащее сумматор, два блока инвертирования, элемент "И", два элемента "Запрет" и четыре элемента "Исключающее ИЛИ". Сумматор, первый знаковый выход которого подключен к первому знаковому входу блока запрета, выход "Переполнение" которого является выходом вычислительного устройства. Устройство выполняет операции сложения и вычитания чисел с разными знаками, представленных прямыми кодами, и формирует результат в прямом коде.

Однако устройство-прототип имеет недостаток: ограниченная область применения. Это связано с отсутствием возможности прямого применения в устройствах управления радиоэлектронными системами в управляющих вычислительных машинах, где необходима нелинейная зависимость выходных сигналов от результатов вычислений и функциональный контроль состояния вычислительного устройства.

Целью изобретения является разработка вычислительного устройства, обладающего более широкой областью применения за счет дополнительной обработки результатов арифметических действий.

Поставленная цель достигается тем, что в известное вычислительное устройство, содержащее блок запрета, сумматор, первый знаковый выход которого подключен к первому знаковому входу блока запрета, выход "Переполнение" которого является выходом вычислительного устройства, дополнительно введены блок управления, блок преобразования результатов, кодоформирователь. 2N информационных входов, где N=4, 5, 6 ..., блока управления являются информационными входами вычислительного устройства. Вход "Разрешение" блока управления подключен к выходу "Разрешение" блока запрета, 2N выходов блока управления подключены к соответствующим 2N входам сумматора. Второй знаковый выход сумматора подключен ко второму знаковому входу блока запрета, N-2 выходов сумматора подключены к соответствующим N-2 входам блока преобразования результатов. Первый и второй запрещающие входы блока преобразования результатов подключены к соответствующим запрещающим выходам блока запрета, N-2 групп установочных входов блока преобразования результатов подключены к соответствующим N-2-м группам установочных выходов кодоформирователя, k информационных выходов, где k= ] log2(N-1)+l[(] [- результат округляется до меньшего целого), и выход "max" блока преобразования результатов являются соответственно информационными k выходами и выходом "max" вычислительного устройства.

Блок управления состоит из 2N двухвходовых элементов "И", первый вход i-го элемента "И", где i=1, 2,..., 2N, является соответственно i-ым информационным входом блока управления, вторые входы всех элементов "И" соединены в параллель и являются входом "Разрешение" блока управления, выход i-го элемента "И" является i-ым выходом блока управления.

Сумматор состоит из N элементарных полных сумматоров, первый и второй входы j-го, где j=1, 2,3,..., N, элементарного полного сумматора являются соответственно (2j-1)-ым и 2j-ым входами сумматора, а выход u-го элементарного полного сумматора, где u=1, 2, 3,..., N-2, является u-м выходом сумматора, а выходы (N-1)-го и N-го элементарных полных сумматоров являются соответственно первым и вторым знаковыми выходами сумматора, причем вход переноса m-го элементарного полного сумматора, где m= 1, 2,3,..., N-1, подключен к выходу переноса m+l-го элементарного полного сумматора.

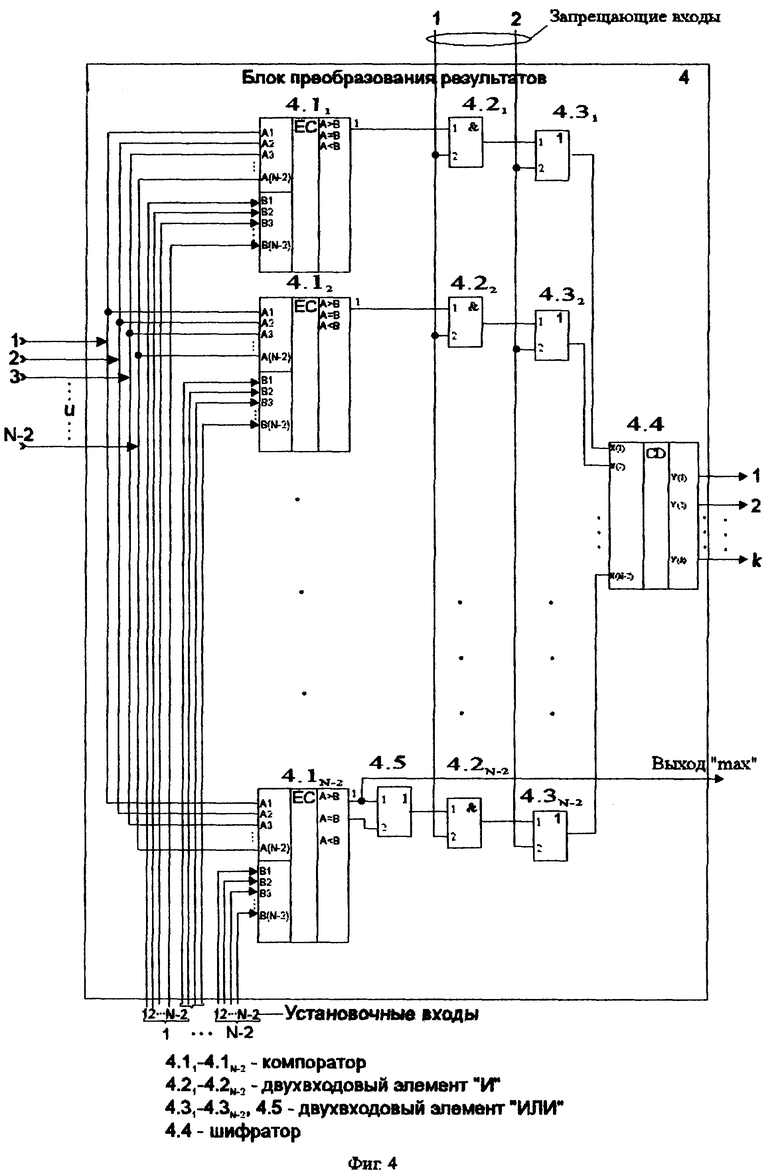

Блок преобразования результатов состоит из N-2-x компараторов, каждый из которых содержит первую группу из N-2-x входов и вторую группу из N-2-x входов, N-2 двухвходовых элементов "И", N-2 двухвходовых элементов "ИЛИ", N-2- входовый шифратор и дополнительный двухвходовый элемент "ИЛИ". Входы первой группы из N-2- x входов компараторов включены в параллель и являются соответствующими входами блока преобразования результатов. Входы второй группы из N-2-х групп входов компараторов являются соответствующими установочными входами блока преобразования результатов, выход s-ого компаратора, где s=l,2,..,N-3, подключен к первому входу s-ro двухвходового элемента "И", выход которого подключен к первому входу u-го двухвходового элемента "ИЛИ", где u=1, 2, 3,... N-2, выход которого является u-м входом шифратора, a k выходов, где k=]log2(N-1)+l[, шифратора являются соответствующими k выходами блока преобразования результатов, вторые входы N-2-x двухвходовых элементов "И" включены в параллель и являются первым запрещающим входом блока преобразования результатов, вторые входы N-2-x двухвходовых элементов "ИЛИ" включены в параллель и является вторым запрещающим входом блока преобразования результатов, причем первый выход N-2-го компаратора подключен к первому входу дополнительного двухвходового элемента "ИЛИ" и является выходом "max" блока преобразования результатов, второй выход N-2-го компаратора подключен ко второму входу дополнительного двухвходового элемента "ИЛИ", выход которого подключен к первому входу N-2-го двухвходового элемента "И".

Блок запрета состоит из двухвходового элемента "И-НЕ", двухвходового элемента "ИСКЛЮЧАЮЩЕЕ ИЛИ", первые входы элементов "И-НЕ" и "ИСКЛЮЧАЮЩЕЕ ИЛИ" подключены параллельно и являются вторым знаковым входом блока запрета, вторые входы элементов "И-НЕ" и "ИСКЛЮЧАЮЩЕЕ ИЛИ" подключены параллельно и являются первым знаковым входом блока запрета, выход элемента "И-НЕ" является выходом "Разрешение" и первым запрещающим выходом блока запрета, выход элемента "ИСКЛЮЧАЮЩЕЕ ИЛИ" является выходом "Переполнение" и вторым запрещающим выходом блока запрета.

Кодоформирователь состоит из N-2-x установочных блоков. Каждый из установочных блоков, состоит из N-2-x резисторов, N-2-x коммутационных элементов и источника питания, выход u-го коммутационного элемента, где u= 1,2,3, . .., N-2, подключен к u-му установочному выходу кодоформирователя, а первый вход u-го коммутационного элемента подключен к первому выводу u-го резистора, второй - заземлен, причем вторые выводы всех резисторов подключены к положительной клемме источника питания, отрицательная клемма которого заземлена.

Благодаря совокупности существенных признаков, заключающихся во введении новых элементов и связей между ними, расширяется область применения вычислительного устройства. Вычислительное устройство позволяет осуществлять функциональный контроль переполнения разрядной сетки, результаты вычислений представляются в двоичном коде в соответствии с некоторой положительной, дискретной, интервальной шкалой при возможности динамического изменения шкалы представления результата, путем изменения кодов порогов, задаваемых в двоичном коде в процессе работы.

Заявленное устройство поясняется чертежами, на которых показаны:

- на фиг. 1 - общая функциональная схема предлагаемого вычислительного устройства;

- на фиг. 2 - функциональная схема блока управления;

- на фиг. 3 - функциональная схема сумматора;

- на фиг. 4 - функциональная схема блока преобразования результатов;

- на фиг. 5 - функциональная схема блока запрета;

- на фиг. 6 - функциональная схема кодоформирователя;

- на фиг. 7 - схема двух позиционного переключателя;

- на фиг. 8 - пример формирования кодов порога.

Вычислительное устройство, показанное на фиг. 1, состоит из блока управления 1, сумматора 2, блок преобразования результатов 4, блок запрета 3, кодоформирователь 5. 2N информационных входов, где N=4, 5, 6..., блока управления 1 являются информационными входами вычислительного устройства. Вход "Разрешение" блока управления подключен к выходу "Разрешение" блока запрета 3. 2N выходов блока управления 1 подключены к соответствующим 2N входам сумматора 2. Первый знаковый выход сумматора 2 подключен к первому знаковому входу блока запрета 3. Второй знаковый выход сумматора 2 подключен ко второму знаковому входу блока запрета 3. Выход "Переполнение" блока запрета 3 является выходом вычислительного устройства. N-2 выходов сумматора 2 подключены к соответствующим N-2 входам блока преобразования результатов 4. Первый и второй запрещающие входы блока преобразования результатов 4 подключены к соответствующим запрещающим выходам блока запрета 3. N-2 группы установочных входов блока преобразования результатов подключены к соответствующим N-2-м группам установочных выходов кодоформирователя 5, k информационных выходов, где k=]log2(N-1)+l[, и выход "max" блока преобразования результатов 4 являются соответственно информационными k выходами и выходом "max" вычислительного устройства.

Блок управления 1, показанный на фиг. 2, предназначен для разрешения считывания информации и состоит из двухвходовых элементов "И" 1.11, 1.12,... , 1.12N, первый вход i-го элемента "И", где i=1, 2,..., 2N, является соответственно i-ым информационным входом блока управления, вторые входы всех элементов "И" соединены в параллель и являются входом "Разрешение" блока управления, выход i-го элемента "И" является i-ым выходом блока управления.

Сумматор 2, показанный на фиг. 3, предназначен для арифметических действий и состоит из N элементарных полных сумматоров 2.11, 2.12,..., 2.1N, первый и второй входы j-го, где j=1, 2, 3,..., N, элементарного полного сумматора являются соответственно (2j-1)-ым и 2j-ым входами сумматора, а выход u-го элементарного полного сумматора, где u=1, 2, 3,..., N-2, является u-м выходом сумматора, а выходы (N-1)-го и N-го элементарных полных сумматоров являются соответственно первым и вторым знаковыми выходами сумматора, причем вход переноса m-го элементарного полного сумматора, где m=1, 2, 3,... , N-1, подключен к выходу переноса m+1-го элементарного полного сумматора.

Блок преобразования результатов 4, показанный на фиг. 4, предназначен для представления результатов суммирования в соответствующем коде и состоит из N-2-x компараторов 4.11, 4.12,..., 4.1N-2, каждый из которых содержит первую группу из N-2-x входов и вторую группу из N-2-x входов, N-2-x двухвходовых элементов "И" 4.21, 4.22,..., 4.2N-2, N-2-x двухвходовых элементов "ИЛИ" 4.31, 4.32, ..., 4.3N-2, N-2-входовый шифратор 4. 4 и дополнительный двухвходовый элемент "ИЛИ" 4.5. Входы первой группы из N-2-x входов компараторов включены в параллель и являются соответствующими входами блока преобразования результатов 4, входы второй группы из N-2-x групп входов компараторов являются соответствующими установочными входами блока преобразования результатов 4, выход s-ого компаратора, где s=1,2,...,N-3, подключен к первому входу s-го двухвходового элемента "И", выход которого подключен к первому входу u-го двухвходового элемента "ИЛИ", где u=1, 2, 3,... N-2, выход которого является u-м входом шифратора, a k выходов, где k=]log2(N-1)+l[ шифратора являются соответствующими выходами блока преобразования результатов 4. Вторые входы N-2-x двухвходовых элементов "И" включены в параллель и являются первым запрещающим входом блока преобразования результатов. Вторые входы N-2-x двухвходовых элементов "ИЛИ" включены в параллель и являются вторым запрещающим входом блока преобразования результатов, причем первый выход (A>B) N-2-ro компаратора подключен к первому входу дополнительного двухвходового элемента "ИЛИ" 4.5 и является выходом "max" блока преобразования результатов. Второй выход (A=B) N-2-ro компаратора подключен ко второму входу дополнительного двухвходового элемента "ИЛИ" 4.5, выход которого подключен к первому входу N-2 двухвходового элемента "И".

Блок запрета 3, показанный на фиг. 5, предназначен для формирования команд на считывание и блокировку информации и состоит из двухвходового элемента "И-НЕ" 3. 1, двухвходового элемента "ИСКЛЮЧАЮЩЕЕ ИЛИ" 3. 2, первые входы элементов "И-НЕ" и "ИСКЛЮЧАЮЩЕЕ ИЛИ" подключены параллельно и являются вторым знаковым входом блока запрета, вторые входы элементов "И-НЕ" и "ИСКЛЮЧАЮЩЕЕ ИЛИ" подключены параллельно и являются первым знаковым входом блока запрета, выход элемента "И-НЕ" является выходом "Разрешение" и первым запрещающим выходом блока запрета, выход элемента "ИСКЛЮЧАЮЩЕЕ ИЛИ" является выходом "Переполнение" и вторым запрещающим выходом блока запрета.

Кодоформирователь 5, показанный на фиг. 6, предназначен для формирования кодов порога и состоит из N-2-x установочных блоков 5.1, 5.2,..., 5.N-2. Причем каждый из установочных блоков 5.u, где u=1,2,3,..., N-2, состоит из N-2-x резисторов 5.u. 11, 5.u1.2,..., 5.u1N-2, N-2-х коммутационных элементов 5. u.11, 5.u12,..., 5.u.1N-2 и источника питания, выход u-го коммутационного элемента, где u= 1,2,3,..., N-2, подключен к u-му установочному выходу кодоформирователя, а первый вход u-го коммутационного элемента подключен к первому выводу u-го резистора, второй - заземлен, причем вторые выводы всех резисторов подключены к положительной клемме источника питания, отрицательная клемма которого заземлена.

Входящие в общую структуру вычислительного устройства элементы являются типовыми и могут быть технически реализованы в настоящее время при использовании имеющейся элементной базы.

Компаратор двоичных чисел может быть реализован на интегральных микросхемах, описан: Б.В. Тарабрин, Л.Ф. Лунин, Ю. Н. Смирнов и др. Интегральные микросхемы. Справочник. - Издание второе, исправленное - М.: Энергоатомиздат, 1985, с. 285.

Двухвходовый элемент "И" может быть реализован на интегральных микросхемах, описан: Б. В. Тарабрин, Л.Ф. Лунин, Ю.Н. Смирнов и др. Интегральные микросхемы. Справочник. - Издание второе, исправленное - М.: Энергоатомиздат, 1985, с. 189.

Двухвходовый элемент "ИЛИ" может быть реализован на интегральных микросхемах, описан: Б.В. Тарабрин, Л.Ф. Лунин, Ю.Н. Смирнов и др. Интегральные микросхемы. Справочник. - Издание второе, исправленное - М.: Энергоатомиздат, 1985, с. 189.

Двухвходовую схему "И-НЕ" может быть реализован на интегральных микросхемах, описан: Б. В. Тарабрин, Л.Ф. Лунин, Ю.Н. Смирнов и др. Интегральные микросхемы. Справочник. - Издание второе, исправленное - М.: Энергоатомиздат, 1985, с. 189.

Двухвходовый элемент "ИСКЛЮЧАЮЩЕЕ ИЛИ" может быть реализован на интегральных микросхемах, описан: Б.В. Тарабрин, Л.Ф. Лунин, Ю.Н. Смирнов и др. Интегральные микросхемы. Справочник. - Издание второе, исправленное - М.: Энергоатомиздат, 1985, с. 199.

Шифратор с приоритетом кодируемого сигнала может быть реализован на интегральных микросхемах, описан: Б.В. Тарабрин, Л.Ф. Лунин, Ю.Н. Смирнов и др. Интегральные микросхемы. Справочник. - Издание второе, исправленное - М. : Энергоатомиздат, 1985, с. 194.

Резистор может быть реализован путем применения матрицы резисторов, описано: Б. В. Тарабрин, Л.Ф. Лунин, Ю.Н. Смирнов и др. Интегральные микросхемы. Справочник. - Издание второе, исправленное - М.: Энергоатомиздат, 1985, с. 190.

Сумматор может быть реализован на элементах И, ИЛИ, НЕ, описано: Справочник по цифровой вычислительной технике: (процессоры и память) /Б.М. Малиновский, Е. И. Брюхович и др. Под ред. Б.Н. Малиновского. - К.: Технiка, 1979. С. 180-191.

В качестве коммутационного элемента может быть использован любой двухпозиционный переключатель, например, показанный на фиг. 7.

Вычислительное устройство работает следующим образом. Два двоичных числа в модифицированном двоичном коде (см. описание в В.А. Семененко, А.В. Балтрушевич Электронно-вычислительные машины. М. : Высшая школа, 1985. С. 51) поступают на 2N входа блока управления 1 элементов "И" 1.11, 1.12,..., 1.12N. С выходов элементов "И" 1.11, 1.12,..., 1.12N поступают на входы A и B элементарных полных сумматоров 2, причем знаковые (2N-3)-й, (2N-2)-й, (2N-1)-й и 2N-Й разряды слагаемых подаются на входы элементарных полных сумматоров 2.1N-1 и 2.1N соответственно, разряды 1,2,..., 2N-4 слагаемых - на входы элементарных полных сумматоров 2.11, 2.12,..., 2.1N-2 соответственно.

В вычислительном устройстве осуществляется суммирование поступивших на вход чисел в соответствии с правилами двоичной математики (см. В.А. Семененко, А.В. Балтрушевич Электронно-вычислительные машины. М.: Высшая школа, 1985. С. 52-62). Вычисленное положительное значение суммы, при котором на знаковых выходах 1, 2 сумматора 2 имеются сигналы с уровнем логического "0", с выходов S1, S2, . .., S(N-2) сумматора 2 поступает на первую группу N-2 входов, включенных в параллель блока преобразование результатов 4, в котором вычисленное значение поступает на входы A1, A2,..., A(N-2) компараторов 4.11, 4.12,...,4,1N-2, на группы входов B1, B2,..., B(N-2), поступают пороговые коды с кодоформирователя 5, код которого формируется в соответствии с требуемой шкалой измерения, подачей сигналов логических "1" или "0", путем коммутации N-2-x групп установочных выходов кодоформирователя 5 на резистор или на заземление соответственно. В результате сравнения вычисленного в сумматоре 2 значения с пороговыми кодами на выходах A>B компараторов 4.11, 4.12,... 4.1N-2. 2 образуется кодовая комбинация, считываемая через элементы "И", 4.21, 4.22, . . .4.2N-2, "ИЛИ" 4.31, 4.32,...,4.3N-2 и дополнительный элемент "ИЛИ" 4.5 на входы X1, X2,..., X(N-2) шифратора с приоритетом кодируемого сигнала 4.4, на выходах Yl, Y2,..., Y(k) шифратора формируется выходной k-разрядный код. Выходной код формируется следующим образом:

если на входах X1, X2,..., X(N-2) шифратора с приоритетом кодируемого сигнала 4.4 появляется несколько сигналов высокого уровня, то приоритетом обладает сигнал высокого уровня, находящийся на входе со старшим номером. Это означает, что двоичный код на выходах Yl, Y2,..., Y(k) будет соответствовать этому сигналу высокого уровня, т.е. однозначно указывать на отрезок заданной пороговыми кодами положительной, дискретной, интервальной шкалы, которому принадлежит результат суммирования. При формировании на выходах S элементарных полных сумматоров 2.11, 2.12, ...,2.1N-2 кода, превышающего значение кода порога на компараторе 4.1N-2, на выходах A>B компараторов 4.11, 4.12,...,4.1N-1 появляется кодовая комбинация, содержащая "1" в каждом разряде, которая преобразуется шифратором с приоритетом кодируемого сигнала 4.4 в код, указывающий на максимальный отрезок заданной пороговыми кодами интервальной шкалы. Одновременно на выходе 1 компаратора 4.1N-1 и соответственно на выходе вычислительного устройства формируется сигнал "max", указывающий на превышение максимально допустимого значения. Пример формирования кодов порога, показан на фиг. 8, в логарифмическом масштабе с дополнительным масштабированием на 1000. Данный код устанавливается в блоке кодоформирователя 5.

При формировании на выходах S элементарных полных сумматоров 2.11, 2.12. ..., 2.1N-2 кода, соответствующего отрицательному числу, в знаковых разрядах Z1, Z2 появляются два сигнала с уровнем логической "1 ", которые поступают в блок запрета 3 и элемент "И-НЕ" 3.1 формирует сигнал с уровнем логического "0", запрещающий считывание информации с выходов А>В компараторов 4.11, 4.12,..., 4.1N-3 и элемента "ИЛИ" 4.5, на входы X1, X2,..., X(N-2) шифратора с приоритетом кодируемого сигнала 4.4, на выходах Y1,..., Y(k) которого формируется нулевая комбинация. Логический "0" с элемента "И-НЕ" 3.1 поступает на вход "Разрешения" блока управления 1 и запрещает считывание с информационных входов блока управления 1. На выходах 1, 2,..., 2N блока управления 1 формируются сигналы с уровнем логического "0", которые подаются на входы 1,2, ..., 2N сумматора 2, обнуляют его и на знаковых выходах 1,2 сумматора 2 появляются сигналы с уровнем логического "0", поступающие на знаковые входы 1, 2 блока запрета 3, на выходе элемента "И-НЕ" 3.1 формируется сигнал с уровнем логической "1", разрешающий работу вычислительного устройства.

Появление на знаковых выходах Z1, Z2 сумматора 2 комбинаций "01" или "10" указывает на то, что в сумматоре произошло переполнение. В этом случае на выходе элемента "ИСКЛЮЧАЮЩЕЕ ИЛИ" 3.2 появляется сигнал с уровнем логической "1", который формирует на выходах элементов "ИЛИ" 4.31, 4.32,..., 4.3N-2, кодовую комбинацию, состоящую из сигналов с уровнем "1" в каждом разряде, которая в шифраторе с приоритетом кодируемого сигнала 4.4 преобразовывается в код, указывающий на максимальный отрезок заданной пороговыми кодами интервальной шкалы. Одновременно на выходе вычислительного устройства с блока запрета 3 формируется сигнал "Переполнение", сигнализирующий о переполнении разрядной сетки.

Благодаря новой совокупности существенных признаков в заявленном устройстве, позволило расширить область применения вычислительного устройства с обеспечением функционального контроля его элементов. Возможно применение устройства в управляемой радиоэлектронной аппаратуре и системах с решающей обратной связью, где необходимо представление результатов вычисления в положительной, дискретной и интервальной, в том числе неравномерной, шкале представления, при обеспечении выполнения свойства самодиагностирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕГИСТР СДВИГА | 1998 |

|

RU2143140C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| ГЕНЕРАТОР БЕЛОГО ШУМА (ВАРИАНТЫ) | 1997 |

|

RU2120179C1 |

| ВЕКТОРНЫЙ ГЕНЕРАТОР | 1995 |

|

RU2100842C1 |

| ГЕНЕРАТОР РАВНОМЕРНО РАСПРЕДЕЛЕННЫХ СЛУЧАЙНЫХ ИМПУЛЬСОВ | 1996 |

|

RU2107941C1 |

| ГЕНЕРАТОР ФУНКЦИЙ УОЛША | 1996 |

|

RU2115951C1 |

| СПОСОБ И УСТРОЙСТВО ДИАГНОСТИКИ СОСТОЯНИЯ АППАРАТУРЫ ЦИФРОВЫХ СИСТЕМ ПЕРЕДАЧИ | 1998 |

|

RU2132594C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 1997 |

|

RU2121754C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении универсальных и специализированных управляющих устройств, а также вычислительных устройств. Технический результат изобретения заключается в разработке вычислительного устройства, обладающего более широкой областью применения за счет дополнительной обработки результатов арифметических действий и обеспечении функционального контроля элементов устройства. Вычислительное устройство содержит блок управления, сумматор, блок преобразования результатов, блок запрета, кодоформирователь. Возможно применение устройства в управляемой радиоэлектронной аппаратуре и системах с решающей обратной связью, где необходимо представление результатов вычисления в положительной, дискретной и интервальной, в том числе неравномерной, шкале представления, при обеспечении выполнения свойства самодиагностирования. 5 з.п. ф-лы, 8 ил.

| Вычислительное устройство | 1988 |

|

SU1517024A1 |

| JP 08212058 A, 20.08.96 | |||

| SU 1591005 A1, 07.09.90 | |||

| Устройство для алгебраического сложения | 1989 |

|

SU1603378A1 |

| Устройство для алгебраического вычитания | 1985 |

|

SU1297036A1 |

| Параллельный сумматор | 1986 |

|

SU1594523A1 |

| Сумматор-вычитатель | 1988 |

|

SU1536373A1 |

| US 5394349 A, 28.02.95 | |||

| US 5511018 A, 23.04.96 | |||

| JP 54048136 A, 22.09.97. | |||

Авторы

Даты

1999-06-20—Публикация

1998-02-18—Подача