Изобретение относится к вычислительной технике и автоматике и может быть использовано в арифметических устройствах электронных цифровых вычислительных машин и в цифровых измерительных приборах.

Цель изобретения - упрощение устройства.

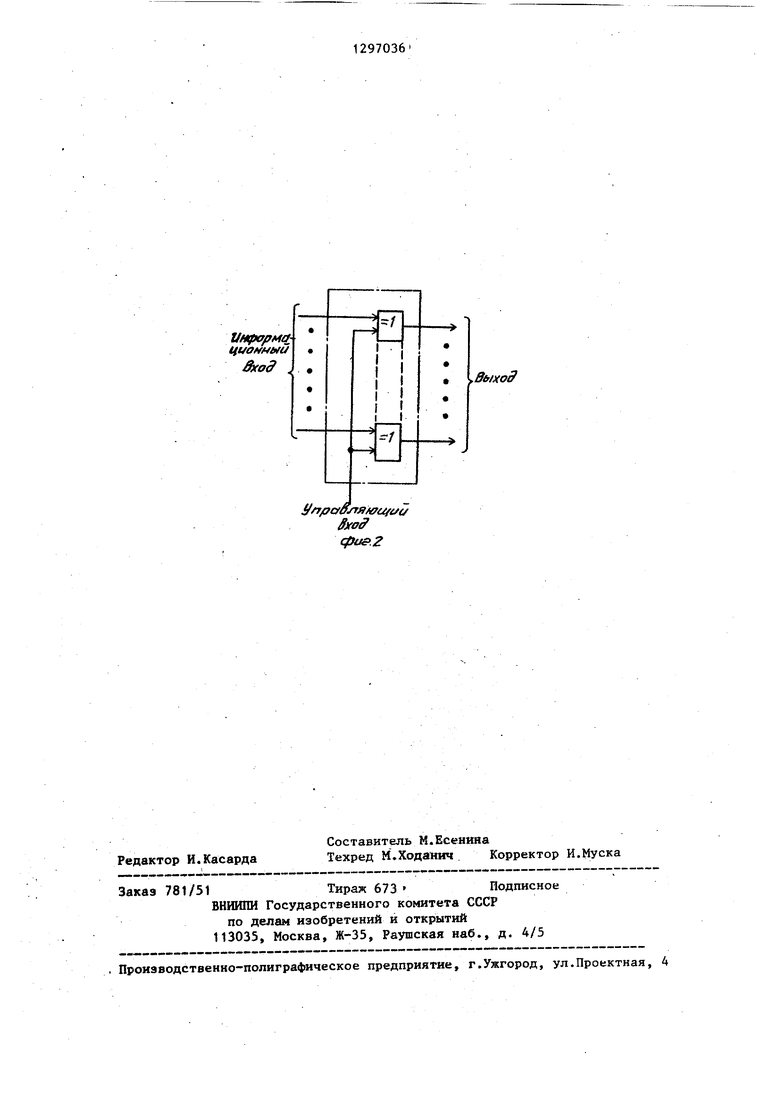

На фиг. 1 приведена структурная схема устройства для алгебраического вычитания ; на фиг. 2 - функциональная схема блока инвертирования.

Устройство для алгебраического вычитания содержит сумматор 1, входную шкну 2 первого операнда устройства, входной блок 3 инвертирования, входную шину 4 второго операнда, выходной блок 5 инвертирования, выход 6 результата устройства, первый и второй элементы И 7 и 8, выход 9 признака переполнения, первый, второй и третий элементы ИСКЛЮЧАЮЩЕЕ РШИ 10-12, первый элемент НЕ 13, шину 14 знакового разряда первого операнда, шину 15 знакового разряда второго операнда, выход 16 знака результата устройства и второй элемент НЕ 17,

Блок инвертирования может быть выполнен, например, на микросхеме 564 ЛП2.

Устройство для алгебраического вычитания работает следующим образом

При одинаковых знаках Зн. А и Зн.

8на зходах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

11 присутствуют одинаковые потенциалы, на выходе этого элемента - логический О, который поступает на второй вход элемента И 7. На выходе

9признака переполнения устройства при этом также присутствует логический О. Кроме того, логический О поступает на вход элемента НЕ 13. С его выхода логическая 1 поступает на управляющий вход входного блока

3 инвертирования. При этом на второй вход сумматора 1 поступает инверсный код второго операнда В. Если А В, то на выходе переноса сумматора 1 формируется логическая 1, которая проходит через элемент И 8 и поступает на вход переноса сумматора 1. На выходе сумматора 1 появляется прямой код разности операндов А и В. В это время на обоих входах элемента ИСКЛЮЧАЩЕЕ ИЛИ 10 присутствуют две логические 1 (с выхода элемента И 8 и с вьпсода элемента НЕ 13)

5

0

5

и на его выходе возникает логический О. Этот логический О поступает на управляющий вход выходного блока

5инвертирования, который пропускает прямой код разности операндов А и В на выходе 6 результата устройства. При наличии логической 1 на входе элемента НЕ 17 (с выхода элемента

И 8) на второй вход элемента ИСКЛЮЧАЩЕЕ ИЛИ 12 поступает логический О. Тогда потенциал, который присутствует на шине 15 знакового разряда второго операнда проходит на выход 16 знака, результата устройства, т.е. Зн. С Зн. В.

При А ВиЗн. А 3н. В

(+А) - (+В) -1-{А-В),

(-А) - (-В) -(А-Б).

При А В на выходе сумматора 1 появляется инверсньй код разности операндов А и В, а на выходе переноса сумматора 1 формируется сигнал логического О. Этот сигнал на выходе элемента И 8 устанавливает логический О, которьш поступает на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

10и формирует на его выходе логическую 1. Эта логическая 1 при поступлении на управляющий вход выходного блока 5 инвертирования вызывает инверсию выходного кода сумматора 1. В результате этого на выходе

6результата устройства присутствует прямой код разности операндов А и В.

5 Логический О с входа элемента НЕ, 17 инвертируется, и логическая 1 с выхода этого инвертора поступает на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12. В этом случае на выходе 16 знака результата, Зн. С устройства присутствует инверсия значения знакового разряда второго операнда на шине 15, т.е. Зн. С Зн. В.

При А В Зн. А - Зн. С

(+А) - (+В) -() -(В-А),

(-А) - (-В) +(А-В) +(В-А).

При различных знаках Зн. А и Зн. В на выходе элемента ИСКЛЮЧАКЯЦЕЕ ИЛИ

11формируется логическая 1, а на выходе элемента НЕ 13 - логический , который поступает на .управляющий вход входного блока 3 инвертирования. В этом случае на второй вход сумматора 1 поступает прямой код операнда

В, и на выходе сумматора 1 появляются код суммы операндов А и В и сигнал с выхода переноса сумматора 1,

0

0

5

0

5

который через элемент И 7 поступает на выход 9 признака переполнения.

Логический О с выхода элемента НЕ 13 запрещает прохождение сигнала с выхода переноса сумматора 1 через элемент И 8 и формирует на его выходе логический О. Наличие этого логического О и логического, О с выхода элемента НЕ 13 на входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 вызывает появление логического О на его выходе и управляющем входе выходного блока 5 инвертирования. В результате этого на выходе 6 результата устройства появляется прямой код суммы one рандов А и В.

При инвертировании логического О с выхода элемента И 8 на выходе

анды +В

-В -«-В -В

С при Зн. В (+А) - (В)

(+А) - (-В) (-А) - (+В) (-А) - (-В)

Формула

изобретения

Устройство для алгебраического вычитания, содержащее сумматор, два элемента НЕ, первый элемент ИСКЛЮ- ЧАКНЦЕЕ ШШ, два элемента И, причем первый информационный вход сумматора соединен с входом значащих разрядов первого операнда устройства, входы знаковых разрядов первого и второго операндов устройства соединены соот- ветственно с первым и вторым входами первого элемента ИСКЛЮЧАЩЕЕ ИЛИ, выход которого соединен с входом первого элемента НЕ и первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом первого элемента НЕ, отличающееся тем, 4TOj с целью упрощения устройства, в него введены два блока инвертирования, второй и третий элементы ИСКЛЮЧАЮЩЕЕ ШШ, причем вход значащих разрядов второго операнда устройства соединен с информационным входом первого блока инвертирования, вход раз- рещения инвертир|Ования которого соеэлемента НЕ 17 формируется логическая 1, которая поступает на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 При этом на вьгходе 16 знака результата устройства фиксируется инверсия значения знакового разряда Зн. В на шине 15, т.е. Зн. С Зн. В.

При Зн. А + Зн. Б

(+А) - (-В) +(А+В),

(-А) - (+В) -(А+В).

При подаче на шину 15 инверсного значения знакового разряда Зн. В второго операнда второй вариант устройства выполняет операцию сложения двух чисел с различными знаками, что подтверждается следующими преобразованиями.

С при Зн. В

(+А)-(-В) (+А)+(+В)

(+А)-(+В) (+А)-(-В)

(-А)-(-В) (-А) + (ч-В)

(-А)-(-В) (-А)+(-В)

динен с выходом первого элемента НЕ, выход первого блока инвертирования соединен с вторым информационным входом сумматора, выход суммы которого соединен с информационным входом второго блока инвертирования, выход которого соединен с выходом значащих разрядов результата устройства, а ыход переноса сумматора соединен с вторым входом первого элемента И, выход которого соединен с выходом переполнения устройства, выход второго элемента И соединен с входом переноса сумматора, входом второго элемента НЕ и первым входом второго элемента ИСКЛЮЧАЩЕЕ ИЛИ, второй вход которого соединен с выходом первого элемента НЕ, вход разрешения инвертирования второго, блока инвертирования соединен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ШШ, вход знакового разряда второго операнда устройства соединен с первым входом третьего элемента ИСКЛЮЧАЩЕЕ ИЛИ, второй вход которого соединен с выходом второго элемента НЕ, выход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом знака результата устройства.

ционный

off

.ff /xoff

yfrffcfOfr /ffUfui/ S)foff

фа.2

Редактор И.Касарда

Составитель М.Есенина

Техред М.Ходанич Корректор И.Myска

Заказ 781/51Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для алгебраического сложения | 1985 |

|

SU1297035A1 |

| Вычислительное устройство | 1988 |

|

SU1517024A1 |

| Устройство для сложения и вычитания | 1978 |

|

SU842798A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1985 |

|

SU1259249A1 |

| Устройство для сложения и вычитания | 1980 |

|

SU922730A1 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| УСТРОЙСТВО для СУММИРОВАНИЯ | 1973 |

|

SU393740A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU451078A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в арифметических устройствах электронных цифровых вычислительных машин| и в цифровых измерительных приборах. Цель изобретения - упрощение устройства. Устройство для алгебраического вычитания содержит сумматор 1, два блока.3 и 5 инвертирования, два элемента 7.и 8, три элемента ИСКЛЮЧМЩЕЕ ИЛИ 10- 12, элемент НЕ 13. 2 ил. -об сл с в тг J6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , Авторское свидетельство С6СР ;№ 913368, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-29—Подача