1

По

(Л

Изобретение относится к вычислительной техШ1ке и может-быть использовано при реализации арифметических устройств в электронных цифровых вычисли тельных машинах и цифровых измерительных приборах.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечеш1я допол- нительно к операции алгебраического суммирования операции алгебраического вычитания.

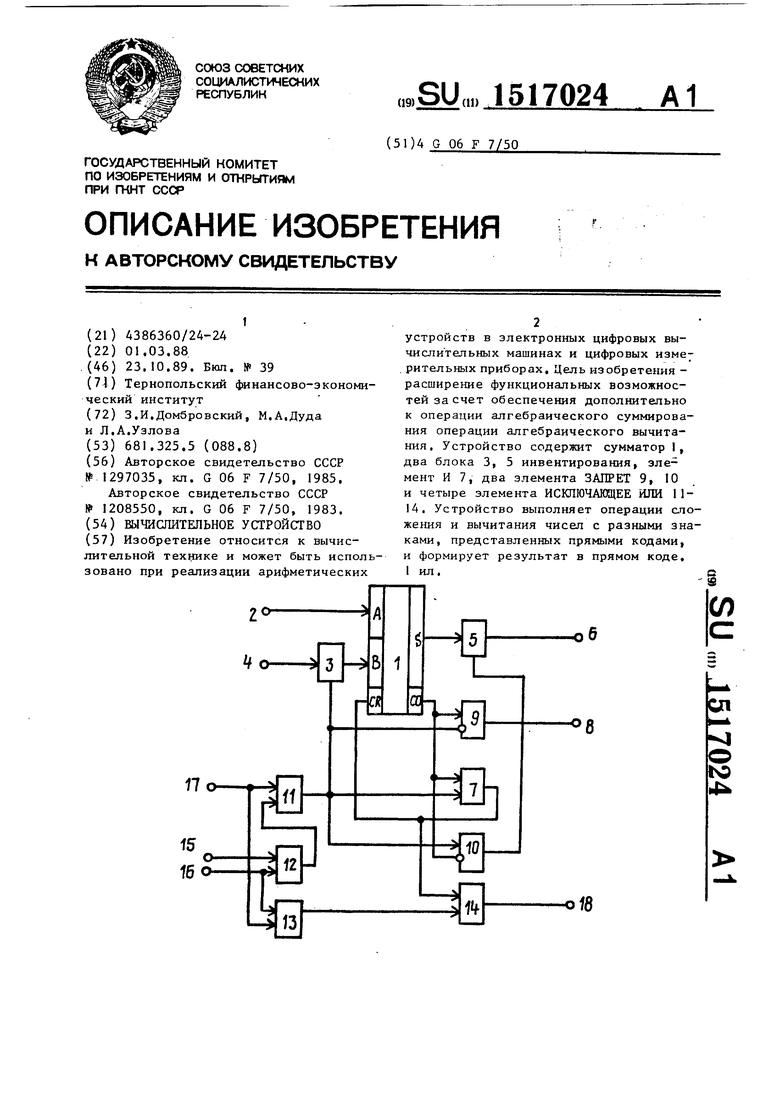

На чертеже представлена блок-схема вычислительного -устройства.

Устройство содержит сумматор 1, вход 2 первого операнда, блок 3 инвертирования, вход 4 второго операнда, блок 5 инвертирования, выход 6 результата, элемент И 7, выход 8 приз нака переполнения, элементы ЗАШ ЕТ 9 и 10, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11-14, вход 15 знака первого операвда вход 16 знака второго операнда, вход 17 управлеш1я режимом и выход 18 зпа- ка результата.

Устройство работает следующим образом ,

Код первого операнда А по входу 2 поступает на первый вход суммато- ра 1. Код второго операнда В поступает по входу 4 на информационный вход блока 3 пнвертирования, Знаки (Зн, А и Зн, З)операндов по входам 15 и 16 соответственно поступают на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12. При этом, если на выходе 17 есть нулевой сигнал то устройство выполняет операцию алгебраического сложения, а если на входе 17 есть единичный сигнал, то уст- ройство выполняет операцию алгебраиче чого БЬ :Чита1шя ,

Пусть на входе 17 присутствует ну- сигнал, означающий, что устройство выполняет операцию алгебраическо го сложетш. При одинаковых Зн.А и Зл, j па входах элемента ИСКЛЮЧАЮЩЕЕ ИЛ.И 12 о; ноБременно присутствуют два логнчсск 1х О (что соответствует пол Ж1П ег1ь;;ь м знакам) или две логические 1 (что соответствует отрицательным знакам), В этом случае на выходе элемента ИCKЛЮЧ :OЩEE А-ШИ 12 присутствует логической о, который поступает на псрБглй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

11, на втором входе которого также логический О с входа 17. Следовательно, ,а пыходе элемента ИСКЛ10ЧАЮ111ЕЕ ИЛИ 11 - логический О, который поступает

j

о 5

п Q

-

5

5

на управляющий вход блока 3 инвертиро - вания, Поэтому код второго операнда не инвертируется. Логический О с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 поступает также на вход элемента И 7, на выходе которого формируется логический О. С выхода элемента И 7 логический О поступает на вход переноса сумматора .1 и на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14. При этом на выходе 18 Зн.С результата устройства повторяет значение на входе 16 Зн.В, так как на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 поступают соответственно логической О с входа 17 и логический О или логическая 1 с входа 16 Зн.В. Следовательно, Зн..В.

Логический О с выхода элемента ИСКЛЮЧАЮЩЕЕ или ll поступает на инверсный вход элемента ЗАПРЕТ 9 и разрешает прохождение сигнала с выхода нереноса сумматора 1 на выход 8. В этом случае выход 8 может быть использован для отображения (п+1)-гО разряда при суммировании п-разрядных двоичных чисел, что исключает вьщачу неправильного результата при сложении.

Кроме этого, логический О с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 1I поступает на прямой вход элемента ЗАПРЕТ 10, вследствие чего на его выходе формируется логический О, который поступает на управляющий вход блока 5 инвертирования и запрещает инвертирование результата суммиро вания,

Таким образом, в случае выполнения операции алгебраического суммировання при совпадении знаков слагаемых код результата С представляет собой сумму прямых кодов операндов к и В. Значение на выходе 18 повторяет значение на выходе 16,

При Зн..В

(+А) + (+В) + (А+В);

(-А) + (-В) - (А+В).

При разных Зн.А и Зн.В на входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 присутствуют противоположные сигналы, что вызывает появле1те на его выходе логической 1. Эта логическая 1 поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11, на втором входе которого есть логический О с входа 17. При этом на выходе элемента ИСКЛЮЧАЩЕЕ ИЛИ 11 формируется логическая 1, которая поступает на управляющий вход блока 3 инвертирования. Поэтому на второй вход сумматора 1 поступает инвертированный код операнда В, Если , то на выходе переноса сумматора 1 формируется сигнал в виде логической 1, Этот сигнал поступает на первый вход элемента И 7, прямой вход элемента ЗАПРЕТ 9 и инверсный вход элемента ЗАПРЕТ 10, При этом логическая I, которая поступает на инверсный вход элемента ЗАПРЕТ 9 с выхода элемента ИСКЛЮЧАЮЩЕЕ Ш1И 11, запрещает прохождение сигнала на выход 8 признака переполнения. В это же время на второй вход элемента И 7 поступает логическая 1 с выхода элемента ИСКЛЮЧАЮЩЕЕ ШШ 11, которая разрешает прохождение логической 1 на выход элемента И 7 и далее на вход переноса сумматора I, Таким образом, на первый вход сумматора 1 поступает прямой код операнда А, на второй вход - инверсный код операнда В.

на вход переноса - логическая 1. На выходе сумматора 1 формируется разность операндов А и В в прямом коде. Присутствие логической I на инверсном входе элемента ЗАПРЕТ 10 вызывает пояление логического О на его выходе, который поступает на управляющий вход блока 5 инвертирования ,зо Зн,.В есть Зн,.В и В этом случае прямой код разности one- (-А) +(-ьВ) - (А-5) + (З-А

мируется инверсный код разности о рандов А и В,

Логический О с выхода перено сумматора 1 поступает на первый в элемента И 7, прямой вход элемент ЗАПРЕТ 9 и инверсный вход элемент ПРЕТ 10. В резулвтате этого на вы де 8 будет логический О, а на вы

Q де элемента И 7, а следовательно, на входе переноса сумматора 1 та будет логический О. При наличии гической 1 с выхода элемента ИС ЧАЮЩЕЕ ИЛИ I 1 на прямом входе элемент

)5 ПРЕТ 10 на его выходе формируется ло кая 1, которая поступает на упра ляющий вход блока 5 инвертирования При этом инверсный код разности о рандов инвертируется блоком 5 инв

20 тирования и на выходе 6 появляется прямой код разности операндов.

Присутствие логического О на первом входе элемента ИСКЛЮЧАЮЩЕЕ 14 вызывает повторение сигнала с

25 хода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13, торый повторяет сигнал с выхода 1 так как на первом его входе прису ствует логический О с входа 17. Таким образом, при 1А I IBI и

о Зн,.В есть Зн,.В и (-А) +(-ьВ) - (А-5) + (З-А

мируется инверсный код разности операндов А и В,

Логический О с выхода переноса сумматора 1 поступает на первый вход элемента И 7, прямой вход элемента ЗАПРЕТ 9 и инверсный вход элемента ЗАПРЕТ 10. В резулвтате этого на выходе 8 будет логический О, а на выхоQ де элемента И 7, а следовательно, и на входе переноса сумматора 1 также будет логический О. При наличии логической 1 с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ I 1 на прямом входе элемента ЗА5 ПРЕТ 10 на его выходе формируется логическая 1, которая поступает на управляющий вход блока 5 инвертирования. При этом инверсный код разности операндов инвертируется блоком 5 инвер0 тирования и на выходе 6 появляется прямой код разности операндов.

Присутствие логического О на первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 вызывает повторение сигнала с вы5 хода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13, который повторяет сигнал с выхода 16, так как на первом его входе присутствует логический О с входа 17. Таким образом, при 1А I IBI и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для алгебраического сложения | 1985 |

|

SU1297035A1 |

| Устройство для алгебраического вычитания | 1985 |

|

SU1297036A1 |

| УСТРОЙСТВО для СУММИРОВАНИЯ | 1973 |

|

SU393740A1 |

| Арифметико-логическое устройство | 1978 |

|

SU922727A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЙ | 1992 |

|

RU2042186C1 |

| Двоично-десятичный сумматор | 1981 |

|

SU1019441A1 |

| Устройство для суммирования двоичных чисел | 1985 |

|

SU1264164A1 |

| Устройство для вычитания | 1985 |

|

SU1277097A1 |

| Устройство для вычисления разности двух чисел | 1987 |

|

SU1444753A1 |

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

Изобретение относится к вычислительной технике и может быть использовано при реализации арифметических устройств в электронных цифровых вычислительных машинах и цифровых измерительных приборах. Цель изобретения - расширение функциональных возможностей за счет обеспечения дополнительно к операции алгебраического суммирования операции алгебраического вычитания. Устройство содержит сумматор 1, два блока 3, 5 инвертирования, элемент И 7, два элемента ЗАПРЕТ 9, 10 и четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11-14. Устройство выполняет операции сложения и вычитания чисел с разными знаками, представленных прямыми кодами, и формирует результат в прямом коде. 1 ил.

рандов А и В поступает с выхода сумматора 1 на выход 6 результата устройства ,

Знак результата устройства определяется состоянием сигналов на входах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 14 .и 13 На первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 с выхода элемента И 7 поступает логическая 1, На второй вход этого элемента поступает сигнал с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13, который повторяет сигнал на входе 16, так как на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 присутствует логический О с выхода 17, Присутствие логической 1 на первом входе элемента ИСКШОЧАЮЩЕЕ ИЛИ 14 выэывает инверсию сигнала с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13. Таким образом, на выходе 18 формируется инверсия сигнала с входа 16.

При одинаковых Зн,Л м Зн,В на вхо дах элемента ИСКШОЧАЮЩЕЕ ЯГО 12 присутствуют одновременно два логических О или две логические 1. На выходе элемента ИСКЛЮЧАЮЩЕЕ ;ШИ 12 - логичес кий О, который поступает на первый вход элемента ИСКЛЮЧАИДЕЕ ИЛИ 1 1 , на втором входе которого есть логическая 1 с входа 17 устройстиа. Тогда на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 - логическая 1, которая поступает на управляющий вход блока 3 инвертирования, вследствие чего код второго операнда В инвертируется. Логическая 1 с выхода элемента ИСКЛЮЧАЮЩЕЕ И.ЛИ 1 1 поступает на инверсный вход элемента , ЗАПРЕТ 9, поэтому на выходе 8 - логн55

Следовательно, при |А 1 1В I и Зн.А УЗн.В

(-А) -I- ( В) - (А-в) ;

( А) (-В) - (А-В) . Если |А I 1В|, то на выходе перено- мент И 7 и поступает на вход переноса са сумматора 1 присутствует логический О, а на выходе сумматора 1 форческий О. Если lAl 5|В1, то на вы- ходеЪереноса сумматора 1 форм-ируется ло гическая 1, которая проходит через эле

сумматора 1. При этом на выходе сумма тора 1 будет прямой код разногти one

(+А) + (-В) + (А-3) - (В-А), Пусть на входе 17 присутствует единичный сигнал, означающий, что устройство выполняет операцию алгебраического вычитания,

При одинаковых Зн,Л м Зн,В на входах элемента ИСКШОЧАЮЩЕЕ ЯГО 12 присутствуют одновременно два логических О или две логические 1. На выходе элемента ИСКЛЮЧАЮЩЕЕ ;ШИ 12 - логический О, который поступает на первый вход элемента ИСКЛЮЧАИДЕЕ ИЛИ 1 1 , на втором входе которого есть логическая 1 с входа 17 устройстиа. Тогда на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 - логическая 1, которая поступает на управляющий вход блока 3 инвертирования, вследствие чего код второго операнда В инвертируется. Логическая 1 с выхода элемента ИСКЛЮЧАЮЩЕЕ И.ЛИ 1 1 поступает на инверсный вход элемента , ЗАПРЕТ 9, поэтому на выходе 8 - логн

55

- мент И 7 и поступает на вход переноса

ческий О. Если lAl 5|В1, то на вы- ходеЪереноса сумматора 1 форм-ируется логическая 1, которая проходит через элеент И 7 и поступает на вход переноса

сумматора 1. При этом на выходе сумматора 1 будет прямой код разногти oneран}т,ов А и В, В это же время на инверсном входе элемента ЗАПРЕТ 10 присутствует логическая 1 с выхода переноса сумматора 1, вследствие чего на его выходе будет логический О, Этот ло- гический О поступает на управляющий вход блока 5 инвертирования, который обеспечивает прямой код разности операндов А и В на выходе 6, Знак резуль-,,. тата устройства при этом определяется состоянием сигналов на входах элемент тов ИСКПЮ ШОЩЕЕ Ш1И 14 и 13. На первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 поступает логическая 1 с выхода элеменр та И 7, а на второй вход поступает сиг-. нап 13,

с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ т.е. инверсия значе1П1Я За,В, так

как на первом входе элемента ИСКИЮЧА- ИЛИ 13 присутствует логическая 1 с входа 17, Присутствие логичес- KOii I на первом входе элемента ИС- iiJi 0 -L iOUlEE lUlli 14 вызывает инверсию сиг- iinjia с выхода элемента ИСКЛЮЧАЮЩЕЕ ;ПИ 13, т.е. Зн..В.

Поэтому при I А I I 3 I и Зн.А Зн.В

-(+В) + (А-В);

-(-В) - - (А-В).

/ . I 13 на выходе сумматора ;я инверсный код разности one А и В, а на выходе переноса сумформируется сигнал логическо Этот сигнал поступает на пер- j;ai вход элемента И 7 и инверсный вхо элг-мента ЗАПРЕТ 10, На прямом входе элемента ЗАШ ЕТ 10 присутствует логи чосч ая 1 с выхода элемента ИСЮ1ЮЧА- . ;Uin 11, Б результате на В1.ходе I lCMCHTa ЗАП1 ЕТ 10 формируется логиче к.1 1, которая при поступлении на ули.ч вляющий вход блока 5 инвертирует Л:::-:од::ой код сумматора , В результа- ;-е на нмходе 6 будет прямой код раз- операндов ч и В, Логический О с uLixii;ja элемента tl 7 по I l. ii ;jxo;i элемента

iia jjiopoM входе которого присутствует ....-т.-г- ргное значение Зн. В, поступающе- - п.. 16. В этом случае на выхо- ;;.- 18 - инверсное значе1П1е знака вто- Р-ПЧ) О17еранда, поступающего на вход b, т.е. Зн,,В, Следовательно, при л I V Г: I и Зн., В,

(+А) .- (+В) - (А) - (В-А);

(-Л) - (-В) + (А-В) (В-А).

гунает на пе ИСКЛЮЧА10ЩЕЕ ШИ 14,

При различных Зн.А и Зн.В на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 фор- t--:ipye-i c логическая 1, на выходе лемеита ИС:;Ш;ОЧ.10ЩЕЕ ИЛИ 1 1 - логический , который поступает на управляющий вход блока 3 инвертирования В этом случае на второй вход сумматора 1 поступает прямой код операнда В и на выходе сумматора I будет код суммы операндов А и В и сигнал с выхода переноса сумматора I, При этом на инверсном входе элемента ЗАПРЕТ 9 есть логический О, который разрешает прохождение сигнала с выхода переноса сумматора 1 на выход 8, Вместе с тем логический О с выхода элемента ИС- КЛЮЧАЩЕЕ ИЛИ 1 1 запрещает прохождение сигнала с выхода переноса сумматора 1 через элемент И 7 и формирует на его выходе логической О, который

поступает на вход переноса сумматора 1 и на первый вход элемента ЯС1ШЮЧАЩЕЕ ИШ- 14.

Наличие логического О на прямом входе элемента ЗАПРЕТ 10 с выхода элемента ИС1ШЮЧА10ЩЕЕ ИЛИ 1 1 вызывает наличие логического О на его выходе и управляющем входе блока 5 инвертирования, В результате этого на выходе 6 будет прямой код суммы операндов А и В. Наличие логическогб О на первом входе элемента ИСКЛЮЧАЩЕЕ ИЛИ 14 повторяет на его выходе сигнал, присутствующий на втором его входе, т.е. инверсное значение знака второго операнда на входе 16, так как Зн.С Зн,В, Поэтому при Зн.,В

35

-

0

-

0

5

(+А) - (-В) + (А+В)}

(-А) - (+В) - (А+В).

При подаче на вход 16 инверсного значения Зн.В второго операнп,а это устройство вьнюлняет операцию вычитания чисел с различными знаками в случае подачи на вход 17 логического О и операдию сложения чисел с различными знаками в случае подачи на вход , 17 логической 1 ,

Формула изобретения

Вычислительное устройство, содержащее сумматор, два блока инвертирования, элемент И, первый, второй элементы ЗАПРЕТ, первый и второй элементы ИСКЛЮЧАЩЕЕ Лт, причем первый информационный вход сумматора соединен с входом первого операнда устройства, второй информационный вход сумматора соединен с выход()м первого блока инвертирования, информационный вход которого подключен к входу второго операнда устрс йстил, пг рвый и

второй входы первого элемента ИСКЛЮЧАЮЩЕЕ 41ПИ соединены соответственно с входами знаков первого и второго операндов устройства, выход суммы суматора соединен с информационным входом второго блока инвертирования, выход которого соединен с выходом результата устройства, выход переноса сумматора соединен с первым входом элемента И, с прямым входом первого элемента ЗАПРЕТ и с инверсным входом второго элемента ЗАПРЕТ, выход первого элемента ЗАПРЕТ соединен с выходом признака переполнения устройства, выход элемента И подключен к входу переноса сумматора, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом знака результата устройства, выход второго элемента ЗАПРЕТ соединен с управляющим входом второго блока инвертирования, управляющий вход первого блока инвертирования соединен с инверсным входом первого элемента ЗАПРЕТ, вторым входом элемента И и прямым входом второго элемента ЗАПРЕТ, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения дополнительно к операции алгебраического суммирования операции алгебраического вычитания, в него введены третий

0 и четвертый элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых соединены с входом управления режимом устройства, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом третье5 го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом элемента И, выход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ШШ, второй вход которого

0 соединен с выходом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с вторым входом первого элемента ИСКЛЮЧАЮЦЕЕ ИЛИ.

| Устройство для алгебраического сложения | 1985 |

|

SU1297035A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Двоично-десятичный сумматор | 1983 |

|

SU1208550A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-23—Публикация

1988-03-01—Подача