Изобретение относится к компьютерной технике и может использоваться для контроля целостности данных в системах защиты информации.

Известен многоканальный сигнатурный анализатор, содержащий регистры, блоки сложения, умножения и деления в поле GF(L) (А.с. СССР N 1185338, БИ, N 38, 1985 г. ). Данное устройство предназначено для формирования сигнатур параллельного потока данных. Принцип работы устройства основан на делении многочлена входных последовательностей на характеристический многочлен, примитивный над полем GF(L).

Устройство эффективно при обнаружении случайных искажений во входных анализируемых последовательностях. Однако простота процедуры определения информационной последовательности, имеющей заданную сигнатуру, обуславливает низкую достоверность устройства при обнаружении умышленных искажений информации.

Наиболее близким по технической сущности к предлагаемому устройству является многоканальный сигнатурный анализатор, содержащий блок управления, предназначенный для формирования окна измерений, и формирователь сигнатур, принцип работы которого основан на алгоритме деления многочленов. Тактовый вход блока управления образует одноименный вход анализатора. Тактовый вход формирователя сигнатур подключен к первому выходу блока управления. Группа информационных выходов формирователя сигнатур образует группу одноименных выходов анализатора, которая подключается к входам блока индикации (Сигнатурный анализ в задачах контроля и диагностики цифровых устройств. - М.: МИФИ, 1986, с. 21, рис. 12).

Данное устройство предназначено для формирования сигнатур параллельного потока данных. Устройство эффективно при обнаружении случайных искажений во входных анализируемых последовательностях. Однако простота процедуры определения информационной последовательности, имеющей заданную сигнатуру, обуславливает низкую достоверность устройства при обнаружении умышленных искажений информации.

Для повышения достоверности контроля при обнаружении умышленных искажений информации предлагается в многоканальный сигнатурный анализатор, содержащий формирователь сигнатур, блок управления, причем тактовый вход блока управления образует одноименный вход устройства, тактовый вход формирователя сигнатур подключен к первому выходу блока управления, группа информационных выходов формирователя сигнатур образует группу одноименных выходов устройства, дополнительно ввести два блока преобразования, причем группа информационных входов первого блока преобразования образует группу одноименных входов устройства, группа информационных выходов первого блока преобразования соединена с группой одноименных входов второго блока преобразования, группа одноименных выходов которого соединена с группой одноименных входов формирователя сигнатур, первая и вторая группы входов режима устройства подключены к первой и второй группам информационных входов блока управления соответственно, третья и четвертая группы входов режима устройства подключены к группам одноименных входов первого и второго блоков преобразования соответственно, второй, третий, четвертый и пятый выходы блока управления соединены соответственно с тактовыми входами первого и второго блоков преобразования, со входами режима первого и второго блоков преобразования, шестой выход блока управления является выходом сигнала готовности устройства.

Блоки преобразования и соответствующие связи вводятся в состав устройства для обеспечения дополнительного этапа преобразования информационной последовательности перед формированием сигнатуры. Суть алгоритма преобразования заключается в разбиении входной информационной последовательности на блоки и шифровании каждого слова и каждого блока. В отличие от стандартных алгоритмов шифрования методом замены для отдельных слов и блочных алгоритмов шифрования в предлагаемом устройстве результат преобразования (шифрования) слова (или блока слов) зависит не только от кода слова (или блока), но и от его позиции в преобразуемой последовательности слов (или блоков). В результате максимально усложняется процедура поиска информационной последовательности, имеющей заданную сигнатуру, а значит увеличивается достоверность контроля целостности информации.

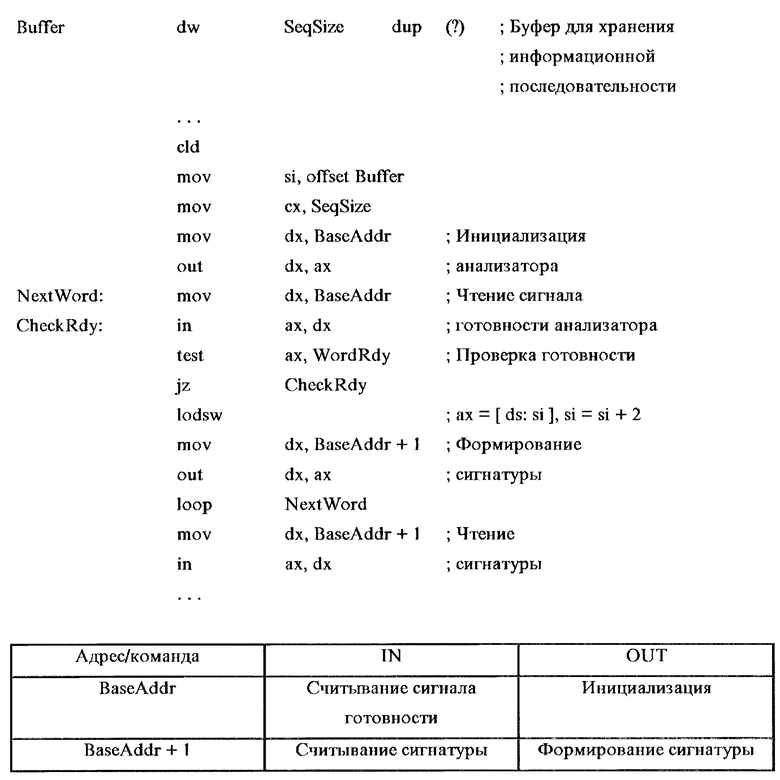

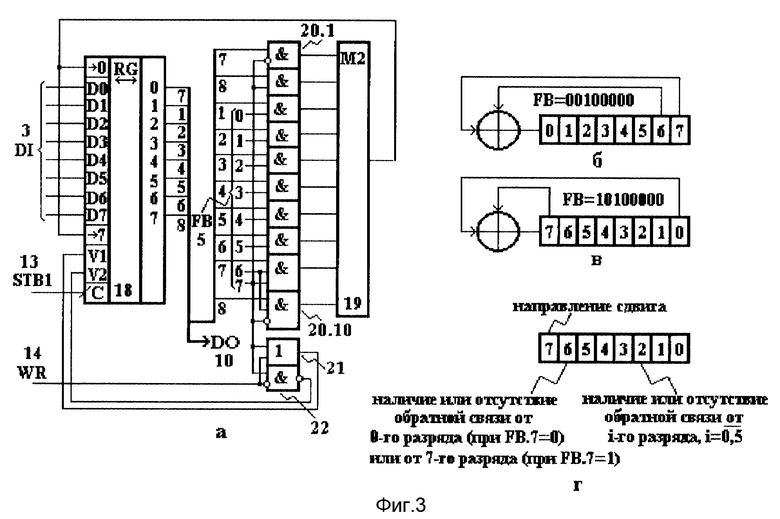

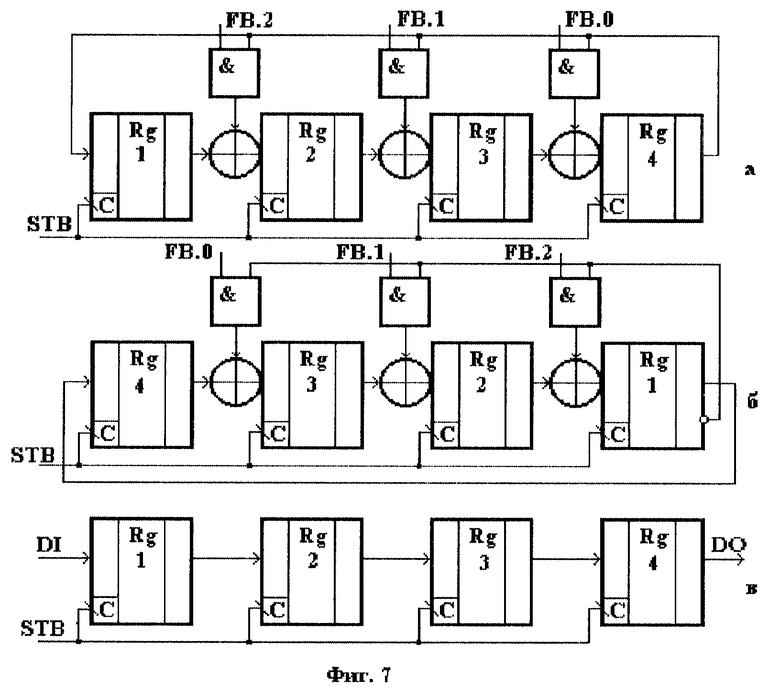

На фиг. 1 представлена схема многоканального сигнатурного анализатора; на фиг. 2 приведена временная диаграмма выходных сигналов блока управления; на фиг. 3 - пример построения первого блока преобразования и его эквивалентные схемы на различных этапах функционирования устройства; на фиг. 4 - схема блока управления; на фиг. 5 - пример построения второго блока преобразования; на фиг. 6 - временная диаграмма работы устройства; на фиг. 7 - эквивалентные схемы второго блока преобразования на различных этапах работы устройства.

Многоканальный сигнатурный анализатор (МСА) (фиг. 1) имеет первую 1 и вторую 2 группы входов режима, группу 3 информационных входов, тактовый 4 вход, третью 5 и четвертую 6 группы входов режима, группу 7 информационных выходов, выход 6 сигнала готовности устройства. В состав МСА входят первый 9 и второй 10 блоки преобразования, формирователь 11 сигнатур и блок 12 управления. На фиг. 1 также показаны тактовый 13 вход блока 9, вход 14 режима работы блока 9 (WR/CRIPTO_W), тактовый 15 вход блока 10, вход 16 режима работы блока 10 (WR/CRIPTO_B), тактовый 17 вход формирователя 11 сигнатур (импульсы считывания блока и формирования сигнатуры блока). Тактовый вход блока управления образует одноименный вход устройства, тактовый вход формирователя сигнатур подключен к первому выходу блока управления, группа информационных выходов формирователя сигнатур образует группу одноименных выходов устройства, группа информационных входов первого блока преобразования образует группу одноименных входов устройства, группа информационных выходов первого блока преобразования соединена с группой одноименных входов второго блока преобразования, группа одноименных выходов которого соединена с группой одноименных входов формирователя сигнатур, первая и вторая группы входов режима устройства подключены к первой и второй группам информационных входов блока управления соответственно, третья и четвертая группы входов режима устройства подключены к группам одноименных входов первого и второго блоков преобразования соответственно, второй, третий, четвертый и пятый выходы блока управления соединены соответственно с тактовыми входами первого и второго блоков преобразования, со входами режима первого и второго блоков преобразования, шестой выход блока управления является выходом сигнала готовности устройства.

На фиг. 3 показан пример построения блока 9 преобразования для случая, когда разрядность входного слова равна 8 (байт). В состав блока 9 входят регистр 18 сдвига, разрядность которого равна разрядности m входного слова, сумматор 19 по модулю два, группа из (m+2) элементов 20 И, элемент 21 ИЛИ и элемент 22 И.

На фиг. 4 показана схема блока 12 управления, в состав которого входят первый 23 и второй 24 элементы И, первый 25 элемент ИЛИ, третий 26 элемент И, мультиплексор 27, второй 28 и третий 29 элементы ИЛИ, триггер 30, элемент 31 И-НЕ, четвертый 32 и пятый 33 элементы И, генератор 34 импульсов, первый распределитель импульсов на триггерах 35-37, четвертый 38 элемент ИЛИ, шестой 39 элемент И, пятый 40 элемент ИЛИ, первый 41 счетчик по модулю N, дешифратор 42, седьмой 43, восьмой 44 и девятый 45 элементы И, шестой 46 элемент ИЛИ, второй распределитель импульсов на триггерах 47-49, элемент 50 ИЛИ и второй 51 счетчик.

На фиг. 5 показан пример построения второго 10 блока преобразования для случая N = 4. Блок 10 содержит N регистров 52 разрядностью m, N мультиплексоров 53, первую 54 группу из N сумматоров, вторую 55 группу из N - 1 сумматоров, первый 56 и второй 57 элементы И, элемент 58 ИЛИ, первую 59 группу из N - 1 элементов И, вторую 60 группу из N - 1 элементов И.

На фиг. 7 показаны эквивалентные схемы блока 10 на этапе преобразования при FB. 3 = 1 (фиг. 7,а) и FB.3 = 0 (фиг. 7,6), где FB.3 - старший разряд вектора обратных связей, который определяет направление сдвига информации; и на этапах записи (чтения) в блок 10 (чтения из блока 10) (фиг. 7,в).

Устройство работает следующим образом. Перед началом работы формирователь 11 сигнатур, счетчик 41, триггеры 36, 37, 47 устанавливается в нулевое состояние, триггеры 30 и 35 устанавливаются в единичное состояние. Цепи установки в исходное состояние не показаны. После инициализации МСА на входы 3 DI (Data Input) начинают поступать слова контролируемой информационной последовательности, сопровождаемые тактовыми импульсами 4 STB (Strobe). Поступление очередного слова в МСА разрешено только при наличии на выходе 8 сигнала готовности устройства RDY (Ready). Сигнал RDY = 0, когда устройство функционирует на этапах преобразования слова или блока слов. После записи очередного слова в блок 9 начинается этап преобразования (шифрования) этого слова. Блок 9 представляет собой генератор кодов, функционирующий в поле GF(2) (фиг. 3), направление сдвига (определяемое старшим разрядом кода 5), вектор обратных связей (определяемый младшими разрядами кода 5) и число nwi тактов работы преобразования (определяемое кодом 1) меняется по псевдослучайному закону (который определяют генератор псевдослучайных кодов, формирующий коды 1, 5 для блока 9) от слова к слову. После выполнения nwi тактов преобразования над N словами, где i = 1,N,N - размер блока слов, сформированный массив из N слов оказывается в блоке 10, после этого начинается этап его преобразования. Блок 10 представляет собой генератор кодов, функционирующий либо в режиме mN-генератора (фиг. 5) (m - разрядность слова), либо в поле GF(L), например GF(2m), направление сдвига (определяемое старшим разрядом кода 6), вектор обратных связей (определяемый младшими разрядами кода 6) и число nbi тактов работы преобразования (определяемое кодом 2) меняется по псевдослучайному закону (который определяет генератор псевдослучайных кодов, формирующий коды 2, 6 для блока 10) от блока к блоку. После выполнения nbi тактов преобразования сформированный массив из N слов поступает на входы формирователя 11 сигнатур (этап формирования сигнатуры блока из N слов). После поступления на входы устройства всей информационной последовательности в блоке 11 будет получена сигнатура, которая может быть считана с выходов 7.

На основе результата сравнения полученной сигнатуры с эталонной делается вывод об отсутствии или наличии искажений во входной анализируемой последовательности.

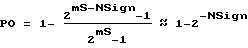

Если МСА выполнен в виде УВВ, подключенного к разъему расширения IBM PC и функционирующего в соответствии с табл. 1, то фрагмент программы формирования сигнатуры информационной последовательности длиной SeqSize будет иметь вид, приведенный в конце описания.

Таким образом, особенностью предлагаемого устройства является наличие дополнительного этапа преобразования информационной последовательности перед формированием сигнатуры. Суть алгоритма преобразования заключается в разбиении входной информационной последовательности на блоки и шифровании каждого слова и каждого блока. В отличие от стандартных алгоритмов шифрования методом замены для отдельных слов и блочных алгоритмов шифрования в данном МСА результат преобразования (шифрования) слова (или блока слов) зависит не только от кода слова (или блока), но и от его позиции в преобразуемой последовательности слов (или блоков). В результате максимально усложняется процедура поиска информационной последовательности, имеющей заданную сигнатуру, а значит увеличивается достоверность контроля целостности информации при использовании МСА в системах защиты от умышленных искажений. Если алгоритм формирования сигнатуры в блоке 11 основан на делении многочленов, то доля обнаруженных искажений в информационной последовательности длиной S при разрядности сигнатуры NSing равна .

.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1996 |

|

RU2120136C1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1995 |

|

RU2087030C1 |

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

| Сигнатурный анализатор | 1984 |

|

SU1264180A1 |

| Сигнатурный анализатор | 1987 |

|

SU1524054A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1246098A1 |

| Устройство для контроля хода микропрограмм | 1990 |

|

SU1734096A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1185338A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Сигнатурный анализатор | 1985 |

|

SU1336006A1 |

Изобретение относится к компьютерной технике и может использоваться для контроля целостности данных в системах защиты информации. Устройство содержит формирователь сигнатур и блок управления. Технический результат: повышение достоверности контроля при обнаружении умышленных искажений информации. С этой целью в анализатор дополнительно введены два блока преобразования информации. Сущность алгоритма преобразования заключается в разбиении входной информационной последовательности на блоки и шифровании каждого слова и каждого блока. В отличие от стандартных алгоритмов шифрования методом замены для отдельных слов и блочных алгоритмов шифрования в устройстве результат преобразования (шифрования) слова (или блока слов) зависит не только от кода слова (или блока), но и от их позиции в преобразуемой последовательности слов (или блоков). 7 ил., 1 табл.

Многоканальный сигнатурный анализатор, содержащий формирователь сигнатур, блок управления, причем тактовый вход блока управления образует одноименный вход анализатора, тактовый вход формирователя сигнатур подключен к первому выходу блока управления, группа информационных выходов формирователя сигнатур образует группу одноименных выходов анализатора, отличающийся тем, что он дополнительно содержит два блока преобразования, группа информационных входов первого блока преобразования образует группу одноименных входов анализатора, группа информационных выходов первого блока преобразования соединена группой одноименных входов второго блока преобразования, группа одноименных выходов которого соединена с группой одноименных входов формирователя сигнатур, первая и вторая группы входов режима анализатора подключены к первой и второй группам информационных входов блока управления соответственно, третья и четвертая группы входов режима - к группам одноименных входов первого и второго блоков преобразования соответственно, второй - пятый выходы блока управления соединены соответственно с тактовыми входами первого и второго блоков преобразования, с входами режима первого и второго блоков преобразования, шестой выход блока управления является выходом сигнала готовности устройства.

| Иванов М.А | |||

| и др | |||

| Сигнатурный анализ в задачах контроля и диагностики цифровых устройств | |||

| - М.: МИФИ, 1986, с.21, рис.12 | |||

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1995 |

|

RU2087030C1 |

| US 4524444 A, 18.06.85 | |||

| US 4991175 A, 05.02.91 | |||

| WO 9638788 A2, 05.12.96. | |||

Авторы

Даты

1999-07-10—Публикация

1998-02-10—Подача