Изобретение относится к вычислительной технике и может быть использвано в контрольно-испытательной аппаратуре дискретных объектов.

Цель изобретения - повышение быст роденствия.

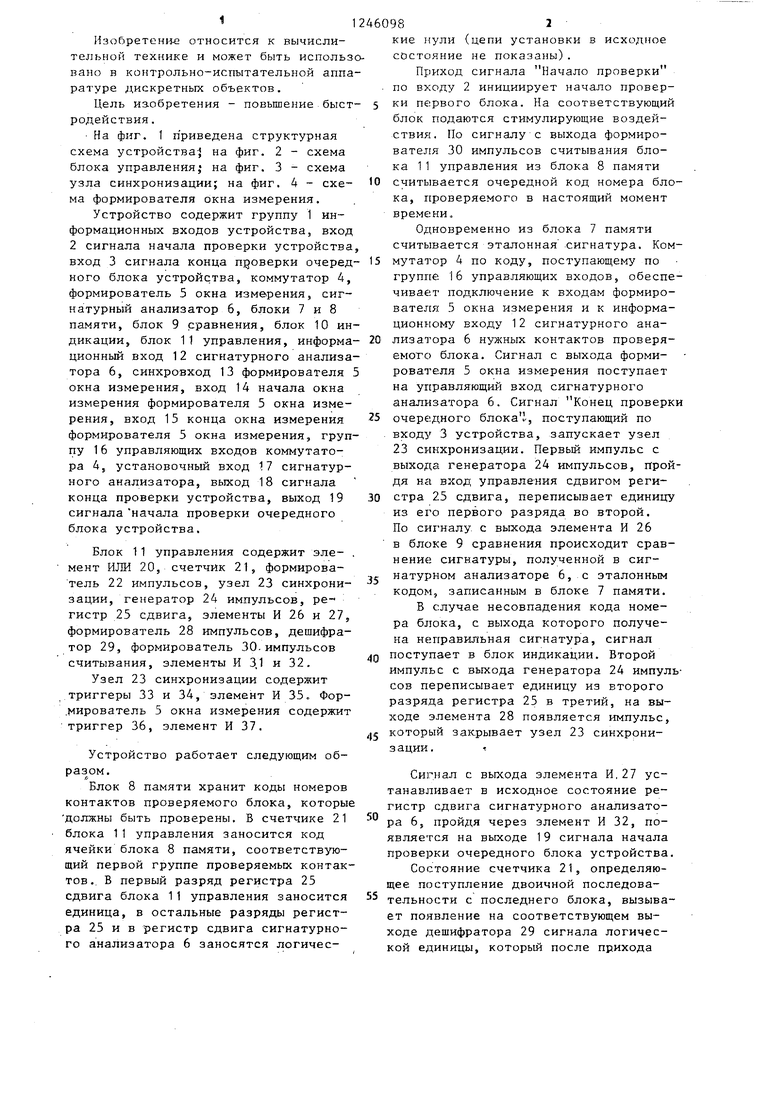

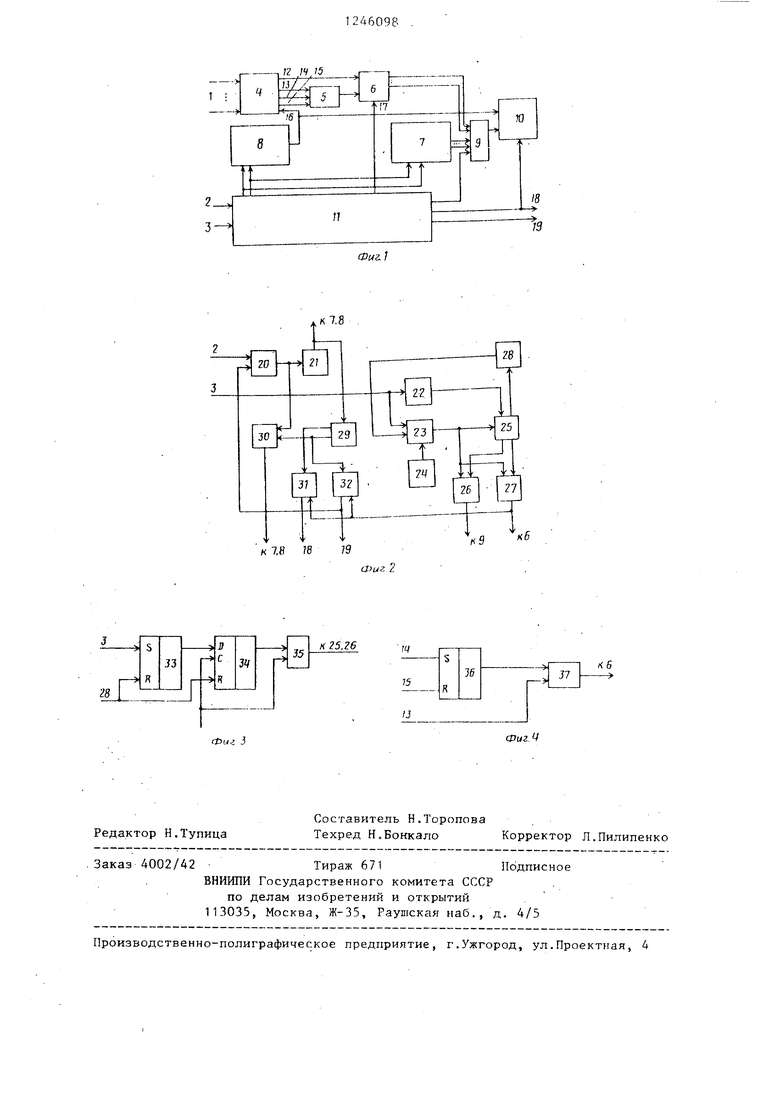

На фиг. 1 п риведена структурная схема устройства на фиг. 2 - схема блока управления; на фиг. 3 - схема узла синхронизации; на фиг. 4 схе- ма формирователя окна измерения.

Устройство содержит группу 1 информационных входов устройства, вход 2 сигнала начала проверки устройства вход 3 сигнала конца проверки очеред ного блока устройства, коммутатор 4, формирователь 5 окна измерения, сигнатурный анализатор 6, блоки 7 и 8 памяти, блок 9 сравнения, блок 10 индикации, блок 11 управления, информа ционный вход 12 сигнатурного анализатора 6, синхровход 13 формирователя окна измерения, вход 14 начала окна измерения формирователя 5 окна измерения, вход 15 конца окна измерения формирователя 5 окна измерения, группу 16 управляющих входов коммутатора 4, установочный вход 17 сигнатурного анализатора, выход 18 сигнала конца проверки устройства, выход 19 сигнала начала проверки очередного блока устройства.

Блок 11 управления содержит эле- мент ИЛИ 20, счетчик 21, формирова- тель 22 импульсов, узел 23 синхрони- зации, генератор 24 импульсов, ре- гистр 25 сдвига, элементы И 26 и 27, формирователь 28 импульсов, дешифратор 29, формирователь 30. импульсов считывания, элементы И 3,1 и 32.

Узел 23 синхронизации содержит триггеры 33 и 34, элемент И 35. Фор- .мирователь 5 окна измерения содержит

триггер 36, элемент И 37.

Устройство работает следующим образом.

Блок 8 памяти хранит коды номеров контактов проверяемого блока, которые должны быть проверены. В счетчике 21 блока 11 управления заносится код ячейки блока 8 памяти, соответствующий первой группе проверяемых контактов. В первый разряд регистра 25 сдвига блока 11 управления заносится единица, в остальные разряды регистра 25 и в регистр сдвига сигнатурного анализатора 6 заносятся логические кули (цепи установки в исходное состояние не показаны).

Приход сигнала Начало проверки по входу 2 инициирует начало проверки первого блока. На соответствующий блок подаются стимулирующие воздействия. По сигналу с выхода формирователя 30 импульсов считывания блока 11 управления из блока 8 памяти считывается очередной код номера блока, проверяемого в настоящий момент времени,.

Одновременно из блока 7 памяти считывается эталонная сигнатура. Коммутатор 4 по коду, поступающему по группе 16 управляющих входов, обеспечивает подключение к входам формирователя 5 окна измерения и к информационном ; входу 12 сигнатурного анализатора 6 нужных контактов проверяемого блока. Сигнал с выхода формирователя 5 окна измерения поступает на управляющий вход сигнатурного анализатора 6. Сигнал Конец проверк очерб .дного блока, поступающий по входу 3 устройства, запускает узел 23 синхронизации. Первый импульс с выхода генератора 24 импульсов, пройдя на вход управления сдвигом регистра 25 сдвига, переписывает единицу из его первого разряда во второй. По сигналу, с выхода элемента И 26 в блоке 9 сравнения происходит сравнение сигнатуры, полученной в сигнатурном анализаторе 6, с эталонным кодом, записанным в блоке 7 памяти. В случае несовпадения кода номера блока, с выхода которого получена неправильная сигнатура, сигнал поступает в блок индикации. Второй импульс с выхода генератора 24 импулсов переписывает единицу из второго разряда регистра 25 в третий, на выходе элемента 28 появляется импульс, который закрывает узел 23 синхронизации. .

Сигнал с выхода элемента И,27 устанавливает в исходное состояние регистр сдвига сигнатурного анализатора 6, пройдя через элемент И 32, появляется на выходе 19 сигнала начала проверки очередного блока устройства

Состояние счетчика 21, определяющее поступление двоичной последовательности с последнего блока, вызывает появление на соответствующем выходе дешифратора 29 сигнала логической единицы, который после прихода

импульса с выхода элемента И 27 вызывает появление на выходе элемента И -31 сигнала Конец проверки, после которого на экран блока индикации выводятся номера блоков, с выходов котрых были получены неправильные сигнатуры.

Формула изоб.ретения

Устройство для контроля цифровых узлов, содержащее первый блок памяти блок управления., блок сравнения, сигнатурный анализатор, причем группа выходов сигнатурного анализатора соединена с первой группой информационн входов блока сравнения, вторая группа информационных входов которого соединена с группой выходов первого блока памяти, группа адресных входов которого соединена с группой вых.одов блока управления, причем блок управления содержит счетчик, дешифратор, отличающееся тем, что, с целью повышения быстродействия, в устройство введен второй .блок памяти коммутатор , формирователь окна измер.ения, блок индикации, причем группа выходов блока управления соединена с группой адресных входов второго блок памяти, группа выходов которого соединена с группой управляющих входов коммутатора и с группой информационных входов блока индикации, информационный вход которого соединен с выходом блока сравнения, управляющий вход которого соединен с первым выходом блока управления, второй выход которого соединен с входом сброса сигнатурного анализатора, информацион ный вход которого соединен с первым входом коммутатора, второй, третий и четвертый входы которого соединены соответственно с синхровходом, с входом начала окна измер1ения и с входом окончания окна измерения формирователя окна измерения, выход которого соединен с управляющим входом сигнатурного анализатора, группа информационных входов коммутатора является группой информационных входов устройства, вход сигнала начала проверки устройства соединен с первым входом блока управления, второй вход которого является входом сигнала конца проверки очередного блока устройства, третий выход блока управления

соединен с управляющим входом блока индикации и является выходом сигнала конца проверки устройства, четвертый выход блока управления является выходом сигнала начала проверки очередного блока устройства, причем в блок управления введены элемент ИЛИ, четыре элемента И, два формирователя импульсов, формирователь импульсов считывания, узел синхронизации, генератор импульсов, регистр сдвига, выход первого разряда которого соединен с первым входом первого элемента И, первый вход второго элемента И соединен с выходом второго разряда регистра сдвига, второй вход первого элемента И соединен с вторым входом второго элемента И, с входом управления сдвигом регистра сдвига и с выходом узла синхронизации, тактовый вход которого соединен с выходом генератора импульсов,, выход третье го разряда регистра сдвига соединен с входом первого формирователя импульсов, выход которого соединен с входом управления остановом узла синхронизации, вход управления запуском которого является первым входом блока и соединен с входом второго формирователя импульсов, выход которого соединен с входом запуска регистра сдвига, второй вход блока управления соединен с первым входом элемента ИЛИ, выход которого соединен с первым входом формирователя импульсов считывания и с входом разрешения счета счетчика, выход которого соединен с входом дешифратора и является первым выходом группы выходов блока управления, первый выход дешифратора соединен с вторым входом формирователя импульсов считывания и с первым входом третьего элемента И, выход которого соединен с вторым входом элемента ИЛИ и является четвертым выходом блока, второй выход дешифратора соединен с первым входом четвертого элемента И, выход которого является третьим выходом блока, выход формирователя импульсов считывания является вторым выходом группы выходов блока управления, выход первого элемента И является первым выходом блока, выход второго элемента И соединен с вторыми входами третьего и четвертого элементов И и является вторым выходом блока.

IS

1

Ю

J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Сигнатурный анализатор | 1987 |

|

SU1444776A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Устройство сигнатурной проверки аналого-цифровых преобразователей | 1979 |

|

SU790293A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Сигнатурный анализатор | 1984 |

|

SU1223231A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

Изобретение относится к области вычислительной техники и может быть использовано в контрольно-испытательной аппаратуре дискретных объектов. Отличительной особенностью устройства является возможность задания кодов проверяемых контактов блоков из памяти их коммутации. Целью изобретения является повышение быстродействия. Это достигается введением второго блока памяти, коммутатора, формирователя окна измерения и блока индикации. 4 ил. с о N9 4ib О) О QD ОО

« 7,J /0 79

Фиг 3

Редактор Н.Тупица

Составитель Н.Торопова

Техред Н.Бонкало Корректор Л.Пилипенко

. Заказ 4002/42 Тиоаж 671й-

«ннипы гПодписное

ВНИИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие . г. УжгородГул проё

Фиг Ч

ктная, 4

| Авторское свидетельство СССР № 913385, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-23—Публикация

1983-07-01—Подача