Настоящее изобретение относится к ПЗУ X-конфигурации, в частности к X-ПЗУ, с целью повышения плотности интеграции при изготовлении маски ПЗУ и стираемого и программируемого ПЗУ.

Обычно в X-ПЗУ область контактов может совместно содержать множество ячеек, и множество ячеек расположено в конфигурации X, центрируясь вокруг области контактов.

Соответственно, X-ПЗУ широко используют для увеличения плотности интеграции.

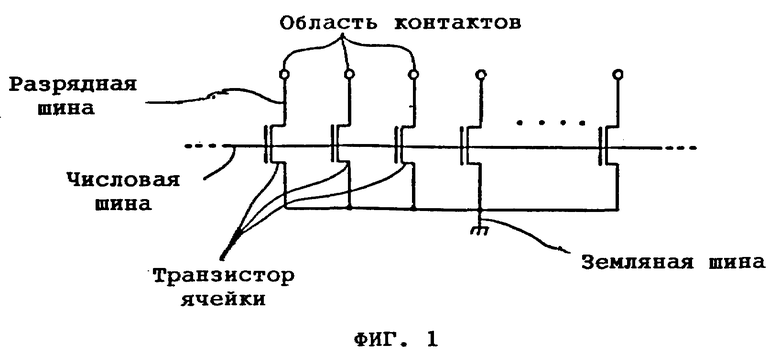

Фиг. 1 показывает структуру наиболее стандартной маски ПЗУ, постоянно сохраняющей информацию при использовании маски в известных технических решениях.

Как показано на фиг. 1, ПЗУ включает в себя транзисторы ячеек, имеющие память в 1 бит, числовую шину, соединенную с транзисторами ячеек, GND (земляную) шину, соединенную с каждым транзистором ячеек, разрядные шины, не показанные на фигуре, и области контактов для соединения всех транзисторов ячеек.

В качестве транзистора ячейки здесь используются FET (полевой транзистор).

Однако плотность интеграции указанной маски ПЗУ уменьшена, так как область контактов соответственно сформирована напротив каждого транзистора ячейки, как показано на фиг. 1.

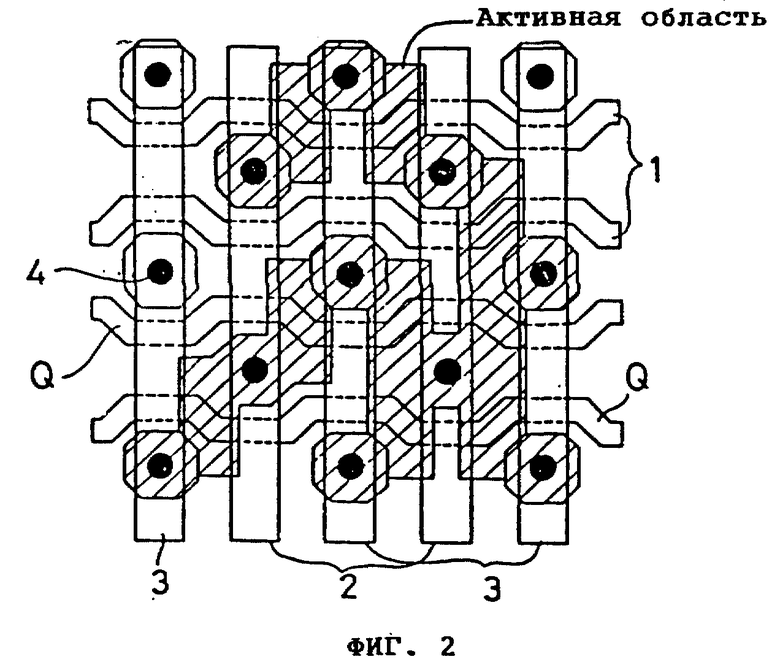

Фиг. 2 - схема компоновки X-ПЗУ для улучшения плотности интеграции, в которой числовая шина 1 расположена рядами с постоянным интервалом в вертикальном направлении, транзисторы Q (здесь FET используется в качестве транзистора ячейки) ячеек последовательно подключены к каждой числовой шине 1 на равных интервалах в горизонтальном направлении, шина 3 непостоянной земли и разрядная шина 2, в свою очередь, последовательно расположены в направлении, пересекающемся с каждой числовой шиной 1, а контактные области 4 сформированы между числовыми шинами так, чтобы иметь четыре транзистора совместно действующими.

На фигуре заштрихованные области являются активными.

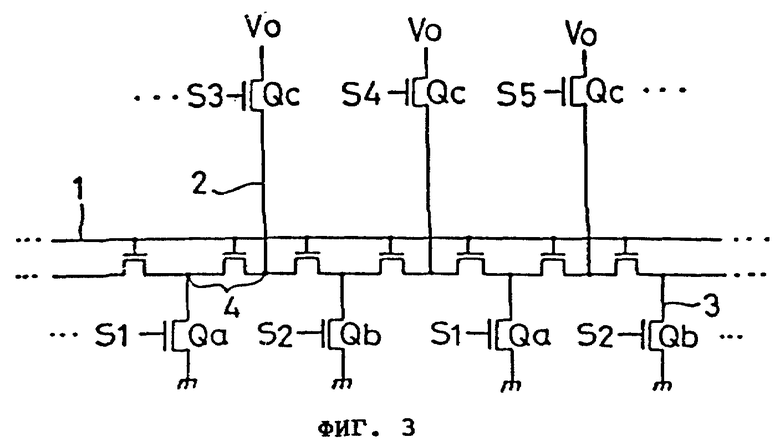

Фиг. 3 - схема фрагмента, соответствующего одной числовой шине среди шин 1, иллюстрируемых фиг. 2. На фиг. 3 между транзисторами Q ячеек, которые последовательно подключены к числовой шине 1 через равные интервалы, поочередно через область 4 контактов последовательно размещены шина 3 непостоянной GND и разрядная шина 2.

Транзистор Q с ячейки усиления считывания соответственно подключен к каждой разрядной шине 2, транзистор Qa ячейки запуска соответственно подключен к нечетной шине 3 непостоянной GND, а транзистор Qb ячейки запуска - к четной шине 3 непостоянной GND.

Соответственно, нужные шины из шин 3 непостоянной GND заземляются управляющими сигналами S1 и S2, приложенными к затворам транзисторов Qa и Qb ячеек запуска, а другие шины отключены или запитываются предварительно определенным напряжением от отдельной цепи (не показана).

Далее, управляющие сигналы от S3 и S5, поданные на затворы транзисторов Qc ячеек усиления считывания, служат для выдачи только выходных сигналов транзисторов Qc ячеек, соответствующих указанному адресу.

Как указано, GND шина X-ПЗУ известного технического решения названа шиной непостоянной GND, поскольку требуемые GND шины выбираются сигналами S1 и S2, и они являются земляными.

Кроме того, из-за того, что одна область 4 контактов обычно используется для четырех транзисторов ячеек, которые образованы в форме X, центрируясь вокруг нее, как показано на фиг. 2, плотность интеграции известного X-ПЗУ выше, чем плотность обычного H-ПЗУ.

На фиг. 2 и фиг. 3 числовая шина 1 сделана из поликристаллического кремния, а разрядная шина 2 и шина непостоянной GND сделаны из металла.

Заштрихованная область фиг. 2 показывает активную область, транзисторы ячеек сформированы активной областью, а числовая шина 1, разрядная шина 2 и шина непостоянной GND соединены друг с другом активной областью.

Работа известного X-ПЗУ, имеющего вышеуказанную структуру, будет описана более подробно.

Сначала, если на затворы транзисторов Qa и Qb ячеек запуска поданы управляющие сигналы S1 и S2, то выбираются четные или нечетные шины 3 непостоянной GND. В этот момент заряд, полученный между транзистором Q ячейки и разрядной шиной 2 с предварительно заданным напряжением от отдельной схемы, разряжается на выбранную шину 3 непостоянной GND через транзистор ячейки, соответствующий выбранной шине 3 непостоянной GND.

В этот момент на разрядной шине 2 возникает падение напряжения, и падение напряжения считывается с низким состоянием (или высоким состоянием) транзисторами ячеек, соответствующими выбранным шинам непостоянной GND, из транзисторов Qc ячеек усиления считывания, которые подключены к выходам разрядных шин 2.

То есть, когда ПЗУ запрограммирован для предотвращения протекания электрического тока через транзисторы Q ячеек, падения напряжения не возникает на разрядной шине 2, и транзисторами Qc ячеек усиления считывания считывается высокое состояние.

Способ для программирования указанных транзисторов Q ячеек является способом, перемещающим активную область, способом, повышающим пороговое напряжение ионной имплантации, и способом, повышающим пороговое напряжение посредством инжектирования заряда в отключенный затвор, как в стираемом и программируемом ПЗУ, использующим отключаемый затвор.

Практическая схема X-ПЗУ, как показано на фиг. 3, использует способ, перемещающий активную область, в качестве способа для программирования указанных транзисторов ячеек.

Как выше отмечено, структура известного X-ПЗУ, как показано на фиг. 2 и фиг. 3, может увеличить плотность интеграции устройства по сравнению с обычным H-ПЗУ, поскольку четыре транзистора, подключенные к числовой шине 1, сформированы так, чтобы иметь общую область контактов.

Однако из-за того, что один и тот же материал используется как для разрядной шины 2, так и для шины 3 непостоянной GND в известном X-ПЗУ, они должны формироваться через одинаковые интервалы.

Соответственно, из-за того, что имеется предел уменьшения конструктивных размеров, эффективная интеграция высокой плотности не может быть достигнута.

Кроме того, из-за того, что выбранный транзистор ячейки соответственно подключен к каждой шине непостоянной GND, интеграция высокой плотности не может быть достигнута.

Целью настоящего изобретения является для X-ПЗУ повысить плотность интеграции устройства посредством формирования шины непостоянной GND из двух классов: металлической шины непостоянной GND и шины GND из поликристаллического кремния и посредством эффективного расположения указанных шин непостоянной GND.

В соответствии с предпочтительным вариантом осуществления настоящего изобретения разработано улучшенное X-ПЗУ, в котором вытянутая горизонтально числовая шина из поликристаллического кремния расположена рядами, множество транзисторов ячеек горизонтально соединено с каждой силовой шиной из поликристаллического кремния типа, в котором металлическая разрядная шина и металлическая шина непостоянной GND сформированы поочередно между транзисторами ячеек в вертикальном направлении, пересекаясь с числовой шиной из поликристаллического кремния, расположенной рядами, каждая из областей контактов сформирована так, чтобы быть расположенной в месте, в котором четыре транзистора ячеек сформированы в форме X, концентрируясь вокруг нее, улучшение отличается тем, что шина непостоянной GND из поликристаллического кремния вместе с указанной металлической шиной непостоянной GND сформирована как шина непостоянной GND типа, в котором одна металлическая шина непостоянной GND соответственно размещена на обеих сторонах фиксированного числа шин непостоянной GND из поликристаллического кремния и расположена рядами, нечетные шины непостоянной GND из поликристаллического кремния из фиксированного числа шин непостоянной GND из поликристаллического кремния обычно сведены с одной металлической шиной непостоянной GND через обозначенную шину из поликристаллического кремния, четные шины непостоянной GND из поликристаллического кремния обычно подключены к другим шинам непостоянной GND через обозначенную шину из поликристаллического кремния, каждая металлическая шина непостоянной GND заземляется через соответствующие транзисторы ячейки запуска.

Краткое описание чертежей

Фиг. 1 - схема, показывающая структуру стандартного ПЗУ известного технического решения.

Фиг. 2 - схема компоновки X-ПЗУ известного технического решения.

Фиг. 3 - фрагмент схемы, соответствующий одной числовой шине фиг. 2.

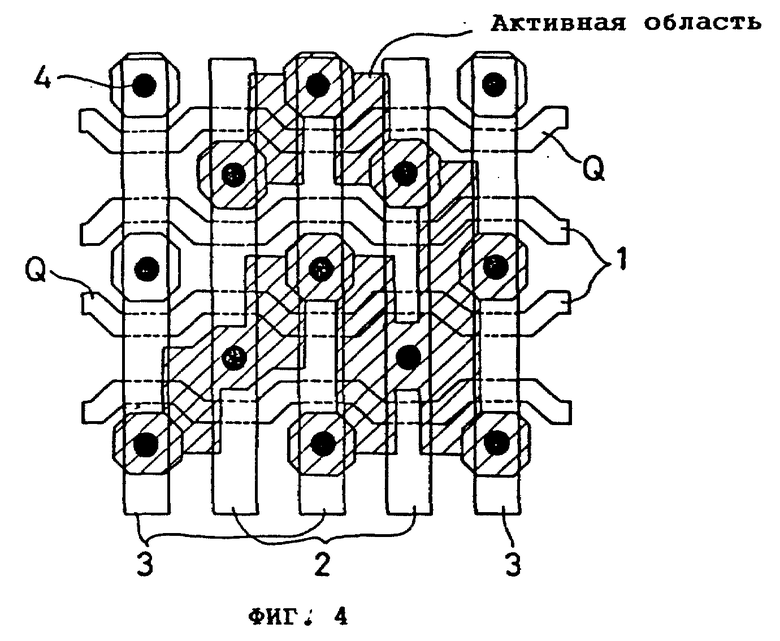

Фиг. 4 - схема компоновки X-ПЗУ в соответствии с настоящим изобретением.

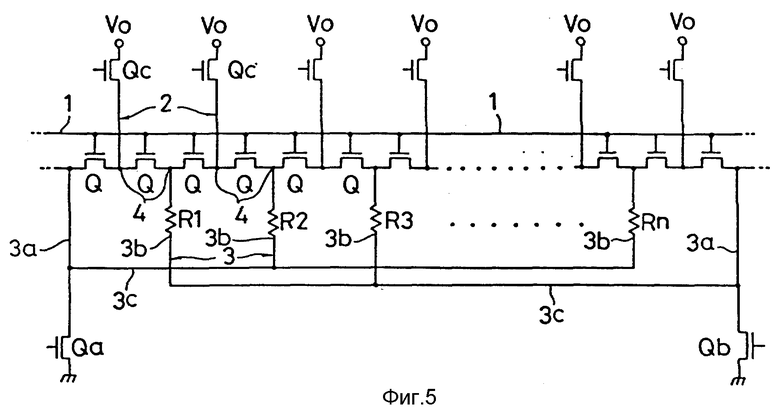

Фиг. 5 - фрагмент схемы, соответствующий одной числовой шине фиг. 3.

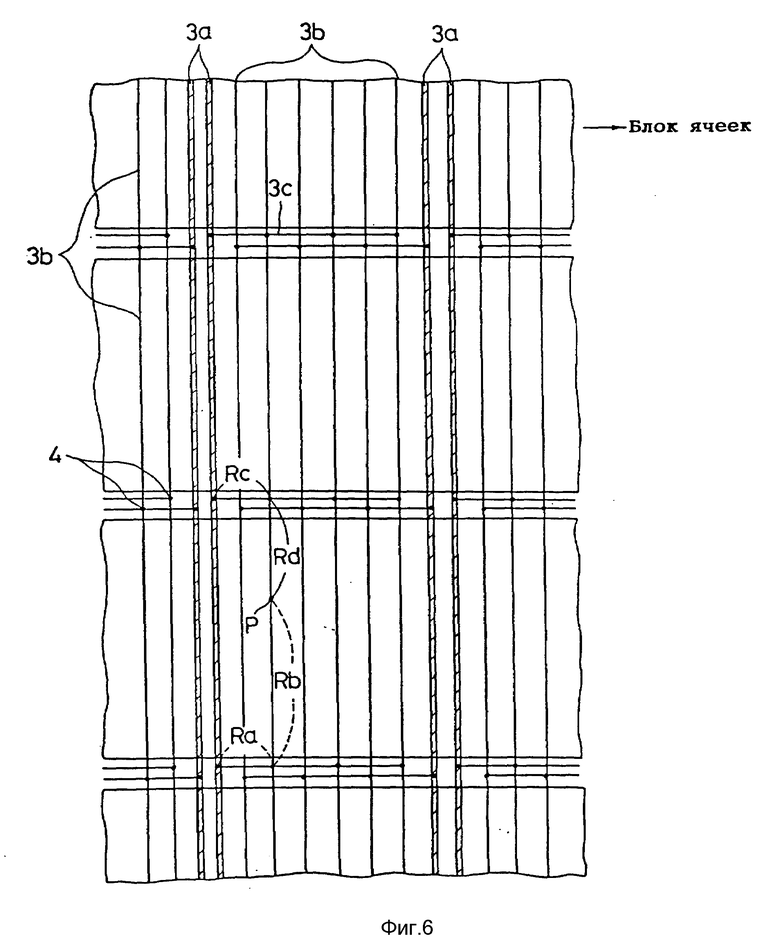

Фиг. 6 - чертеж, иллюстрирующий структуру шины непостоянной GND в соответствии с настоящим изобретением.

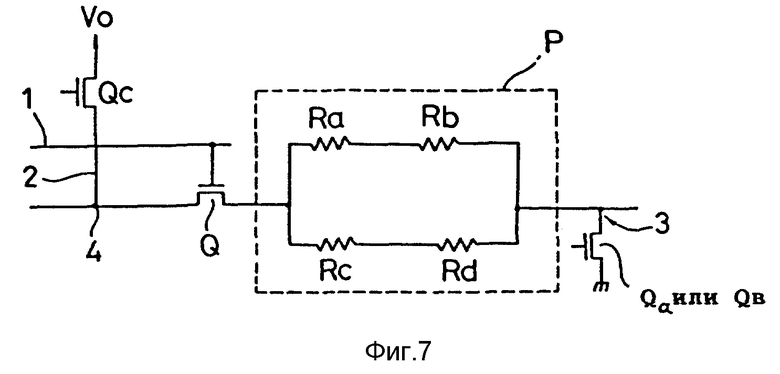

Фиг. 7 - эквивалентная схема части, соответствующей точке P фиг. 6.

Подробное описание предпочтительного варианта осуществления

Предпочтительный вариант осуществления настоящего изобретения описан со ссылкой на прилагаемые чертежи от фиг. 4 до фиг. 7.

Во-первых, фиг. 4 является схемой компоновки X-ПЗУ в соответствии с настоящим изобретением, которая идентична со схемой X-ПЗУ известного технического решения, показанной на фиг. 2.

То есть, числовая шина 1, которая вытянута по горизонтали, расположена последовательно через одинаковые интервалы в вертикально расположенных рядах, множество транзисторов Q ячеек, которые рядами расположены на равных расстояниях, подключены к каждой числовой шине таким образом, что разрядная шина 2 и шина 3 непостоянной GND расположены поочередно рядами, идущими в вертикальном направлении, пересекая указанную числовую шину 1, область 4 контактов расположена в месте, в котором четыре транзистора ячеек, подключенные к обозначенной числовой шине 1, расположены в форме X, концентрируясь вокруг нее.

Далее, отличающимся моментом при сравнении с известным техническим решением X-ПЗУ является то, что шина 3 непостоянной GND формируется как двухкомпонентная, из металлической шины 3a непостоянной GND и шины 3b непостоянной GND из поликристаллического кремния. Числовая шина 1 и разрядная шина сделаны из поликристаллического кремния и металла соответственно, которые идентичны с такими же материалами известного технического решения, но полисиликоны, используемые для числовой шины 1 и шины 3 непостоянной GND, имеют компоненты, отличные друг от друга. Взаимные соединительные связи между металлической шиной 3a непостоянной GND и шиной 3 непостоянной GND будут более подробно описаны ниже.

Фиг. 5 - подробная схема части, соответствующей одной числовой шине 1 фиг. 4 и X-ПЗУ в соответствии с настоящим изобретением, которое имеет такую же структуру, как известное X-ПЗУ, в котором множество транзисторов Q ячеек размещено рядами на одинаковых интервалах по горизонтали, а разрядные шины 2 и шина 3 непостоянной GND размещены рядами поочередно между транзисторами ячеек.

Однако здесь отдельным отличным моментом по сравнению со структурой известного X-ПЗУ является то, что металлическая шина 3a непостоянной GND соответственно сформирована на обеих сторонах шин 3b непостоянной GND из n (положительное целое).

Кроме того, нечетное из указанных n полисиликоновых шин 3b непостоянной GND обычно соединены с одной металлической шиной 3a непостоянной GND через обозначенную полисиликоновую шину 3c, а четные обычно соединены с другой через обозначенную полисиликоновую шину 3c. Как отмечено выше, выходы всех разрядных шин 2, сделанных из металла, соединены соответственно с транзисторами Qc ячеек усиления считывания.

Однако только выходы металлических шин 3a непостоянной GND из шин 3 непостоянной GND соответственно соединены с транзисторами Qa и Qb запуска, которыми выходы заземляются.

Наконец, требуются только два транзистора Q ячеек запуска напротив шин непостоянной GND из n+2.

Как выше упоминалось, из-за того, что шина 3 непостоянной GND состоит из двух металлических шин 3a непостоянной GND против полисиликоновых шин 3b непостоянной GND из n, когда полисиликоновая шина 3b непостоянной GND и металлическая разрядная шина 2 расположены поочередно между транзисторами Q ячеек, то поддерживается между ними только минимальный интервал.

Здесь номер 4 обозначает область контактов, а необъясненные символы от R1 до Rn являются компонентом сопротивления, который существует благодаря полисиликону полисиликоновых шин 3b непостоянной GND из n. В то же время, поскольку компонент сопротивления почти не существует в металле, они не обозначены в металлических шинах 3a непостоянной GND. Компонент сопротивления вызывает ухудшение пределов по шуму и скоростных характеристик, и способ уменьшения действия указанной причины будет более подробно описан ниже.

Работа схемы согласно фиг. 5 почти подобна работе схемы фиг. 3.

То есть, нечетные полисиликоновые шины 3a непостоянной GND и четные полисиликоновые шины 3b непостоянной GND одновременно выбираются соответствующими транзисторами Qa и Qb ячеек запуска управления. В этот момент заряды разряжаются на одну или другую металлическую шину 3a непостоянной GND через транзистор Q ячейки, соответствующий выбранной нечетной или четной полисиликоновой шине 3b непостоянной GND и полисиликоновой шине 3b непостоянной GND, которые предварительно подзаряжены между транзистором Q ячейки и разрядной шиной 2 до заранее определенного напряжения от отдельной схемы.

В этот момент падение напряжения, генерируемое на разрядной шине 2, считывается в виде высокого состояния или низкого состояния транзисторами ячеек, соответствующими выбранным нечетным или четным полисиликоновым шинам 3b непостоянной GND, из транзисторов Qc ячеек усиления считывания, подключенных к выходам разрядных шин 2.

Фиг. 6 показывает отношение связи полисиликоновой шины 3b непостоянной GND с металлической шиной 3a непостоянной GND, когда число n указанных полисиликоновых шин 3b непостоянной GND равно шести.

То есть, как иллюстрируется на фиг. 5, элемент типа, где одна металлическая шина 3a непостоянной GND соответственно сформирована на обеих сторонах шин 3 непостоянной GND из шести и расположена рядами и нечетные полисиликоновые шины 3b непостоянной GND из числа элементов типа шин 3 непостоянной GND вместе подключены к одной металлической шине 3a непостоянной GND через обозначенную полисиликоновую шину 3c, а четные полисиликоновые шины 3b непостоянной GND вместе подключены к другой через обозначенную полисиликоновую шину 3c.

В то же время компонент указанной обозначенной полисиликоновой шины 3c отличен от компонента полисиликоновой шины 3b непостоянной GND и идентичен с компонентом числовой шины 1.

С другой стороны, из-за того, что полисиликон включает в себя, как выше упоминалось, компонент сопротивления, чтобы уменьшить компонент сопротивления, выгодно, чтобы структура связей указанной металлической шины 3a непостоянной GND и полисиликоновой шины 3b непостоянной GND была надлежащим образом выполнена в каждом обозначенном блоке ячеек. Однако, если структура связей сделана редкой, то плотность интеграции устройства уменьшается.

Необъясненные символы Ra, Rb, Rc и Rd на фиг. 6 показывают индивидуальные сопротивления полисиликоновых шин 3b непостоянной GND в точке P.

Фиг. 7 - эквивалентная схема части, соответствующей указанной точке P. Величина резистора R в точке P может быть выражена следующей формулой (I):

R = Ra + Rb // Rc + Rd.

То есть, металлическая шина 3a непостоянной GND соединена с транзистором Q обозначенной ячейки через полисиликоновую шину 3c, имеющую значение Ra сопротивления, полисиликоновую шину 3b непостоянной GND, имеющую значение Rb сопротивления, полисиликоновую шину 3c непостоянной GND, имеющую величину Rc сопротивления, и полисиликоновую шину 3d непостоянной GND, имеющую значение Rd сопротивления.

Указанное значение R сопротивления предотвращает протекание электрического тока через транзистор Q ячейки и предотвращает падение напряжения на разрядной шине 2, вызывающие ухудшение предельных характеристик по шуму транзистора Qc ячейки усиления считывания и скоростных характеристик X-ПЗУ.

С другой стороны, фиг. 6 показывает только состояние соединения шин 3 непостоянной GND. Однако на практике числовая шина 1, сделанная из поликристаллического кремния, имеющего различный компонент с поликристаллическим кремнием шины 3 непостоянной GND, транзистор Q ячейки и разрядная шина 2, сделанная из металла, расположены между полисиликоновыми шинами 3b непостоянной GND.

Как указано выше, настоящее изобретение имеет следующий эффект.

Шина непостоянной GND формируется как двухкомпонентная, из металлической шины непостоянной GND и полисиликоновой шины непостоянной GND, посредством чего минимизируется интервал между разрядной шиной, сделанной из металла, и шиной непостоянной GND.

Соответственно, плотность интеграции X-ПЗУ может быть улучшена.

Кроме того, если интервал между разрядной шиной и шиной непостоянной GND минимизируется, размер ячейки в направлении числовой шины уменьшается.

В соответствии с уменьшением длины числовой шины главная причина замедления скорости X-ПЗУ, возникающего в числовой шине, может быть уменьшена.

Кроме того, в пропорции к уменьшению размера ячейки уменьшается электростатическая емкость разрядной шины и можно достигнуть улучшения другой скорости.

Изобретение относится к ПЗУ Х-конфигурации. Технический результат заключается в увеличении плотности интеграции. В Х-ПЗУ металлическую шину непостоянной земли формируют таким образом, что металлическая шина непостоянной земли расположена на обеих сторонах фиксированного числа полисиликоновых шин непостоянной земли GND. Нечетные полисиликоновые шины непостоянной земли соединяют с одной металлической шиной непостоянной GND через полисиликоновую шину. Четные полисиликоновые шины непостоянной GND соединяют с другой металлической шиной непостоянной GND через полисиликоновую шину. Каждая из металлических шин непостоянной GND соединяется с выводом GND через управляющие транзисторы ячеек. 7 ил.

Полупроводниковое постоянное запоминающее устройство X-образной формы, содержащее числовую шину, множество транзисторов ячеек, расположенных на равных расстояниях и подключенных к числовым шинам, разрядную шину и шину непостоянной земли, которые расположены поочередно, пересекая числовую шину, каждая область контактов сформирована с возможностью взаимного соединения соответствующих разрядной шины, шины непостоянной земли и транзистора ячейки, отличающееся тем, что шина непостоянной земли сформирована из двух металлических шин непостоянной земли, одной шины непостоянной земли из поликристаллического кремния для соединения нечетных шин непостоянной земли с одной металлической шиной непостоянной земли, другой поликристаллической кремниевой шины для соединения четных шин непостоянной земли с другой металлической шиной непостоянной земли, а также содержит два транзистора запуска, включенных с возможностью подсоединения к обеим металлическим шинам непостоянной земли.

| The Design and analysys of VLSI circuits | |||

| Addisson Westley Publishing Company, 1985, Lance A | |||

| Glasser и др | |||

| Masachusetts Institute of Technology, p.380 - 383 | |||

| Пономарев М.Ф | |||

| Конструирование и расчет микросхем и микропроцессоров | |||

| - М.: Радио и связь, 1986, с.72 - 81 | |||

| Полупроводниковые и запоминающие устройства и их применение | |||

| / Под ред.А.Ю.Гордонова | |||

| - М.: Радио и связь, 1981, с.148 - 150. |

Авторы

Даты

1999-08-20—Публикация

1991-06-11—Подача