Настоящее изобретение относится к полупроводниковому запоминающему устройству и особенно к цепи для генерирования напряжения внутреннего источника в полупроводниковом запоминающем устройстве.

Так как полупроводниковое запоминающее устройство обладает высокой степенью интеграции, элементы памяти, вмонтированные в запоминающее устройство, весьма миниатюрны. Поэтому, если внешнее напряжение, приложенное к запоминающему устройству, неправильно отрегулировано, может возникнуть сильное электрическое поле, которое приведет к перенапряжению, приложенному к запоминающему устройству, а значит и к разрушению элементов памяти. В полупроводниковом запоминающем устройстве более, чем порядка 16 Мбит следует использовать цепь для генерирования внутреннего напряжения для того, чтобы уменьшить уровень внешнего напряжения до значения рабочего напряжения запоминающего устройства. Например, в полупроводниковом запоминающем устройстве более, чем порядка 16 Мбит следует использовать внутреннее напряжение 4 В, которое обычно устанавливается путем снижения внешнего напряжения 5 В.

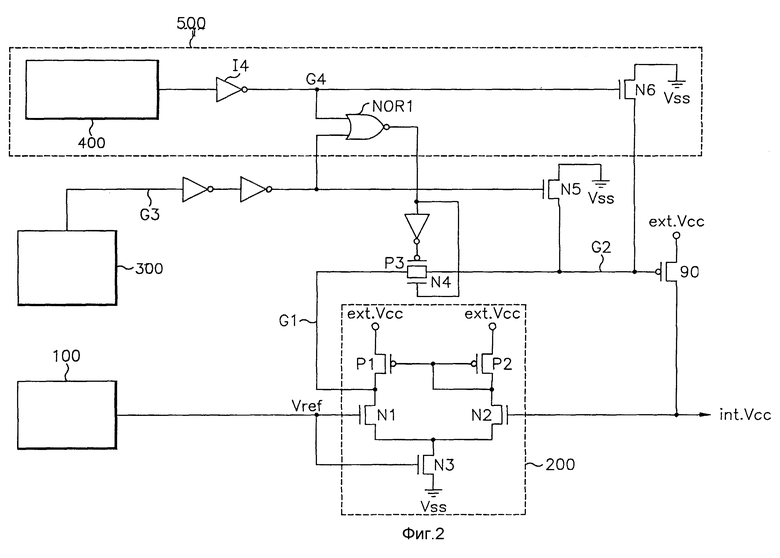

На фиг. 1 показана цепь для генерирования напряжения внутреннего источника в соответствии с известным уровнем техники, которая включает генератор опорного напряжения 100 для генерирования опорного напряжения Vref (Vопорное), компаратор 200 для сравнения напряжения внутреннего источника int. Vcc (Vвнутр.) с опорным напряжением Vref, и запускающего каскада 90 для подачи под управлением компаратора 200 внешнего напряжения ext • Vcc (Vвнешн) к напряжению внутреннего источника и генератора пережигающего опорного напряжения 300. Напряжение внутреннего источника int • Vcc подается на элементы памяти запоминающего устройства, а также и к NMOS (n-МОП) транзистору N 2 компаратора 200. Если напряжение внутреннего источника int • Vcc опускается ниже опорного напряжения Vref из-за потребления мощности элементами памяти, уровень выходного сигнала G1 компаратора 200 понизится настолько, чтобы полностью включить запускающий каскад 90 для компенсации падения напряжения внутреннего источника int • Vcc. С другой стороны, если напряжение внутреннего источника int • Vcc поднимается выше опорного напряжения Vref, выходной сигнал G1 компаратора 200 увеличивается настолько, чтобы вызвать отключение запускающего каскада 90 для снижения напряжения внутреннего источника int • Vcc до опорного напряжения Vref

Если уровень напряжения внешнего источника ext • Vcc выше уровня пережигающего опорного напряжения, генератор пережигающего опорного напряжения 300 генерирует выходной сигнал C3 уровня логической "1", чтобы таким образом через инверторы 11 и 12 закрыть проходные ключи N4, P3 и включить понижающий транзистор 5, так, чтобы напряжение внешнего источника ext • Vcc подавалось к запоминающему устройству через запускающий каскад 90. В этом случае, так как проходной ключ N4, P3 закрыт, выходной сигнал G1 компаратора 200 не влияет на сигнал G2, который подается к затвору запускающего каскада 90.

В такой общепринятой цепи для генерирования напряжения внутреннего источника, если уровень напряжения внешнего источника ext • Vcc ниже уровня опорного напряжения Vref, проходной ключ N4, P3 открывается таким образом, чтобы выходной сигнал G1 компаратора воздействовал на запускающий каскад 90. Следовательно, когда напряжение внутреннего источника int • Vcc изменяется под действием пикового тока, генерируемого в запоминающем устройстве, напряжение G изменяется таким образом, что происходит мгновенное падение напряжения внутреннего источника int • Vcc ниже напряжения внешнего источника и тем самым снижается быстродействие элементов памяти, что вызывает неправильное функционирование.

Целью изобретения является создание цепи для генерирования напряжения внутреннего источника, обеспечивающего подачу напряжения внешнего источника непосредственно к элементам памяти полупроводникового запоминающего устройства, когда уровень напряжения внешнего источника ниже, чем уровень опорного напряжения.

Другой целью настоящего изобретения является создание цепи для генерирования напряжения внутреннего источника, предотвращающей уменьшение быстродействия элементов памяти из-за мгновенного падения напряжения внутреннего источника.

В соответствии с первым вариантом настоящего изобретения цепь для генерирования на основе данного напряжения внешнего источника, напряжения внутреннего источника для его подачи к элементам памяти полупроводникового устройства, включает первое устройство генерирования опорного напряжения для генерирования опорного напряжения, устройство сравнения напряжения внутреннего источника с опорным напряжением, запускающее устройство для подвода напряжения внешнего источника к напряжению внутреннего источника под управлением устройства сравнения, второе устройство генерирования опорного напряжения для генерирования другого опорного напряжения и для генерирования управляющего сигнала, полностью открывающего запускающее устройство, когда уровень напряжения внешнего источника ниже уровня опорного напряжения, и при этом управляющий сигнал второго устройства генерирования опорного напряжения для генерирования другого опорного напряжения предотвращает передачу выходного сигнала устройства сравнения к запускающему устройству для подведения напряжения от внешнего источника к элементам памяти.

Уровень выходного сигнала второго устройства для генерирования другого опорного напряжения изменяется в соответствии с уровнем напряжения внешнего источника напряжения.

Второе устройство для генерирования другого опорного напряжения предпочтительно включает по крайней мере компаратор напряжения и делитель напряжения.

В соответствии со вторым вариантом настоящего изобретения цепь для генерирования на основе подаваемого напряжения внешнего источника, напряжения внутреннего источника для его подачи к элементам памяти полупроводникового устройства включает первое устройство генерирования опорного напряжения для генерирования опорного напряжения, устройство сравнения напряжения внутреннего источника с опорным напряжением, запускающее устройство для подвода напряжения внешнего источника к напряжению внутреннего источника под управлением устройства сравнения, второе устройство генерирования опорного напряжения для генерирования другого опорного напряжения и для генерирования управляющего сигнала для полного включения запускающего устройства, когда уровень напряжения внешнего источника оказывается ниже уровня опорного напряжения, и при этом управляющий сигнал второго устройства генерирования опорного напряжения для генерирования другого опорного напряжения полностью включает запускающее устройство для подведения напряжения внешнего источника к элементам памяти, если уровень напряжения внешнего источника ниже уровня опорного напряжения.

Уровень выходного сигнала второго устройства для генерирования другого опорного напряжения изменяется в соответствии с уровнем напряжения внешнего источника напряжения.

Второе устройство для генерирования другого опорного напряжения предпочтительно включает по крайней мере компаратор напряжения и делитель напряжения.

На фиг.1 представлена общепринятая схема цепи для генерирования напряжения внутреннего источника.

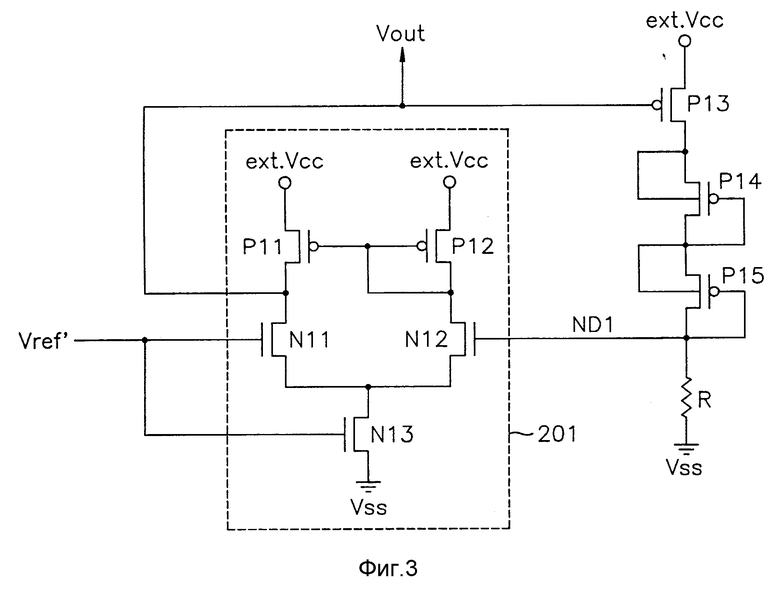

На фиг. 2 представлена схема цепи для генерирования напряжения внутреннего источника в соответствии с настоящим изобретением, и

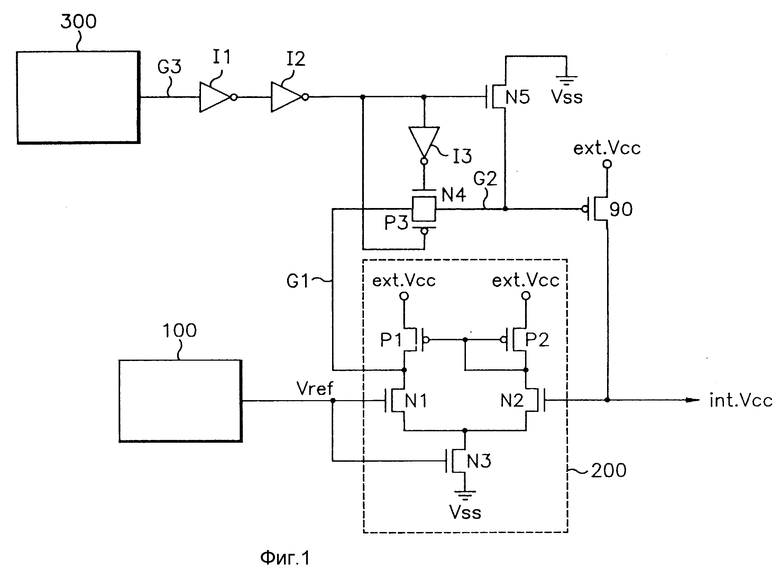

на фиг. 3 представлена схема генератора низкого опорного напряжения на фиг. 2.

В соответствии с фиг.2 генератор опорного напряжения 100 необходим для генерирования опорного напряжения Vref. Компаратор 200 необходим для сравнения напряжения внутреннего источника int • Vcc ее с опорным напряжением Vref. Запускающий каскад 90 необходим для подвода напряжения внешнего источника ext • Vcc к напряжению внутреннего источника int • Vcc под управлением компаратора 200. Генератор пережигающего опорного напряжения 300 генерирует выходной сигнал G3, предотвращающий подачу выходного сигнала G1 от компаратора на запускающий каскад 90 и полностью открывающий запускающий каскад 90. Генератор низкого опорного напряжения 400 необходим для генерирования управляющего сигнала, предотвращающего передачу выходного сигнала G1 от компаратора на запускающий каскад 90 и полностью открывающий запускающий каскад 90, когда уровень напряжения внешнего источника ext • Vcc ниже уровня опорного напряжения Vref.

Генератор пережигающего опорного напряжения 300 генерирует выходной сигнал G3 уровня логической "1", закрывающий проходные ключи N4, P3 так, что сигнал G2 уровня логического "0" прикладывается к затвору запускающего каскада 90. Тогда запускающий каскад 90 открывается так, что напряжение внешнего источника ext • Vcc прикладывается непосредственно к элементам памяти.

Если уровень напряжения внешнего источника ext • Vcc ниже уровня опорного напряжения Vref, генератор низкого опорного напряжения 400 генерирует выходной сигнал уровня логического "0". Выходной сигнал генератора низкого опорного напряжения 400 с помощью инвертора 14 превращается в сигнал G4 уровня логической "1". Следовательно, выходной сигнал NOR1 ключа NOR имеет уровень логического "0", закрывая таким образом проходные ключи N4, P3. Кроме того, сигнал G4 уровня логической "1" открывает понижающий транзистор N6. Соответственно уровень напряжения G2 становится равным напряжению земли, так что запускающий каскад 90 полностью открывается для того, чтобы напряжение внешнего источника ext • Vcc подвести к элементам памяти запоминающего устройства. В то же время закрываются проходные ключи N4, P3 для того, чтобы предотвратить подачу выходного сигнала компаратора 200 к запускающему каскаду 90. Этим достигается то, что напряжение внешнего источника ext • Vcc постоянно приложено к элементам памяти, даже если уровень напряжения внутреннего источника int • Vcc ниже уровня опорного напряжения Vref. Таким образом надежно поддерживается быстродействие элементов памяти.

На фиг. 3 показан генератор низкого опорного напряжения 400 в цепи для генерирования напряжения внутреннего источника. Если напряжение Vref' постоянно, параметры PMOS (p-МОП) транзисторов P14 и P15 с диодными характеристиками и величина сопротивления резистора R могут быть подобраны так, чтобы путем деления напряжения установить желаемый уровень напряжения в точке ND1. Когда приложено напряжение от внешнего источника ext • Vcc, уровень напряжения в точке ND1 становится ниже уровня опорного напряжения Vref' после чего уровень напряжения в точке ND1 становится равным уровню напряжения Vref'. Следовательно, выходной сигнал Vont уровня логического "0" с помощью инвертора 14 на фиг.2 преобразуется в выходной сигнал G4 уровня логической "1".

Таким образом, если уровень напряжения внешнего источника выше уровня опорного напряжения, к элементам памяти с помощью цепи настоящего изобретения подается напряжение внутреннего источника заранее определенного уровня. С другой стороны, если уровень напряжения внешнего источника ниже, чем уровень опорного напряжения, напряжение внешнего источника подается непосредственно к элементам, памяти, повышая таким образом их быстродействие.

Цепь для генерирования напряжения внутреннего источника, подводимого к элементам памяти полупроводникового устройства, включают цепь для генерирования опорного напряжения, компаратор для сравнения напряжения внутреннего источника с опорным напряжением, запускающий каскад для подвода под управлением компаратора напряжения внешнего источника к напряжению внутреннего источника и цепь для генерирования низкого опорного напряжения для генерирования управляющего сигнала, полностью включающего запускающий каскад, когда уровень напряжения внешнего источника ниже уровня опорного напряжения, за счет чего управляющий сигнал указанной цепи, генерирующей низкое опорное напряжение, предотвращает подачу выходного сигнала с компаратора с тем, чтобы подать напряжение внешнего источника на элементы памяти запоминающего устройства. Техническим результатом является повышение быстродействия. 2 с.п. и 4 з.п.ф-лы, 3 ил.

| US 5103158 А, 07.04.92 | |||

| Источник питания с защитой от перегрузки | 1982 |

|

SU1112354A1 |

| Стабилизированный источник постоянного напряжения | 1983 |

|

SU1112355A1 |

Авторы

Даты

1999-09-10—Публикация

1993-03-30—Подача