Изобретение относится к области техники, занимающейся разработкой вычислительно-управляющих систем объектов различного назначения (например, вычислительно-управляющей системы ракетных комплексов подвижного базирования, подверженных захвату террористами в процессе их автономного боевого дежурства, с целью производства штатных пусков ракет в рамках диверсионных действий).

Известно значительное количество способов и устройств по защите информации в вычислительных системах различного назначения, основанных на ограничении доступа к информации различного уровня конфиденциальности, использование паролей при входе в систему, блокировки отдельных блоков памяти, применение средств криптографической защиты, подавления побочного электромагнитного излучения вычислительных устройств и каналов передачи информации (патенты Франции NN 2673477, 2690258, 2702857; патенты Германии NN 4315732, 4103173, патенты США NN 5136712, 5339427).

Наиболее близким по технической сущности является устройство для защиты информации по заявке ЕПВ (EP) NN 0449256 МКИ G 06 F 12/14, содержащее микроконтроллер, включающий в себя первый блок памяти, в котором в инверсном порядке хранятся зашифрованные программные данные, второй блок памяти, в которой хранится ключ к шифру, необходимый для декодирования пароля, хранящегося в первой памяти, центральный процессор, управляющий записью или считыванием данных из первого и второго блоков памяти, и блок, который на основе ключа, хранящегося во втором блоке памяти, дескремблирует шифр программных данных, хранящихся в первом блоке памяти, когда процессор осуществляет доступ к памяти на основе продекодирования данных.

В рассматриваемом устройстве не фиксируются попытки несанкционированного доступа потенциального нарушителя к ресурсам вычислительной системы и не формируются дополнительные действия, препятствующие этим попыткам, что делает недостаточно эффективной защиту вычислительного комплекса от несанкционированного доступа.

Целью настоящего изобретения является повышение эффективности системы защиты вычислительного комплекса от несанкционированного доступа путем выявления и фиксации попыток несанкционированного доступа и передачи части вычислительных ресурсов высокоприоритетному программному модулю на время, адекватное количеству несанкционированных попыток.

Поставленная цель достигается тем, что в известное устройство для защиты информации, содержащее первый блок памяти с информацией о защите, второй блок памяти с ключом к шифру, центральный процессор, блок ввода и отображения информации, включающий в себя блок набора данных, подключенный через первую схему И к первому входу центрального процессора, блок отображения, соединенный с первым выходом центрального процессора и блок разрешения ввода, подключенный ко второму входу первой схемы И, введены последовательно соединенные блок хранения результатов текущих решений, вход которого соединен со вторым выходом центрального процессора, первый блок сравнения, счетчик количеств попыток несанкционированного доступа, схема ИЛИ, блок управления памятью, первый и второй входы которого соединены соответственно с выходами первого и второго блоков памяти, первый выход соединен со вторым входом центрального процессора, а второй выход - со входом блока хранения эталонных решений, выход которого соединен со вторым входом первого блока сравнения, последовательно соединенные формирователь импульсов и счетчик импульсов, второй вход которого соединен с выходом блока разрешения ввода, а выход соединен с третьим входом первого блока сравнения, третий блок памяти с программой дежурного модуля, соединенный через вторую схему И с третьим входом центрального процессора, последовательно соединенные формирователь количеств циклов, третья схема И, ко второму входу которой подключен блок задержки, задатчик циклов и второй блок сравнения, выход которого соединен с четвертым входом центрального процессора, счетчик циклов, вход которого соединен с третьим выходом центрального процессора, а выход - со вторым входом второго блока сравнения, формирователь временных меток, соединенный с пятым входом центрального процессора, при этом входы блока задержки и формирователя количества циклов соединены с первым выходом первого блока сравнения, а его второй выход соединен со вторым входом схемы ИЛИ, к третьему входу которой и ко второму входу второй схемы И подключен формирователь сигнала на запуск устройства, в первом блоке памяти последовательно размещены по заданным адресам программы защиты от несанкционированного доступа и эксплуатационная программа вычислительной системы, а во втором блоке памяти ключом является размещенная в нем последовательность соответствующих эталонных решений программ защиты.

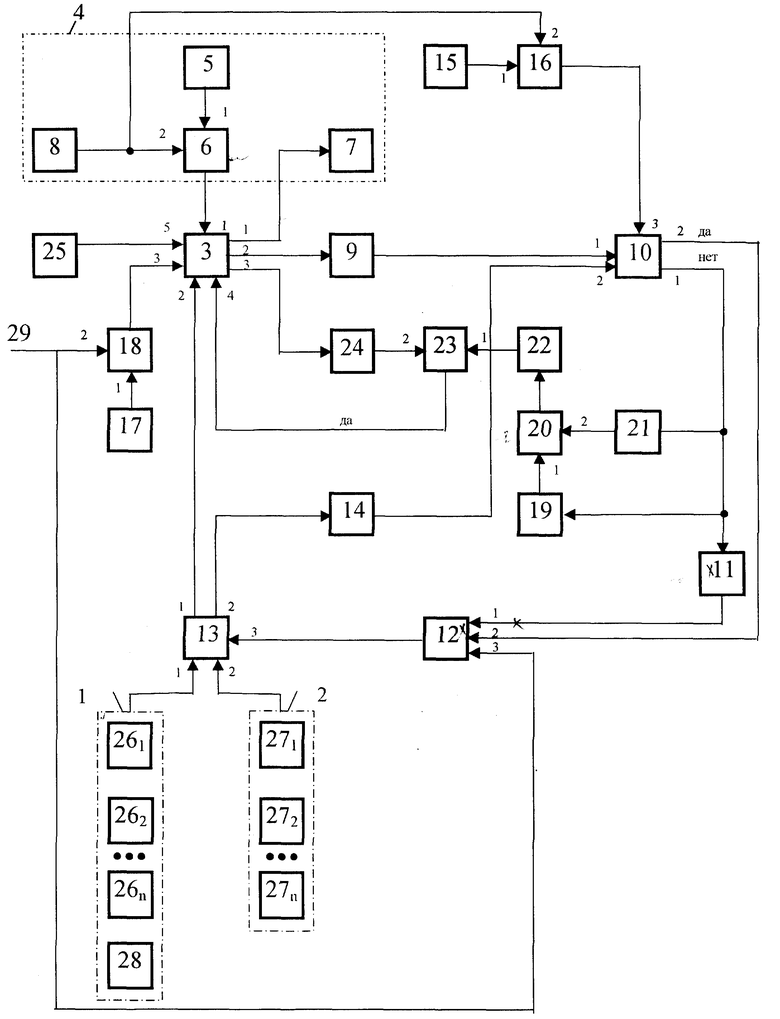

На фиг. 1 представлена блок-схема устройства для защиты вычислительного комплекса от несанкционированного доступа.

В устройство для защиты вычислительного комплекса от несанкционированного доступа входят: первый блок памяти 1, второй блок памяти 2, центральный процессор 3, блок ввода и отображения информации 4, включающий в себя блок набора данных 5, первую схему И 6, блок отображения (информации) 7 и блок разрешения ввода 8; блок хранения результатов текущих решений 9, первый блок сравнения 10, счетчик количеств попыток несанкционированного доступа 11, схему ИЛИ 12, блок управления памятью 13, блок хранения эталонных решений 14, формирователь импульсов 15, счетчик импульсов 16, третий блок памяти с программой дежурного модуля 17, вторую схему И 18, формирователь количества циклов 19, третью схему И 20, блок задержки 21, задатчик количества циклов 22, второй блок сравнения 23, счетчик циклов 24, формирователь временных меток 25, программы защиты от несанкционированного доступа: 261...26n, эталонные решения программ защиты: 271...27n, эксплуатационную программу вычислительного комплекса 28; вход устройства 29.

Устройство многопреградной системы защиты информации в вычислительных системах работает следующим образом. После включения вычислительной системы (например, наземной вычислительной системы ракетного комплекса подвижного базирования, обеспечивающей взаимодействие с системой целеуказания, формирование исходных данных для стрельбы по заданной цели, управление технологическим оборудованием комплекса, а также проведение пуска ракет по соответствующей циклограмме) автоматически в нее вводится и реализуется тест начального включения для определения технического состояния системы. По его положительному завершению формируется результат тестирования и по входу 29 (см. фиг. 1) в виде импульса подается на второй вход второй схемы И 18 и на третий вход схемы ИЛИ 12. Информация о его появлении через схему ИЛИ 12 поступает на третий вход блока управления памятью 13, который по заданному адресу выбирает из первого блока памяти 1 первую программу защиты информации 261 (например, поверки правильности введения пароля) и записывает ее в оперативное запоминающее устройство (ОЗУ) центрального процессора 3, который сразу переходит к ее реализации. Практически одновременно (с запаздыванием на реализацию предыдущей операции) блок управления памятью 13 выбирает из блока памяти 2 эталонное решение 271 записанной в ОЗУ процессора 3 задачи защиты информации 261 (в данном случае правильный пароль) и записывает его в блок хранения эталонных решений 14. Центральный процессор 3 в процессе решения записанной в его ОЗУ первой программы защиты 261 выводит на блок отображения информации 7 ( например, дисплей) предложение пользователю вычислительной системы ввести необходимые исходные данные, состав или содержание которых определяется алгоритмом введенной программы защиты (в данном случае предложение типа: "введите пароль"). Пользователь вычислительной системы (или возможный нарушитель) на наборном поле блока набора данных 5 (клавиатура вычислительной системы) набирает требуемые исходные данные (в данном случае пароль) и средствами блока разрешения ввода 8 и первой схемы И 6 вводит эти данные (пароль) в центральный процессор 3. Следует отметить, что может быть использована иная процедура ввода исходных данных, например, когда каждая буквенно-символьная клавиша через регистр прерывания процессора вводит соответствующий символ в темпе ее нажатия.

Центральный процессор 3 по получении полного состава необходимых исходных данных завершает решение введенной в него программы 261 (например, расшифровывает пароль, форматирует его и т.д.) и записывает его результат (в данном случае пароль) в блок хранения результатов текущих решений 9. Одновременно с вводом исходных данных с выхода блока разрешения ввода 8 подается сигнал на сброс (обнуление) счетчика импульсов 16, который начинает заполняться импульсами, поступающими с формирователя импульсов 15 с определенной частотой. После его переполнения на его выходе появляется сигнал, который поступает на третий вход первого блока сравнения 10, а сам счетчик становится на "защелку", т.е. он перестает фиксировать поступающие на его вход импульсы с формирователя 15. Первый блок сравнения 10 после прихода импульса со счетчика 16 считывает из блоков 14 и 9 эталонное значение результата 271 (в данном случае истинного пароля) с полученным результатом решения задачи по программе защиты 261 (введенный пароль) и сравнивает их. В зависимости от результата сравнения формируется единичный сигнал на первом ("Нет") или втором ("Да") выходах первого блока сравнения 10. При сравнении результатов ("Да"), т.е. пользователем введен истинный пароль, сигнал со второго выхода блока разности 10 через схему ИЛИ 12 поступает на вход блока управления памятью 13 и по описанной выше схеме в ОЗУ центрального процессора 3 будет введена вторая программа защиты информации 262 а в блок хранения 14 - соответствующее эталонное (истинное) решение этой задачи 272. Центральный процессор 3 в процессе решения записанной в ОЗУ второй программы защиты выводит на блок отображения 7 предложение пользователю (взломщику) вычислительной системы ввести необходимые исходные данные, состав и содержание которых определяется алгоритмом этой второй задачи. Этой задачей может быть, например, шахматная задача типа: "белые начинают и выигрывают", "мат в два или три хода" и др. Следует отметить, что выбор такого рода второй задачи требует более обширной эрудиции у взломщика, а также времени раздумывания на ее решение в условиях его дефицита. При этом эталонные решения, записанные в блок хранения эталонных решений 14, могут находиться в области иррационального мышления. Например, для шахматной задачи ими могут быть: ход пешкой назад, в бок, через два поля; ряд ходов только определенными фигурами; взятие собственного короля своей фигурой и др. Пользователь на наборном поле блока набора данных 5 набирает требуемые в рамках данной задачи исходные данные (в данном случае шахматный ход) и вводит описанными средствами в центральный процессор 3, сбрасывая (обнуляя) при этом счетчик импульсов 16. Результаты решения по описанной выше схеме записываются в блок хранения 9. А после очередного переполнения счетчика 16 в блоке сравнения 10 происходит сравнение полученного и эталонного результатов, хранящихся в блоках 9 и 14. Если на втором выходе блока сравнения 10 сформируется "1" (т.е. "Да"), то по описанной выше схеме через схему ИЛИ 12 и блок управления памятью в ОЗУ центрального процессора 3 будет введена программа третьей задачи защиты 263, а в блок памяти 14 - ее эталонное решение 273. Если "1" формируется на первом выходе первого блока сравнения 10 ("Нет", т.е. несовпадение решений), то этот сигнал поступает одновременно на входы блока задержки 21, формирователя количества циклов 19 и счетчик количества попыток несанкционированного доступа (НСД) к вычислительной системе 11. Последний после переполнения формирует на выходе сигнал, который через схему ИЛИ 12 и блок 13 по описанной выше схеме вводит в ОЗУ центрального процессора 3 очередную задачу защиты информации, а в блок 14 - ее эталонное решение. Этой процедурой достигается следующая цель: неудачные попытки взломщика негласно фиксируются и после достижения их некоторого заданного значения, определяемого емкостью счетчика 11, задача защиты заменяется, создавая тем самым у взломщика иллюзию благополучного преодоления преграды. При этом выбор емкости счетчика 11 носит тактический характер. Например, при большой емкости счетчика 11 переход на последующую программу защиты может и не происходить.

Наряду с описанным вычислительным процессом в вычислительной системе выполняется другой вычислительный процесс. Метки времени, формируемые формирователем временных меток 25, поступают, например, на высокоприоритетный разряд регистра прерывания центрального процессора 3, после чего он переходит к реализации программы дежурного модуля (ДМ), которая была введена в ОЗУ центрального процессора 3 при поступлении импульса по входу 29 на второй вход второй схемы И 18. Эти метки могут формироваться и другим образом (например, программными средствами). Цель этой процедуры - периодически (например, с частотой 50 мс) отвлекать вычислительные ресурсы системы от решения задач защиты информации. Программа дежурного модуля может быть построена на реализации различных функций. Например: "1x1", "Sin x", "lg x" и т.д. Счетчик циклов ДМ 24 подсчитывает количество раз его задействования после каждой метки времени, а второй блок сравнения 23 сравнивает это количество с заданным, записанным в задатчике количеством циклов 22. Перед началом работы систем в этом задатчике находится малое значение (например, 1 или 2). Следовательно, через каждые 50 мс ДМ будет задействоваться 1 или 2 раза (например, 1х1), практически не снижая быстродействия вычислительной системы. При приходе сигнала "Нет" с первого выхода блока сравнения 10 на вход формирователя количества циклов ДМ 19 в нем происходит формирование нового заданного значения количества циклов ДМN. Алгоритм его формирования может быть различен. Например: N = 4i (где i - количество раз прихода "Нет"). Через некоторое время, определяемое блоком задержки 21, на второй вход схемы И 20 приходит задержанный импульс и значение вычисленного количества циклов из блока 19 записывается в задатчик циклов 22. Теперь количество раз задействования дежурного модуля после каждой метки от формирователя меток 25 увеличится. Например, при количестве неудачных попыток i=5, после каждой временной метки ДМ будет задействоваться 1024 раза. Если время срабатывания ДМ будет составлять, например, 10 мкс, то теперь на интервале времени 50 мс ДМ будет занимать ≅ 10 мс, а при i=6 - порядка 30 мс. При этом располагаемое время для решения других задач уменьшается (в предельном случае центральный процессор 3 будет "крутить" только ДМ). И если нарушитель даже выйдет на основную программу 28, которая может быть введена в центральный процессор 3 только после последовательного ввода всех программ защиты 26n, то с располагаемой производительностью центрального процессора 3 он не сможет реализовать циклограммы пуска ракет.

Таким образом, предлагается многопреградная защита вычислительной системы от несанкционированного доступа, требующая обширной эрудиции взламывающей стороны, которой может не обладать террорист. При этом правильные решения задач защиты могут находиться в области иррационального мышления с возможным созданием иллюзии правильности действий взламывающей стороны. При правильных же действиях оператор быстро выходит на штатную эксплуатационную программу ВС без потерь ее вычислительных ресурсов. Вследствие этого повышается эффективность защиты ВС (например, ракетного комплекса) от несанкционированного доступа.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПУСКОМ РАКЕТ | 1998 |

|

RU2151359C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРИМЕНЕНИЕМ ЛЕТАТЕЛЬНЫХ АППАРАТОВ | 2002 |

|

RU2221208C2 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| ПРОЦЕССОР | 1990 |

|

SU1826787A1 |

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ | 1991 |

|

RU2006931C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОСЕВОГО ПЕРЕМЕЩЕНИЯ ВАЛА | 1996 |

|

RU2129212C1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА ДЛЯ КОМПЬЮТЕРОВ ИНФОРМАЦИОННО-ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ | 2006 |

|

RU2321055C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФАЗЫ СИГНАЛА | 1986 |

|

SU1433210A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРИМЕНЕНИЕМ ЛЕТАТЕЛЬНЫХ АППАРАТОВ | 2003 |

|

RU2241948C1 |

| СПОСОБ ЗАЩИТЫ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА К СРЕДСТВАМ ОБРАБОТКИ ИНФОРМАЦИИ, РАСПОЛОЖЕННЫМ НА ОХРАНЯЕМОЙ ТЕРРИТОРИИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2180453C1 |

Изобретение относится к области техники, занимающейся разработкой вычислительно-управляющих систем объектов различного назначения. Техническим результатом является повышение эффективности системы защиты вычислительного комплекса от несанкционированного доступа, который достигается путем выявления и фиксации попыток несанкционированного доступа и передачи части вычислительных ресурсов высокоприоритетному программному модулю на время, адекватное количеству несанкционированных попыток. 1 ил.

Устройство для защиты вычислительной системы от несанкционированного доступа, содержащее первый блок памяти с информацией о защите, второй блок памяти с ключом к шифру, центральный процессор, блок ввода и отображения информации, включающий в себя блок набора данных, подключенный через первую схему И к первому входу центрального процессора, блок отображения, соединенный с первым выходом центрального процессора, блок разрешения ввода, подключенный к второму входу первой схемы И, отличающееся тем, что в него введены последовательно соединенные блок хранения результатов текущих решений, вход которого соединен с вторым выходом центрального процессора, первый блок сравнения, счетчик количеств попыток несанкционированного доступа, схема ИЛИ, блок управления памятью, первый и второй входы которого соединены соответственно с выходами первого и второго блоков памяти, первый выход - с вторым входом центрального процессора, а второй выход - с входом блока хранения результатов эталонных решений, выход которого соединен с вторым входом первого блока сравнения, последовательно соединенные формирователь импульсов и счетчик импульсов, второй вход которого соединен с выходом блока разрешения ввода, а выход - с третьим входом первого блока сравнения, третий блок памяти с программой дежурного модуля, соединенный через вторую схему И с третьим входом центрального процессора, последовательно соединенные формирователь количеств циклов, третья схема И, к второму входу которой подключен блок задержки, задатчик циклов и второй блок сравнения, выход которого соединен с четвертым входом центрального процессора, счетчик циклов, вход которого соединен с третьим выходом центрального процессора, а выход - с вторым входом второго блока сравнения, формирователь временных меток, соединенный с пятым входом центрального процессора, при этом входы блока задержки и формирователя количества циклов соединены с первым выходом первого блока сравнения, а его второй выход - c вторым входом схемы ИЛИ, к третьему входу которой и второму входу второй схемы И подключен формирователь сигнала на запуск устройства, в первом блоке памяти последовательно размещены по заданным адресам программы защиты от несанкционированного доступа и эксплуатационная программа вычислительной системы, а во втором блоке памяти ключом является размещенная в нем последовательность соответствующих эталонных решений программ защиты.

| Устройство для дистанционного измерения параметров | 1971 |

|

SU449256A1 |

| US 5339427 A, 16.08.94 | |||

| US 5289540 A, 22.02.94 | |||

| US 5384900 A, 24.01.95 | |||

| US 94020949 A1, 27.02.96 | |||

| RU 94031439 A1, 20.06.96. | |||

Авторы

Даты

1999-09-27—Публикация

1997-12-25—Подача